Преобразователь “аналог-код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

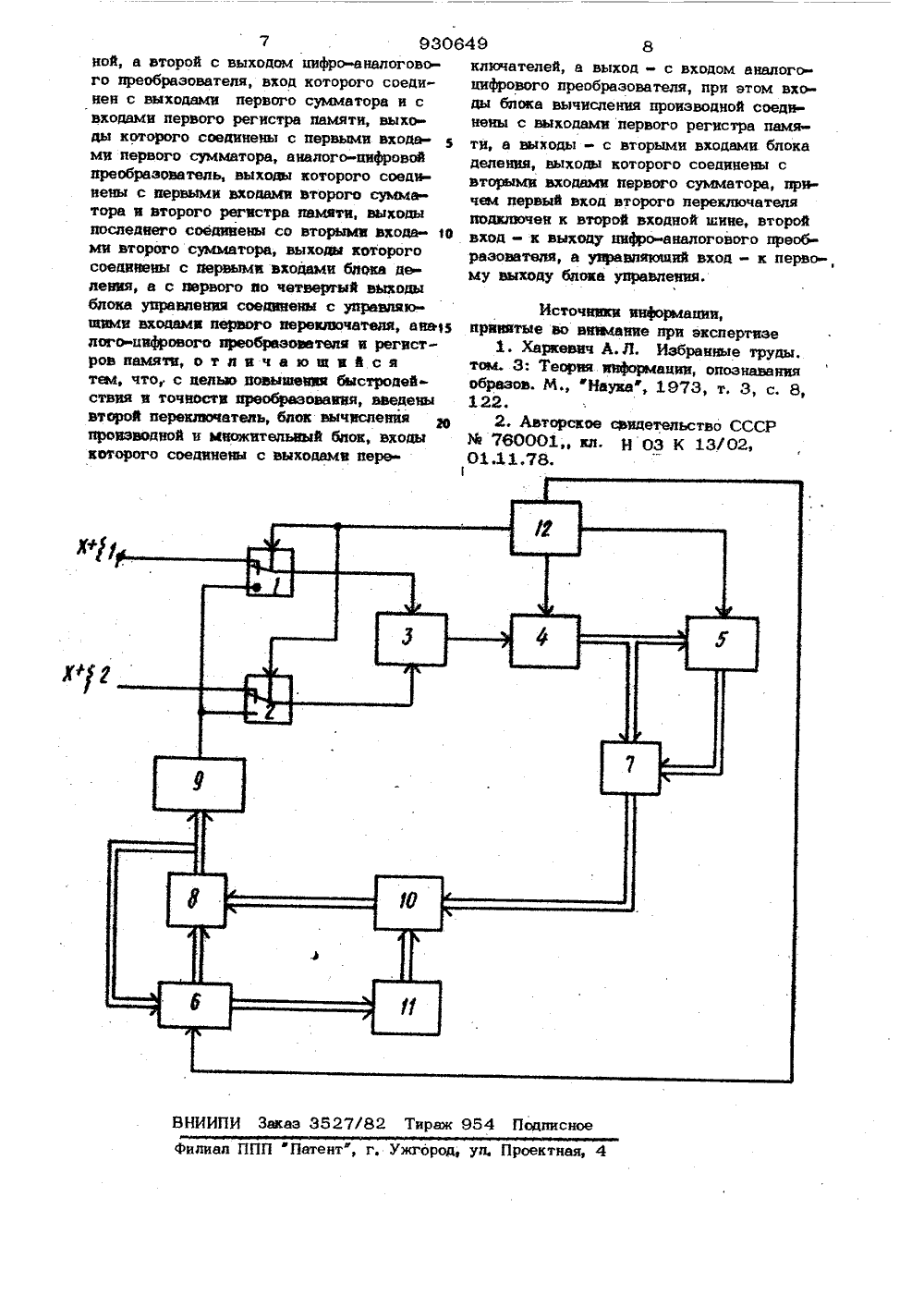

) иекорреам х а таке иокоррелвВх О веъ 3 2Изобретение относится к ииформациоаТ., Тно-измерительной технике и может найти фф Ий й(уа у),у-применение в системах централизованно, ТЯ У 1 г " Уд 1 ф Фф Мго контроля, имеющих протяжные ламии: ф Т т ООсвязи, хсесрые хсяееРкеа веаЮсевдяф ИЮз-М ЬЖ И Чдз Ипомех.Известны методы выделения полезнаго сигнала, следующего на 4 оие помех : Вкф +Ьи Ф ЬОдин иэ таких методов корреляционный, . ФФ Ф%заключается в следуаацем. ИзмеряемаТак как помех , (Ф) и (аналоговая величина Ф цодводитс к идф" З 3 кааиы с ицлезаумс иолезаям сигналмерительному устройству цо двум Ра . Же ма иду абойто их вэаимкабелям связи, на которые соответствеи" цноииые функции ВО,но наводятся помехи с случайными амана и ВОтудамин . Далеее аддитивиаясмесь сигнала н шума Х +(Ф) и . Вйходиай код АЦПИ, как ето следуетМ+ ф, (Ь) поступает на входы пред-,из (1), окажется процорцнощщьным квадвключенного множительного устройства рату входной величины хПолученное на выходе множительного уса- ч К хф . (2).ройства произведение поступает затем на Коэффициент пропорциональности К длявход интегрирующего аналого-циФРового всех суаествукхцих АцП, как правило, бепреобразователя (АЦП). Через соот ретск рюайм единице. Поэтому резулыствующий интервал усреднения Т а вы- тат измерения находят как Х щ Я, т. е,ходе АЦП образуется код измерительное устройство оснащают цнфро 3 93064 вым блоком извлечения квадратного корня.Итак, известный преобразователь содержит последовательно включенные множительный блок, интегрирующий АЦП и блок извлечения квадратного корня Ц,Недостатком этого устройства является то обстоятельство, что погрешности всех упомянутых блоков оказывают непосредственное влияние на точность преобра- щ зования. Другой недостаток устройства состоит в необходимости извлечения квадратного корня, процедура которого, как известно, является достаточно трудоемкой и длительной, а результат приблн- д женным.Известно устройство содержащее переключатель, входы .которого соединены с входной шиной устройства и выходом ЦАП, а выход - с входом АЦП, выход которо- щ го непосредственно и через регистр памяти соединен с входами первого сумматора, выход которого соединен с входами множительиого и делитепьного блоков. Другой вход последнего соединен с выходом второго сумматора, а выход - с дру- . гим входом множительного блока, выход которого соединен с входом третьего сумматора, выход которого соединен с входами ЦАП и второго регистра памяти, вы- зо ход которого соединен с другим входом третьего сумматора, входамн второго сумматора и третьего регистра памяти, выход последнего соединен с другим входом второго сумматора, а выходы блока упраь лений соединены с управляющими входами переключателя, АЦП, делительного блока И трех регистров памятнаСкорость сходимости итераций, то естьбыстродействие известного устройства,оценивается следующим образом.1 п- ю =% 1 и- -у , (3)4,И 9 где Х- цифровой эквивалент истинного (без погрешностей)значения входной величины х,и ,2.пкоды, полученные в результате проведения соответственно и -1 и и ите орацИй;т,Ч-р - разность, характеризующаявеличину абсолютной погрешности измерения накаждой итерации 2.Таким образом, с одной стороны имееп ся преобразователь, обеспечивающий хорошее подавление помех случайной приро-. На чертеже представлена блок-схема преобразователя аналог-код, содержащего переключатели 1 и 2, множительный блок 3, интегрирукяций аналого-цифровой преобразователь (АЦП) 4, регистры памяти 5 и 6, сумматоры 7 и 8, цифро-аналоговый2 Тираж 954 Подписное 3 ИИПИ жгород, ул, Проектная,пиал ППП Патент 7 9306 ной, е второй с выходом инфро-аналогового преобразователя, вход которого соединен с выходами первого сумматора н с входами первого регистра памяти, выходы которого соединены с первыми входами первого сумматора, аналого-цифровой преобразователь, выходы которого соединены с первымн входами второго сумматора и второго регистра памяти, выходы последнего соединены со вторыми входа е ми второго сумматора, выходы которого соединены с первыми входами блока деления, а с первого по четвертый выходы блока управления соединены с управляющими входами первого переключателя, анаи лаго-цифрового преобразователя и регистров памяти, о т л и ч а ю щ и й с я тею, чтос келью повыщении быстродействия и точности преобразования, введены второй переключатель, блок вычисления производной и множительный блок, входы которого соединены с выходами пере 8ключателей, а выход с входом аналогоцифрового преобразователя, при этом входы блока вычисления производной соединены с выходами первого регистра памяти, а выходы - с вторыми входами блока деления, выходы которого соединены с вторыми входами первого сумметора, причем первый вход второго переключателя подключен к второй входной вине, второй вход - к выходу пифро-аналогового преобразователя, а управляющий вход - к первому выходу блока управления. Источники информации,принятые во внваанне при экспертизе1. Харкевич А.Л. Избранные труды,том. 3: Теория информации, опознаванияобразов. М., фйаукаф, 1973) т. 3, с. 8,122.2, Авторское свидетельство СССРф 780001 кл, Я 03 К 13/0201.1 1.78.

СмотретьЗаявка

2924695, 21.07.1980

АЗЕРБАЙДЖАНСКИЙ ИНСТИТУТ НЕФТИ И ХИМИИ ИМ. М. АЗИЗБЕКОВА

АЛИЕВ ТОФИК МАМЕДОВИЧ, ШЕКИХАНОВ АЙДЫН МАХМУДОВИЧ, ДАМИРОВ ДЖАНГИР ИСРАФИЛ ОГЛЫ

МПК / Метки

МПК: H03K 13/02

Метки: «аналог-код»

Опубликовано: 23.05.1982

Код ссылки

<a href="https://patents.su/4-930649-preobrazovatel-analog-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь “аналог-код</a>

Предыдущий патент: Преобразователь “код-ток

Следующий патент: Следящий аналого-цифровой преобразователь

Случайный патент: Амортизационное устройство к втулке несущего винта вертолета