Сумматор по модулю три

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 890393

Авторы: Ташлинский, Шнайдер

Текст

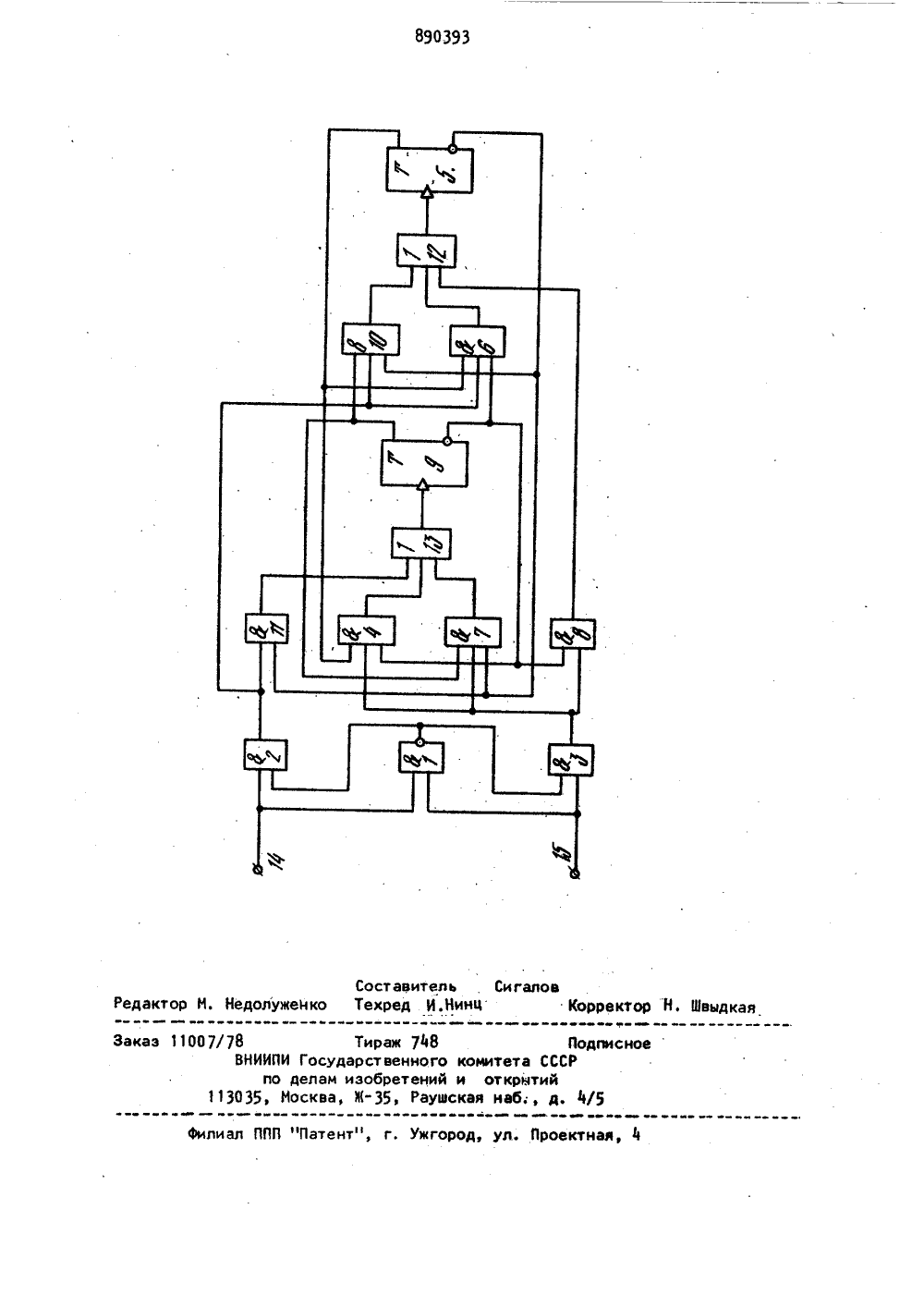

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик п 890393/ с присоединением заявки Ж -3 Ьеудеротекнный комитет СССР до делам изобретений и открытий(088. 8) Дата опубликования описания 151231.,ф.ф. Янайдер и А.Г. Та линский4(5 Й) СУММАТОР ПО МОДУЛЮ ТРИ Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля,Известен сумматор по модулю три, содержащий три установочных триггера с элементами управления в каждом плече триггера на элементах И-НЕ 111.Недостатком его является низкое быстродейст вие. Наиболее близким техническим реше О нием к изобретению является сумматор по модулю три, содержащий схемы совпадениядва триггера и две схемы ИЛИ, выходами подключенные ко входам триггеров, первый вход первой схемы совпадения совместно с первым входом второй схемы совпадения, а второй вход- совместно с первым входом третьей схемы совпадения являются входами сумматора по модулю три, а вторые входы вто рой и третьей схемы совпадения подключены к входу первой схемы совпадения 21. 2Недостатком известного устройства является низкое быстродействие, обусловленное наличием линии задержки.Цель изобретения - увеличение быстродействия сумматора.Поставленная цель достигается тем, что в сумматор по модулю три, содержащий первый и второй триггеры, первый и второй элементы ИЛИ, первый, второй и третий элементы И, причем первый вход сумматора соединен с первым входом первого и второго элементов И, второй вход сумматора соединен с первым входом третьего элемента И и вто-. рым входом первого элемента И, инверсный выход которого соединен со вторыми входами второго и третьего элементов И, выходы первого и второго элементов ИЛИ соединены соответственно . со счетными входами первого и второго триггеров, введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем. прямой выход первого триггера соединен с первыми вхо0393 10 15 35 40 45 5,0 55 3 89 дами четвертого и пятого элементов И, , выходы которых соединены соот вет ст венно с первыми входами второго и йрво го элементов ИЛИ, выход третьего элемента И соединен с первыми входами шестого и седьмого элементов И и со вторым входом четвертого элемента И, выход второго элемента И соединен с первыми входами восьмого и девятого элементов И и вторым входом пятого элемента И, инверсный выход первого триггера соединен со вторыми входами шестого элемента И, восьмого элемента И и девятого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, инверсный выход второго триггера соединен с третьими входами четвертого и пятого элементов И и вто. рым входом седьмого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, прямой выход второго триггера соединен с третьими входами шестого элемента И и восьмого элемента И, выход которого соединен с третьим входом первого элемента И, выход шестого элемента И соединен с третьим входом второго элемента ИЛИ.На чертеже представлена функциональнаяф схема сумматора по модулю три.Схема содержит первый, второй, третий и четвертый элементы И соответственно 1-4. Первый триггер 5, пятый, шестой и седьмой элементы И со ответственно 6-8, второй триггер 9, восьмой и девятый элементыИ соответственно 10 и 11, первый и второй элементы ИЛИ соответственно 12 и 13, входы 14 и 15 сумматора, Первый вход 14 сумматора совместно с первым входом второго элемента И 2, а второй вход15 совместно с первым входом третьего элемента И 3 являются входами сумматора по модулю три, а вторые входывторого и третьего элементов И 2 и 3подключены к выходу первого элементаИ 1. Первый вход третьего элементаИ 4 соединен с выходом триггера 5 и третьим входом пятого элемента И 6, второй вход четвертого элемента И 4- с первыми входами шестого и седьмогоэлементов И 7 и 8 и выходом третьего элемента И 3., третий вход четвертого элемента И 4 - с третьим входом пятого элемента И 6 вторым входом седьмого элемента И 8 и инверсным выходом второго триггера 9. Третьи входы шестого элемента И 7 и восьмого элемента И 10 соединены с выходом триггера 9, вторые входы шестого элемента И 7 со вторыми входами восьмого и девятого элементов 11 и инверсным выходомпервого триггера 5, Выход второго элемента И 2 подключен к первому входудевятого элемента И 11, к первому входу восьмого элемента И 10 и второму входу элемента И 6, Выходы элементов И 6, 8 и 10 подключены ко входам первого элемента ИЛИ 12, выход которого подключен ко входу триггера 5, а выходы элементов И 4, 7 и 11 подключены ко входам второго элемента ИЛИ 12,выход которого подключен ко входутриггера 9. Сумматор по модулю три работаетследующим образом Контролируемый двоичный код поступает параллельно на вХоды 14 и 15. Пусть на вход 14 поступает нечетный о разряд двоичного кода, на вход 15 четный. В этом случае во втором триггере 9 хранится младший разряд остат-ка, в триггере 5 - старший. В процессе работы на входы 14 и 15 могут пода 25,ваться коды "00", "01", "10", "11",а в сумматоре может храниться оста"00" и "11" образуют на выходах схемысовпадения 2 и 3 логический "0" и изменений состояния три ггеров 5 и 9 невызывают. Входные коды "01" и "10" изменяют код остатка сумматора, и работа сумматора в этом. случае зависит отсостояния триггеров 5 и 9. При нулевом состоянии триггеров 5и 9 логические "0" с их прямых выходом блокируют элементы И 4, 6, 7 и 10,При этом входной код "01" образует навыходе третьего элемента И 3 логический "0", блокирующий элемент И 8, ана выходе элемента И 2 логическую "1",сигнал которой проходит через элемент И 11 и ИЛИ 13 на вход триггера9 и устанавливает его в единичноесостояние, Таким образом, в сумматореустанавливается код "01". Входной код"10" при нулевом состоянии триггеров5 и 9 образуют на выходе элемента И2 логический "0", блокирующий эле"мент И 11, а на выходе элемента И 3ло ги че скую "1", си гнал которой проходит через элемент И 8 и ИЛИ 12 навход триггера 5 и устанавливает егов единичное состояние, т,е, в сумматоре устанавливается код "10",При остатке в сумматоре "01" логический "0" с прямого выхода триггера5 и инверсного выхода триггера 9 бло5 890 кирует элементы И 4, 6 и 8. Логичес" кий "0" с выхода элемента И 3 при входном коде "01" блокирует элемент И 7, а сигнал логической "1" поступает с выхода элемента И 2 через элемент И 11 и ИЛИ 13 на триггер 9 и через схемы элемента 10 и ИЛИ 12 на триггер 5, уст анавли вая их соот ветст венно в нулевое и единичное состояние. Таким образом, в сумматоре устанавливается код "10", Логический "0" с выхода элемента И 2 при входном коде "10", а остатке в сумматоре "01" блокирует элементы И 10 и 11, а сигнал логической "1" посту пает с выхода элемент а И 3 через элемент И .7 и ИЛИ 13 на триггер 5, устанавливая его в нулевое состояние. В сумматоре устанавли вается код "00" без установки промежуточного кода "11", т,е. за один такт работы триггеров.При остатке в сумматоре "10" логический "0" с прямого выхода триггера 9 и инверсного выхода триггера 5, блокирует элементы И 7, 1 О и 11. Логический "0". с выхода элемента И 3, входного кода "01", блокирует элементы И 4 и 8, а сигнал логической "1" поступает с выхода элемента И 2 через элементы И 6 и ИЛИ 12 на триггер 5, устанавливая его в нулевое состояние, т.е. в сумматоре устанавливается код "00", как и в предыдущем случае, без установки промежуточного кода "11". Логический "0" с выхода элемента И 2 входного кода "10" и при остатке в сумматоре н 10", блокирует элемент И 6, а сигнал логической единицы поступает с выхода элемента И 3 через элементы И 4 и ИЛИ 13 на триггер 9 и через элементы И 8 и ИЛИ 12 на триг гер 5, устанавливая их сочтцетственно в единичное и нулевое состояния, т;е. в сумматоре уст ана вли вает ся код "10".Благодаря тому, цто сумматор во всех случаях вычисляет остаток от деления двоичного хода на три за один такт, он обладает примерно в двое большим быстродействием по сравнению с известным. второй элементы ИЛИ, первый, второйи третий элементы И, причем первыйвход сумматора сОединен с первымивходами первого и второго элементовИ, второй вход сумматора соединен спервым входом третьего элемента И ивторым входом первого элемента И,инверсный выход которого соединен совторыми входами второго и третьего р элементов И, выходы первого и второго элементов ИЛИ соединены соответственно со счетными входами первогои второго триггеров, о т л и ч а ющ и й с я тем, что, с целью увеличения быстродейст вия, в сумматор введены четвертый, пятый, шестой, седьмой,восьмой и девятый элементы И, причемпрямой выход первого триггера соединен с первыми входами четвертого ипятого элементов И, выходы которых соединены соот вет ст венно с пер выми входами второго и первого элементов ИЛИ,выход третьего элемента И соединенс первыми входами шестого и седьмоо го элементов И и со вторым входомчетвертого элемента И, выход второгоэлемента И соединен с первыми входами восьмого и девятого элементов И ивторым входом пятого элемента И, инверсный выход первого триггера соединен со вторыми входами шестого элемента И, восьмого элемента И и девятого элемента И, выход которого соединенсо вторым входом второго элемента ИЛИ,инверсный выход второго триггера сое- Идинен с третьими входами четвертогои пятого элементов И и вторым входомседьмого элемента И, выход которогосоединен со вторым входом первого 40элемента ИЛИ, прямой выход второготриггера соединен с третьими входамишестого элемента И и восьмого элемента И, выход которого соединен с третьим входом первого элемента И, выходшестого элемента И соединен с третьимвходом второго элемента ИЛИ. формула и зобрет енияСумматор по модулю три, содержащий первый и второй триггеры, первый и Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР И 604155, кп. Н 03 К 23/02, 1976. 2. Авторское свидетельство СССР й 541175, кл. С 06 Г 11/00, 1978 (про-отип)./78 ТиражВНИИРИ Государствпо делам иэобр13035, Москва, Ж748ного комиений иРаущская Подписиета СССРкритийаб;, д. 4/5

СмотретьЗаявка

2887551, 26.02.1980

Заявитель

ШНАЙДЕР ФЕДОР ФРИДРИХОВИЧ, ТАШЛИНСКИЙ АЛЕКСАНДР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 7/72

Опубликовано: 15.12.1981

Код ссылки

<a href="https://patents.su/4-890393-summator-po-modulyu-tri.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю три</a>

Предыдущий патент: Частотное делительное устройство

Следующий патент: Блок приоритета

Случайный патент: Фильера для формирования полой нити