Устройство для умножения чиселв дополнительных кодах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 822181

Авторы: Ледянкин, Малиновский

Текст

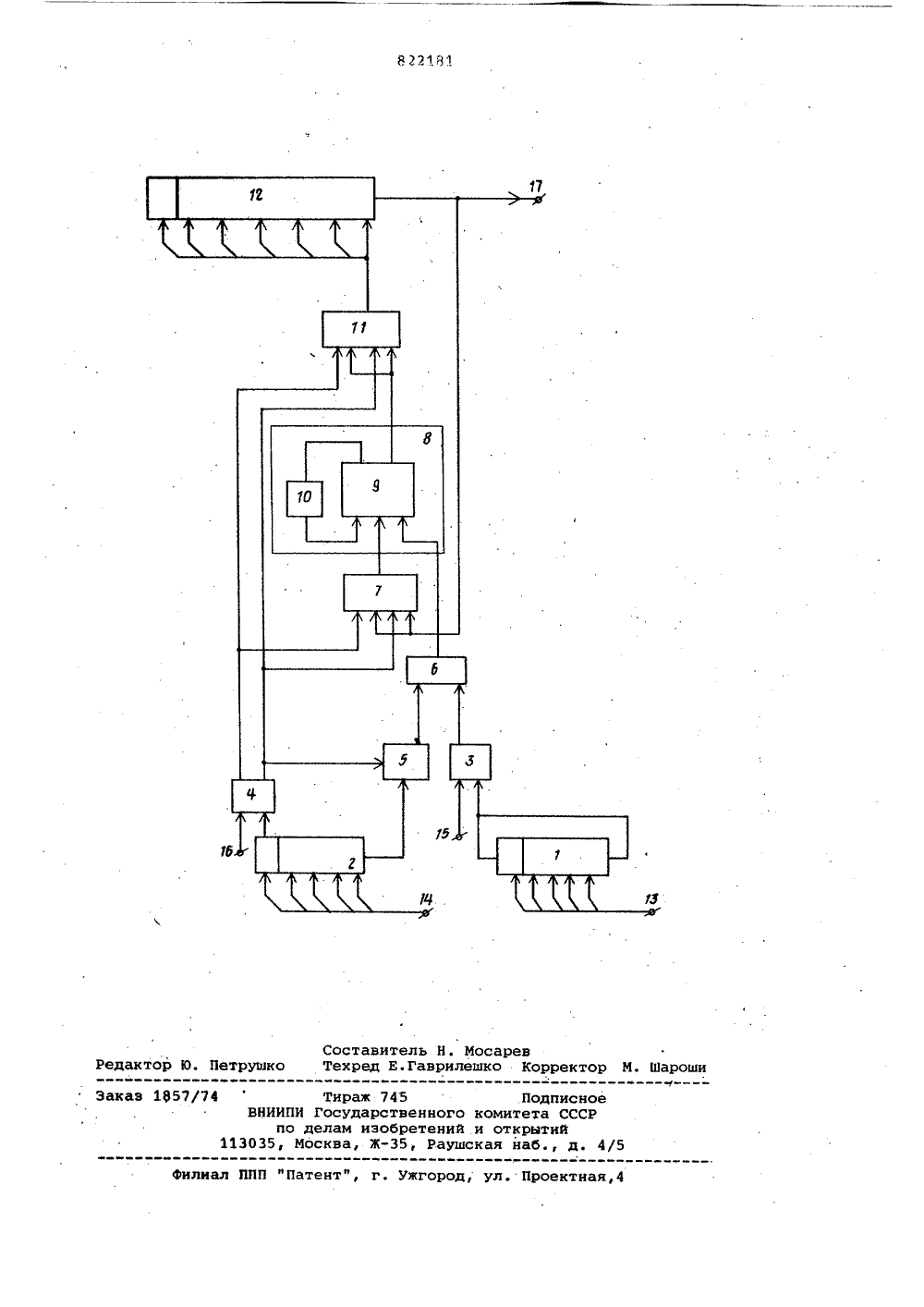

Сфез Советских Социалистических РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ п 822181(51) М. Кл.з с присоединением заявки Йф 6 06 Г 7/52 Государствеииый комитет СССР по делаю изобретений и открытий(72) Авторы изобретения Ю.Я, Ледянкин и Б.Н, Малиновский на Ленина институт кибернетикиАН Украинской ССР АСМОЯДА(71) Заявитель 54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕ В ДОПОЛНИТЕЛЬНЫХ КОДАХ стваервым тение относитс ехнике и может арифметических ых цифровых .вы е Изобре я к вычисли- тельной т. быть исполь-зовано в устройствах специальн числительныхмашин.Известно устройство последовательного типа для,умножения двоичных чисел, содержащее регистр множкмого, множителя и частичного произведения, элементы И и инвертор. Это устройство позволяет выполнять умножение двоичных чисел в дополнительных кодах.Недостатком такого устройства является невысокое быстродействие., связанное с необходимостью выполнения корректирующих циклов суммирования для учета умножения множимого на знак множителя. Особенно значительно происходит понижение быстродействия при небольшой разрядности многи теляНаиболее близким к предлагаемому по техническому решению является устройство последовательного типа для умножения двоичных чисел, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединены с входными шинами множи мого и множителя устрой соот ветственно а выходы с и и вторым входами элемента И, выход регистра множимого соединен также со входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результа та, выход регистра результата соединен со вторым входом узла суммирования и с выходной шиной результата устройства. Данное устройство позволяет выполнять умножение двоичных чисел как в прямых, так и в дополнительных кодах без специальной коррекции результата за счет расширения разрядной сетки сомножителей.Недостатком известного устройства является также невысокое быстродействие при выполнении умножения двоичных чисел в дополнительных кодах, связанное с расширением разрядной сетки сомножителей,которое увеличивает общее число циклов суммирования.Цель изобретения - увеличени быстродействия устройства.Для достижения поставленной цели в устройство для умножения чисел в дополнительных кодах, содержащеерегистр множимого, регистр множителя,регистр результата, узел суммирования,элемент И, причем входы регистровмножимого и множителя соединены совходными шинами множимого и множителя устройства. соответственно, выходрегистра множимого соединен со входом:этого регистра, выход элемента Исоединен с первым входом узла суммирования, выход регистра результатасоединен с выходной шиной результатаустройства, введены триггер знака,триггер модификации сдвига, преобразователь кода множителя в дополнительный код, входной и выходной коммутаторы, причем вцход регистра множимого соединен с информационным входом,триггера модификации сдвига,управляющий вход этого триггера соединен с первым управляющим входомустройства, выход регистра множителясоединен с информационным входом преобразователя кода множителя в дополнительный код, выход знакового разряда регистра множителя соединен синформационным входом триггера знака, управляющий вход которого соединен со вторым управляющим входомустройства, выходы триггера модификации сдвига и преобразователя кодамножителя в дополнительный код соединены с первым и вторым входами элемента И соответственно, прямой выход триггера знака соединен с первымиуправляющими входами входного и выходного коммутаторов и с управляющимвходом преобразователя кода множителяв дополнительный код, инверсный выход З 5триггера знака соединен со вторымиуправляющими входами входного и выходного коммутаторов, прямой и инверсный информационные входы входногокоммутатора соединены с выходом регистра результата, а выход этого коммутатора - со вторым входом узласуммирования, прямой и инверсный информационные входы выходного коммутатора соединены с выходом узла суммирования, а выход - со входом регистра результата,Схема устройства представлена начертеже.Устройство содержит регистр 1 множимого,регистр 2 множителя, триггер 3модификации сдвига, триггер 4 знака, преобразователь 5 кода множителяв дополнительный код, элемент И б,входной коммутатор 7, узел 8 суммирования, содержащий одноразрядныйсумматор 9 и элемент 10 задержки,выходной коммутатор 11, регистр 12результата, входные шины 13 и 14 множимого и множителя, первый и второйуправляющие входы 15 и 1 б устройства 60выходную шину 17 результата.При работе устройства в регистрымножимого 1 и множителя 2 по входнымшинам записызаются коды сомножителей.В зависимости от знака кода множителя 65(+ - ).30б 4ч.п. 0,101 т,к.ч.п. 0,101 о.к.ч.п.множимоео.к,ч.п.п,к.ч.п. в регистре 2 триггер 4 знака множителя устанавливается в единичноеили нулевое состояние. Если знакмножителя положительный, то прохождение кода множителя через преобразователь 5 кода осуществляется без преобразования, т.е. в коде представления (прямом); если же знак отрицательный - берется дополнительный кодот дополнительного кода отрицательного числа, т.е. множитель преобразуется в абсолютную величину. Таким образом, код множителя всегдаделается положительным. Триггер 4зиака своими выходами управляетвходным и,выходным коммутаторамитак, что информация подается с выхода регистра,12 на вход узла 8суммирования через входной коммутатор, и с выхода узла 8 суммирования на вход регистра 12 результата(через выходной коммутатор 11) впрямом коде, если знак множителяположительный, или в обратном, еслизнак отрицательный. В то же времямножимое всегда поступает в узел8 суммирования непосредственно вкоде представления без преобразований, После передачи знакового разряда множимого на выход регистра1 он будет зафиксирован триггером3 модификации сдвига, который в течение последующих микротактов небудет сбрасываться, и в узел 8суммирования, в соответствии справилом модифицированного сдвигачисла будет подаваться код знакового разряда множимого.Знак множителя определяет необходимые сложения или вычитания промежуточного результата (частичногопроизведения) с кодом множимого.При этом реализуется алгоритмвычитания чисел, представленных дополнительным кодом, в соответствиис которым необходимо проинвертировать код уменьшаемого (в данномслучае код результата), сложитьего с кодом вычитаемого (в данномслучае с кодом множимого),а полученный псевдорезультат операциисложения вновь проинвертировать,после чего на выходе (после выходного коммутатора) получаетсяразность исходных чисел,Приме р.3) 0,011000 п.к,ч.п. 0,101множитель4) 0,011000 - т,к.ч,п, 0,101множитель1,100111 - о.к.п.ч.,1,111010 - множимое1,100001 - псевдорезультат.1,011110 - результат = (+ - 4)30 64где ч,п. - частичное произведение; о.к. - обратный код; п.к. - прямой код.В приведенном примере реализуется умножение, начиная со старших разрядов множителя со сдвигом множимого вправо и с неподвижным частичным произведением. Возможна реализация умножения, начиная с младших разрядов множителя.Таким образом, устройство позволяет выполнять операцию умножения двоичных чисел в дополнительных кодах без коррекции с интерпретацией знаковых разрядов как числовых.Введение двух дополнительных триггеров, преобразователя кода множителя и двух коммутаторов позволяет вдвое сократить число циклов суммирования, при выполнении операций умножения чисел в дополнительных кодах без коррекции, так как отпадает необходимость расширения разрядной сетки сомножителей.Это приводит к увеличению быстродействия предлагаемого устройства в 1,7-1,8 раз по сравнению с известным. Предлагаемое устройство позволяет та(же совместить устройство для сложения (вычитания) чисел в дополнительных кодах с устройством умножения (деления) аналогичных чисел.Формула изобретенияУстройство для умножения чисел вдополнительных кодах, содержащеерегистр множимого, регистр множителя,регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединенысо входными шинами множимого и множителя устройства соответственно,выход регистра множимого соединен совходом этого регистра, выход элемента И соединен с первым входом узласуьеюирования, выход регистра результата соединен с выходной шиной результата устройства, о т л и ч а ю щ ее с я тем, что, с целью увеличениябыстродействия, в устройство введенытриггер знака, триггер модификациисдвига, преобразователь кода множителя в дополнительный код, входной ивыходной коммутаторы, причем выходрегистра множимого соединен с информационным входом триггера модификации сдвига, управляющий вход этого триггера соединен с первым управ. ляющим входом устройства, выходрегистра множителя соединен с информационным входом преобразователякода множителя в дополнительный код,выход знакового разряда регистрамножителя соединен с информационнымвходом триггера знака, управляющийвход которого соединен со вторым управляющим входом устройства, выходытриггера модификации сдвига и преобразователя кода множителя в дополнительный. код соединены с первым ивторым входами элемента И соответственно, прямой выход триггера знака соединен с первыми управляющимивходами входного и выходного коммутатора и с управляющим входомпреобразователя кода множителя вдополнительный код, инверсный выходтриггера знака соединен со вторымиуправляющими входами входного и 40 выходного коммутаторов, прямой иинверсный информационные входывходного коммутатора соединены свыходом регистра результата, а выходэтого коммутатора - со вторым входом 45 узла суммирования, прямой и инверсный информационные входы выходногокоммутатора соединены с выходом узласуммирования, а выход - со входомРедактор Ю. Заказ 1957/ Составитель Н. Мосареветрушко Техред Е,Гаврилешко Корректор И. ШарошчТираж 745 Подписное ВНИИПИ ГосУдарственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Раушская наб., д. 4

СмотретьЗаявка

2660932, 21.08.1978

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИАН УКРАИНСКОЙ CCP

ЛЕДЯНКИН ЮРИЙ ЯКОВЛЕВИЧ, МАЛИНОВСКИЙ БОРИС НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: дополнительных, кодах, умножения, чиселв

Опубликовано: 15.04.1981

Код ссылки

<a href="https://patents.su/4-822181-ustrojjstvo-dlya-umnozheniya-chiselv-dopolnitelnykh-kodakh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чиселв дополнительных кодах</a>

Предыдущий патент: Арифметическо-логическое устройство

Следующий патент: Устройство для вычисления разностидвух -разрядных чисел

Случайный патент: Теплица