Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

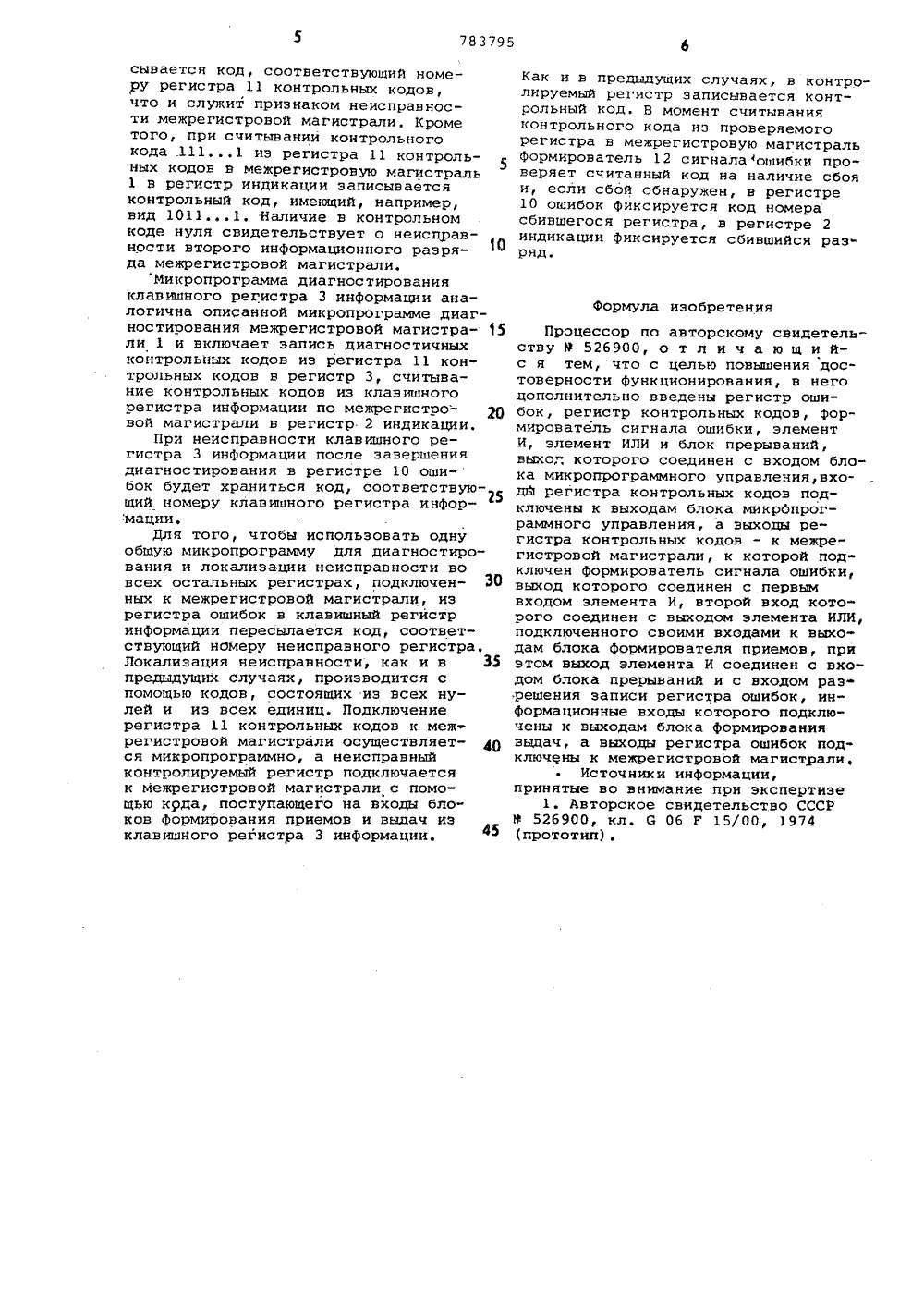

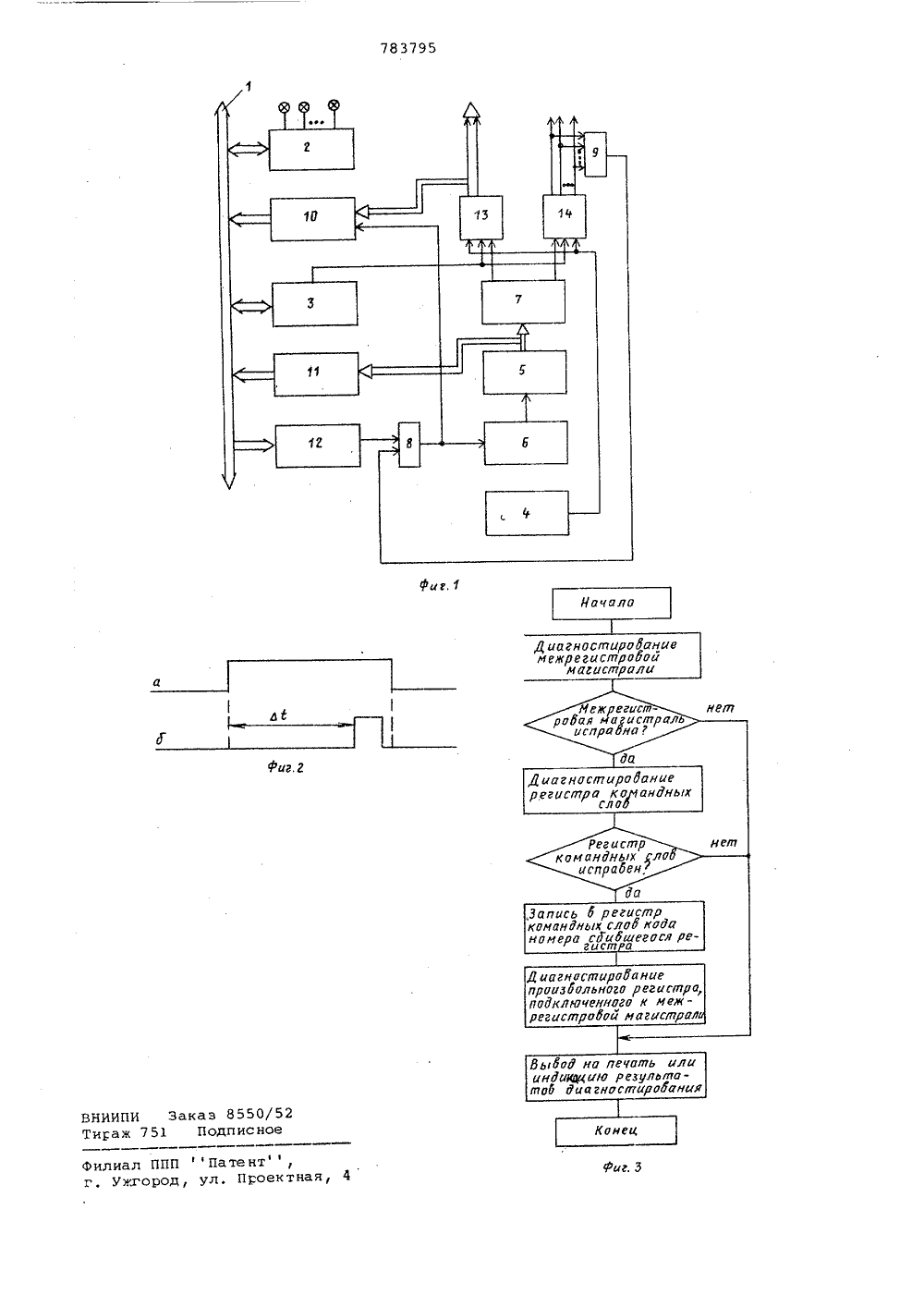

Союз Советских Социалистических РеспубликОПИСАНИЕ ИЗОБРЕТЕНИЯ пи 783795 Фс К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(23) ПриоритетОпубликовано 301180 Бюллетень Мо 44Дата опубликования описания ЗЮ 1 1,80(51)М. Кл 3 З 06 Г 15/00 Государственный комитет СССР по делам изобретений и открытий(54) ПРОЦЕССОР Устройство относится к области вычислительной техники, может быть использовано при проектировании электронных цифровых вычислительных машин и является усовершенствованием известного устройства по авт. св. Р 526900.В основном изобретении по. авт.св, Р 526900 описан процессор 1) содержащий распределитель импульсов, регистр микрокоманды, блоки формирования приемов и выдач, клавишный регистр,клавишный регистр информации, регистр адреса запоминающего устройства, регистр сигналов обмена 15 с оперативным запоминающим устройством, регистр индикации и блок регистров общего назначения. При этом все регистры подключены к межрегистровой магистрали, 20 к которой подключены блоки формирования приемов и выдач, которые соединены с регистром микрокоманд.Целью изобретения является повышение достоверности функционирова ния процессора.Для достижения указанной цели в устройство по авт. св9 526900 введены регистр ошибок, регистр конттзольных кодов, формирователь сигна ла ошибки, элемент И, элемент ИЛИи блок прерываний, выход которогосоединен с входом блока микропрограммного управления. Входы регистраконтрольных кодов подключены к выходам блока микропрограммного управления, а выходы регистра контрольныхкодов - к межрегистровой магистрали,к которой подключен формировательсигнала ошибки, выходом соединенныйс первым входом элемента И, второйвход которого связан с выходом элемента ИЛИ, подключенного своими входами к выходам блока формированияприемов. При этом выход элемента Исоединен с входом блока прерыванийи с входом разрешения записи регистра ошибок, информационные входы которого подключены к выходам блока формирования выдач, а выходы регистра ошибок подсоединены к межрегистровоймагистрали.Структурная схема процессора представлена на фиг.1,Процессор содержит межрегистровую магистраль 1, регистр 2 индикации,клавишный регистр 3 информации,распределитель 4 импульсов, блок 5 микропрограммного управления, блок 6прерываний, регистр 7 микрокоманд,.элемент И 8, элемент ИЛИ 9, регистр10 ошибок, регистр 11 контрольныхкодов, Формирователь 12 сигнала ошибки, блоки 13 и 14 Формирования выдач и приемов соответственно, которые имеют одинаковую внутреннюю структурУ и состоят, например, каждыйиз входной сборки, дешифратора, элементов памяти. В аестве Формирователя 12 сигнала ошибки может бытьприменена схема свертки информациипо некоторому модулю.Контроль за отсутствием сбоев вработе блоков процессора осуществляется в момент передачи информации помежрегистровой магистрали 1. Пусть,напрьщер, необходимо переслать инфор. 35мацию по межрегистровой магистралииз регистра 1 в регистр 3 . для этого на входы блоков формирования выдач и приемов из регистра 7 микрокоманд или из регистра 3 поступаюткодь 1, соответствующие номерам подключаемых регистров. С выхода блока 13Формирования выдач на. вход регистра.приходит сигнал, разрешающий считывание данного регистра в межрегистровую магистраль, одновременно код,соответствующий номеру регистра,пОступает на вход регистра 10 ошибок,Помагистрали 1 информация поступаетца вход регистра 3, а также в Форми-,рователь 12 сигнала ошибки. 3 И)Сигнал записи (фиг,2,б), Формируе 1 нй блоком 14 формирования приемов, запаздывает по отношению сигнала очи тывания Ифиг.2,а) ца время,Ь, дос таточное для осуществления контроля информации формирователем 12 сигнала ошибки. С соответствующего выхода блока 14 сигнал записи поступает на вход записи регистра З и через элемент ИЛИ 9 на вход элемента И 8, где осуществляет опрос сбоя информации. Если сигнал сбоя на выходе Формирователя 12 отсутствует, то это свицетельствует о том, что на вход регистра 3 поступила достоверная цн Формация, Далее осуществляется запись в регистр 3, сигнал прерывания на выходе элемента И 8 не Формируется и запись в регистр 10 ошибок не происходит, 5 ОКонтроль отсутствия сбоев при прохождении информации через входные и выходные цепи регистра ), а также отсутствие искажения информации при ее хранении и обработке в регистре 3 будет осуществлен при последующем считывании информации из этого регистраоЕсли при пересылке информации по межрегистровой магистрали формирова- бО телем 12 сигнала ошибки зафиксирован сбой, сигнал ошибки поступает на первый вход уемента И 8. С соответствующего выхода блока 14 сигнал подается ца вход регистра 3, где осуществляет:я запись информации, Одновременноэтот сигнал поступает на вход элемента ИЛИ 9 и далее на второй вход элемента И 8. С выхода элемента И 8 сигнал сбоя проходит ца вход записи регистра 10 ошибок и осуществляет запись в этот регистр кода, соответствующего номеру регистра 3., передавшего сбившуюся информацию по межрегистровой магистрали. Одновременно сигналсбоя с выхода элемента И 8 поступает в блок б прерываний, далее в блок5 микропрограммного управления ипроцессор переключателя на микропрограмму обработки сбоя.Иикропрограмма обработки сбоя начинается с диагностирования харатера ошибки Исбой или отказ), для этоо используется микропрограмма, организующая повторное выполнение команды Иили группы команд),В случае сбоя при повторном выполнении команды Иили группы омацдпроцессор переключается на тжропрограмму диагностирования и локализации неисправности, алгоритм которыйпредставлен ца Фиг.З. Эта микропрограмма включает следующие действия",диагностирование межрегистровоймагистрали на отсутствие короткогозамьиания информационньж разрядовна 0 или 1диагностирование роботоспособности регистра командных слов;диагностирование произвольногорегистра, подключенного к межрегистровой магистрали, с целью локализации неисправности;вывод на индикацию или на печатьрезультатов диагностирования.Диагностирование межрегистровоймагистрали на отсутствие короткогозамыкания в одном из пнформационцыхразрядов осуществляется путем последовательного считывания в магистраль со специального поля микрокоманды через регистр 11 коцтрольныхкодов, имеющих вид 1111 и 0000,Для опроса Формирователя 12 сигнала ошибки блок 14 Формирует сигнал записи в регистр ицдикации,Если при считывац;ли первого контрольного кода, например, состоящего из всех единиц, будет обнаруженсбой, то контрольный код, состоящийиз всех нулей, не считывается.При считывании онтрольного кодаи магистраль сигнал записи в регистриндикации производит опрос сбоя поцепи". один из выхоцов блока 14, элемент ИЛИ 9, вход элемента. И 8.Предположим, что один из разрядовмежрегистровой магистрали 1 неисправен и равен постоянно логическому0, тогда при считыватлн н магистраль контрольного ода 1111 Формирователь 12 сигнала ошибки Фиксирует сбой; По сигналу с выхода элемента И 8 в регистр 10 ошибок запи 783795сывается код, соответствующий номеру регистра 11 контрольных кодов, что и служит признаком неисправности межрегистровой магистрали. Кроме того, при считывании контрольного кода .1111 иэ регистра 11 контрольных кодов в межрегистровую магистраль5 1 в регистр индикации записывается контрольный код, имеющий, например, вид 10111. Наличие в контрольном коде нуля свидетельствует о неисправности второго информационного разряда межрегистровой магистрали.Микропрограмма диагностирования клавишного регистра 3 информации аналогична описанной микропрограмме диагностирования межрегистровой магистра ли 1 и включает запись диагностичных контрольных кодов из регистра 11 контрольных кодов в регистр 3, считывание контрольных кодов из клавишного регистра информации по межрегистро- ;щ вой магистрали в регистр 2 индикации,При неисправности клавишного регистра 3 информации после завершения диагностирования в регистре 10 оши- бок будет храниться код, соответствующий номеру клавишного регистра инфор:мации.Для того, чтобы использовать одну общую микропрограмму для диагностирования и локализации неисправности во всех остальных регистрах, подключен- ЗО ных к межрегистровой магистрали, из регистра ошибок в клавишный регистр информации пересылается код, соответствующий номеру неисправного регистра, Локализация неисправности, как и в 35 предыдущих случаях, производится с помощью кодов, состоящих иэ всех нулей и из всех единиц. Подключение регистра 11 контрольных кодов к межрегистровой магистрали осуществляется микропрограммно, а неисправный контролируемый регистр подключается к межрегистровой магистрали с помощью кода, поступающего на входы блоков формирования приемов и выдач иэ клавишного регистра 3 информации,Как и в предыдущих случаях, в контролируемый регистр записывается контрольный код. В момент считыванияконтрольного кода иэ проверяемогорегистра в межрегистровую магистральформирователь 12 сигналаошибки проверяет считанный код на наличие сбояи, если сбой обнаружен, в регистре10 ошибок фиксируется код номерасбившегося регистра, в регистре 2индикации фиксируется сбившийся раз"ряд. Формула изобретенияПроцессор по авторскому свидетельству Р 526900, о т л и ч а ю щ и йс я тем, что с целью повышения достоверности функционирования, в негодополнительно введены регистр ошибок, регистр контрольных кодов, формирователь сигнала ошибки, элементИ, элемент ИЛИ и блок прерываний,выход которого соединен с входом блока микропрограммного управления,входй регистра контрольных кодов подключены к выходам блока микрЬпрограммного управления, а выходы регистра контрольных кодов - к межрегистровой магистрали, к которой подключен формирователь сигнала ошибки,выход которого соединен с первымвходом элемента И, второй вход которого соединен с выходом элемента ИЛИ,подключенного своими входами к выходам блока формирователя приемов, приэтом выход элемента И соединен с входом блока прерываний и с входом разрешения записи регистра ошибок, информационные входы которого подключены к выходам блока формированиявыдач, а выходы регистра ошибок подключены к межрегистровой магистрали,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 52 б 900, кл. С 06 Г 15/00, 1974783795 Вача нещ ещ аказ 8550/5 Подп ис ноеВНИИПИТираж 75 Квнеи,г. 3 Филиал ППППатент ,г. Уятород, Ул. Проектная Д иа гносщиро банимемрегисщробвйм агисщрали Мекрегисоаю маг исщр исправно Рда иагносщиро 1 ание гисщра ко 1 чандныю словРегисщр каманднык Хл испрабен..,Запись б регисщркоман дныя слаб кодаивмеро сдибшееогягисщ а Д иа гн асщирова ние процв 3 вльного регисщр подключенного к межрегисщробвй и о гисщра Выбод но печащь илииндиквии(о резульщащвб диа гносщирвбанил

СмотретьЗаявка

2717714, 24.01.1979

ПРЕДПРИЯТИЕ ПЯ А-3756

ЦАКОЕВ СТАНИСЛАВ БОРИСОВИЧ, ЗАЙЦЕВ БОРИС ВАСИЛЬЕВИЧ, ЖУРАВЛЕВ АНАТОЛИЙ ИВАНОВИЧ, ЧЕРНОВ ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, ТИХАНОВИЧ КОНСТАНТИН ПЕТРОВИЧ, ЛАВРЕШИН ВИТАЛИЙ ВЛАДИМИРОВИЧ, СЕРЕДКИН ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 30.11.1980

Код ссылки

<a href="https://patents.su/4-783795-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для контроля последовательности импульсов

Следующий патент: Многоканальный цифровой фильтр

Случайный патент: Устройство для автоматической оценки состояния рельсовой колеи