Программно-задающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

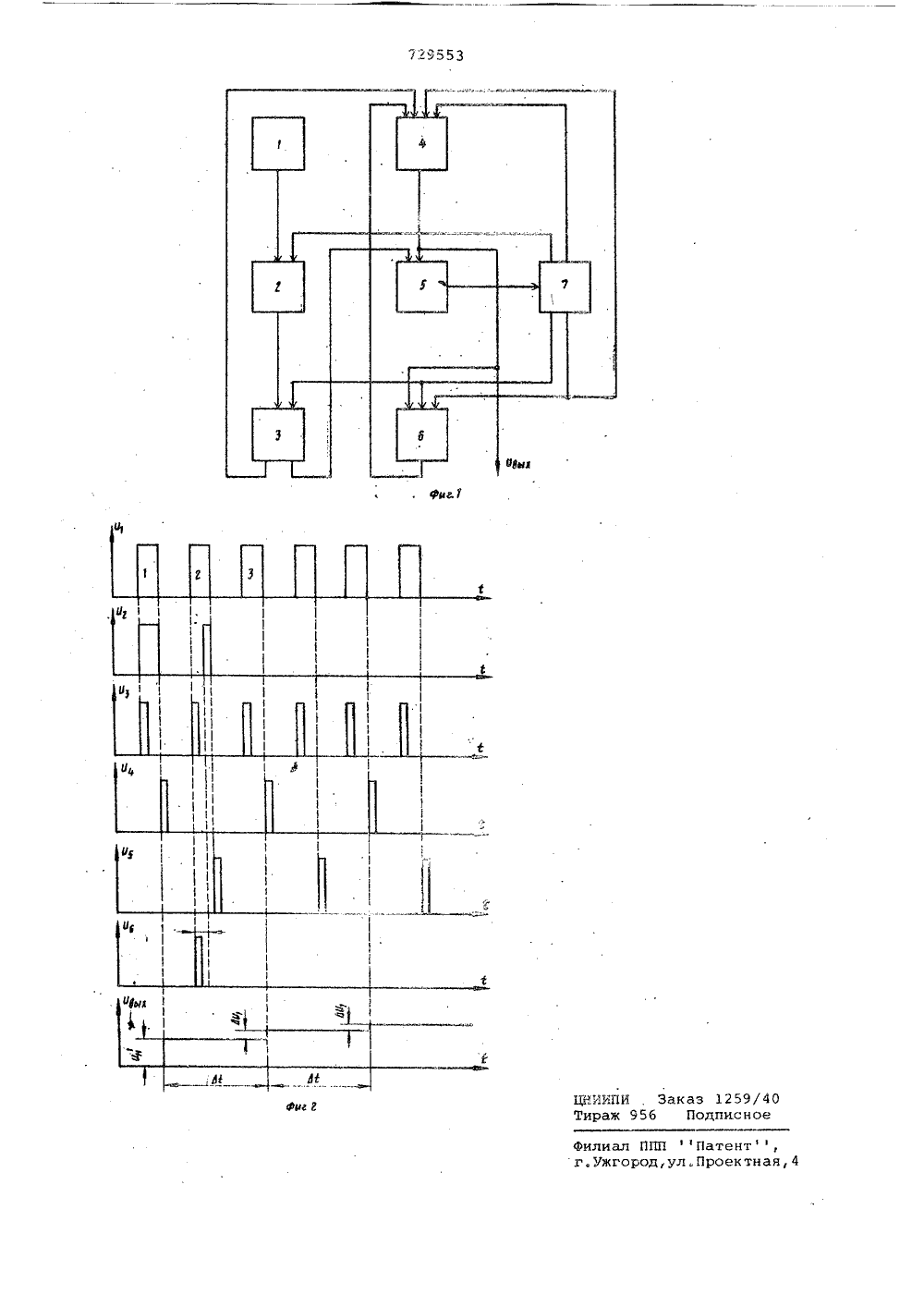

фОЕСЕац- з ИЕЮ) к.; ,в .е,.и Союз Советских Социалистических Республик(22) Заявлено 1111.77 (21) 254с присоединением заявки Йо(23) Приоритет -Опубликовано 250480. БюДата опубликования описан 5 986/18-2 арствениыи комитетСССРелам изобретенийи открытий осуд етень М 1(72) Авторы изобретения фрейдель и П,И.фай(71) Заявитель УСТРОЙСТВ 5 4 ) ПРОГРАММНО-ЗАДА аит 2 ОыПредлагаемое устройство относится к автоматическому управлению, и может быть использовано в устройствах программного регулирования параметров различных технологических процессов.Известно программное задающее устройство, содержащее блоки набор программы, каждый иэ которых состо иэ схемы задания скорости, схемы задания уровня и переключающей схемы,. причем вход схемы задания скорости подключен к управляемому делителю частоты, выход схемы задания уровня подключен к реверсивному счетчику, 15 один выход переключающей схемы соединен со схемами задания скорости и уровня, другой - с переключающей схемой последующего блока набора программ, а входы переключающей схемы соединены, соответственно, с в ходом схемы задания уровня и выходом переключающей схемы предыдущего блока набора программы 1), Однако, применение управляемого делителя частоты существенно затрудняет получение требуемой в современных условиях дискретности задания скорости изменения выходного сигнала. Кроме того, устройство, построенное 30 по такому принципу, содержит очень большое число схем переключения и блоков набора программ, равное числу участков задаваемой программы.Известно также программное задающее устройство, содержащее блок задания уровня и скорости, реверсивный счетчик со схемой совпадения, один вход которого соединен с выходом делителя частоты, другой - с выходом блока задания уровня, а выход подключен ко входу коммутатора, причем вход блока задания уровня подсоединен к выходу коммутатора 2). Это устройство содержит один блок набора программы,.однако применение управляемого делителя частоты оно также не обеспечивает получение требуемой дискретности задания скорости изменения выходного сигнала, а применение коммутатора приводит к снижению надежности устройства,Наиболее близким техническим решением к предлагаемому изобретению является программно-задающее устройство, содержащее блок постоянной программируемой памяти, выход которого соединен с входом основного блока оперативной памяти, блок сравнения, первый вход которого соединен с первым выходом основного блока оперативной памяти, блок заданияпрограммы, выход которого соединенс входом блока постоянной программируемой памяти и блок управления (31Недостатком устройства являетсято, что.оно содержит управляемыйгенератор частоты и циФроаналоговыйпреобразователь, не обеспечивающиеполучения выходного сигнала с точностью, удовлетворяющей требованиямпромышленности, а, следовательно,реализация программных задающихустройств, построенных по подобнойструктуре, является недостаточно рациональной,Целью изобретения является повышение точности и надежности устройства,Это достигается тем, что в устройство введены дополнительный блокоперативной памяти и блок алгебраического суммирования, причем второйвыход основного блока оперативнойпамяти соединен с первым входомблока алгебраического суммирования,второй вход которого соединен с выходом дополнительного блока оперативной памяти, выход блока алгебраического суммирования соединен с входом дополнительного блока онеративной памяти и со вторым входом блокасравнения, выход которого соединен свходом блока управления.На Фиг. 1 представлена функциональная схема программно-задающего устройства; на фиг. 2 - диаграммы им пульсов. Устройство содержит блокзадания программы 1, блок постояннойпрограммируемой памяти 2,основнойблок оперативной памяти 3, блок ал"гебраического суммирования 4, блоксравнения 5, дополнительный блок оперативной памяти б и блок управления 7устройство работает следующимобразом.После включения устройства в сетьиз тактовых импульсов 04 блока 7 Формируются импульсы О, поступающиена управляющий вход блока 2,Каждый импульс Одает командуна считывание чисел, хранимых вблоке 2, а адреса этих чисел определяются количеством/. импульсовпоступивших на управляющий вход блока 2 смомента включения устройства,Первый импульс Осчитывает первоечисло находящееся в, блоке 2 - наало первого участкаи вводит егов блок оперативной памяти 3, ЧислоО при этом возникает на первомй втором выходах блока 3,На эагних Фронтах импульсов 0Формируются следующие поочередноимпульсы О 4 и 0, поступающие с четвертого и второго выходов блока 7на управляющие входы блоков 6, 4и 6,3, соответственно,Первый импульс 04 дает командуалгебраического суммирования числа0 и на втором выходе блока 3 с числом на выходе блока б,Так как в рассматривае/ый моментвремени запоминающие элементы (например, регистры) блока б не заполнены, на выходе блока алгебраического суммирования возникаетчисло О иБлок 7 содержит обычную триггерную схему запрета, которая послепоступления каждого импульса Она управляющий вход блока 2 запрещает прохождение следующих импульсовдо появления; импульса на выходеблока 5. Непосредственно после включения устройства схема запрета устанавливается в открытое состояние.К моменту появления второго импульса О 4 на третьем управляющемвходе блока 4 возникает импульс О,который дает команду на передачу выходного числа блока 4 на второйвход блока 5,В связи с тем, что в рассматриваемый момент времени на первый и второй входы блока 5 поступают одина/ковые числа, а именно Он , на выходе блока 5 появляется импульс О,который через временную задержку 1 звозвращает триггерную схему запретав блоке 3 в исходное состояние, разрешающее прохождение еще одногоимпульса ОВ результате поступления второгоимпульса О на управляющий входблока 2 пройсходит считывание следующих чисел Ок и ЬО, которыепоступают на первый и второй выходы блока З,соответственно,Далее,. в момент окончания второгоимпульса О возникает первый импульс Об , который обеспечивает передачу выходного числа блока 4 в блокб с одновременным запретом считывания инФормации со второго выходаблока 3. В результате на выходе блока оперативной памяти б возникаетчисло Он .Далее, в момент появления третьеготактового импульса О возникаеттретий импульс Оз и вновь, происходит сравнение кодов с выходомблока 4 и 3. Однако теперь на первом выходе блока 3 существует числоОк - ордината конца первого участка, и, так как О, 4 О , совпадениякодов не происходит, импульс О непоявляется и, следовательно, импульсы О не проходят.Затем, в результате появлениявторого импульса 04 происходитлибо суммирование числа Ой с числом Ь 04 , либо вычитание этого жечисла из Оя в зависимости от значения знакового разряда (0 или/) числа Он . В этот моментвремени выходная величина уэеличивается на ц.В дальнейшем происходят аналогичные процессы, поэтому, в моментпрохождения каждого из импульсов04 происходит увеличение выходной величины на приращение ЬО,5а выходная величина Озь, в случаеее нарастания, принимает последовательно следующие значения;ц О+ьО,О+аьОНР Н Лф Нпричем каждое из этих значенийостается неизменным в течение шагаквантования АЕ , Таким образом,реализуется зависимость Оьггг) для1-го участка, представленная ранее 5выражениемО.:О +гг.ОйяЗатем, когда О зы,г достигает значения О, на выходе блока 5 возни цкает сигнал, пропускающий следующийимпульс О , который считываетследующие числа - Ок и АО из блока 2; эти чглсла поступают на первыйи второй выходы блока 3, соответственно, после чего ближайший импульс04 осуществит первое суммированиеили.вычитание чисел 0 и Ь Оа дальше пройзойдут процессы, аналогичные описанным и формирующие законизменения Оэыг на втором участке,ЗОпотом на третьем участке и т.д, доконца заданной программы.Построение программно-задающегоустройства по предлагаемой схемепозволяет существенно повысить точность реализации заданной программыизменения выходной величины устройства по сравнению с известными устройствами.К составляющим результирующей погрешности предлагаемого устройстваотносятся: погрешность, называемаяконечностью значений приращений ЬО;погрешность, определяемая дискретностью младших разрядов чисел концовучастков Он , 0 , Ок , по 45грешностью шага квантования ьПервые две составляющие погрешности могут быть уменьшены до скольугодно малой величины при возрастании числа разрядов чисел Ог и ггО . 50Например, для снижения этих составляющих до 0,01 для представлениячисел ОК и ьО необходимо 4 и 1 десятичных разряда, соответственно.Погрешность шага квантования возни- у 5кает при изменениях частоты =Агенератора тактовых импульсов, Этапогрешность минимизируется путем,применения кварцевого генератора тактовых импульсов с делителем час-тоты на дискретных элементах, нестабильность частоты которого и.соответствующая составляющая погрешность предлагаемого, устройства составляют сотые доли процента.Предлагаемое устройство существенно превосходит известное по точности, что обеспечивает целесообразность его применения для прецизионного контроля и регулирования,обеспечивающего высокое качествовыпускаемой продукции. Кроме того,в предлагаемом устройстве отсутствует цифроаналоговый преобразователь и сложные коммутирующие устрой",тва.Устранение цифроаналогового преобразователя и коммутаторов значительно повышает надежность в работеустройства и обеспечивает возможность его применения для контроляи регулирования ответственных.технологических параметров,Формула изобретенияПрограммно-задающее устройство,содержащее блок постоянной программируемой памяти, выход которого соеди-нен с входом основного блока оперативной памяти, блок сравнения, первый вход которого соединен с первымвыходом основного блока оперативнойпамяти, блок задания программы, выход которого соединен с входом блокапостоянной программируемой памятии блок управления, о т л и ч а ющ е е с я тем, что, с целью повышения точности и надежности устройства, в него введены дополнительныйблок, оперативной памяти и блокалгебраического суммирования, причем второй выход основного блокаоперативной памяти соединен с первымвходом блока алгебраического.суммированиявторой вход которого соединенс выходом дополнительного блока оперативной памяти, выход блока алгебра-ического суммирования соединен с входом дополнительного блока оперативной памяти и со вторым входом блокасравнения, выход которого соединенс входом блока управления.Источники информации,принятые во внимание при экспертизе

СмотретьЗаявка

2542986, 11.11.1977

ПРЕДПРИЯТИЕ ПЯ А-7141

ФРЕЙДЕЛЬ ЛЕВ РАФАИЛОВИЧ, ФАЙН ПАВЕЛ ИОЭЛЬЕВИЧ

МПК / Метки

МПК: G05B 19/406, G05B 19/418

Метки: программно-задающее

Опубликовано: 25.04.1980

Код ссылки

<a href="https://patents.su/4-729553-programmno-zadayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Программно-задающее устройство</a>

Предыдущий патент: Способ управления движением промышленного робота

Следующий патент: Устройство для проведения многофакторного эксперимента

Случайный патент: Устройство для регулирования линейной скорости ленточного материала