Устройство для одновременного суммирования нескольких двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

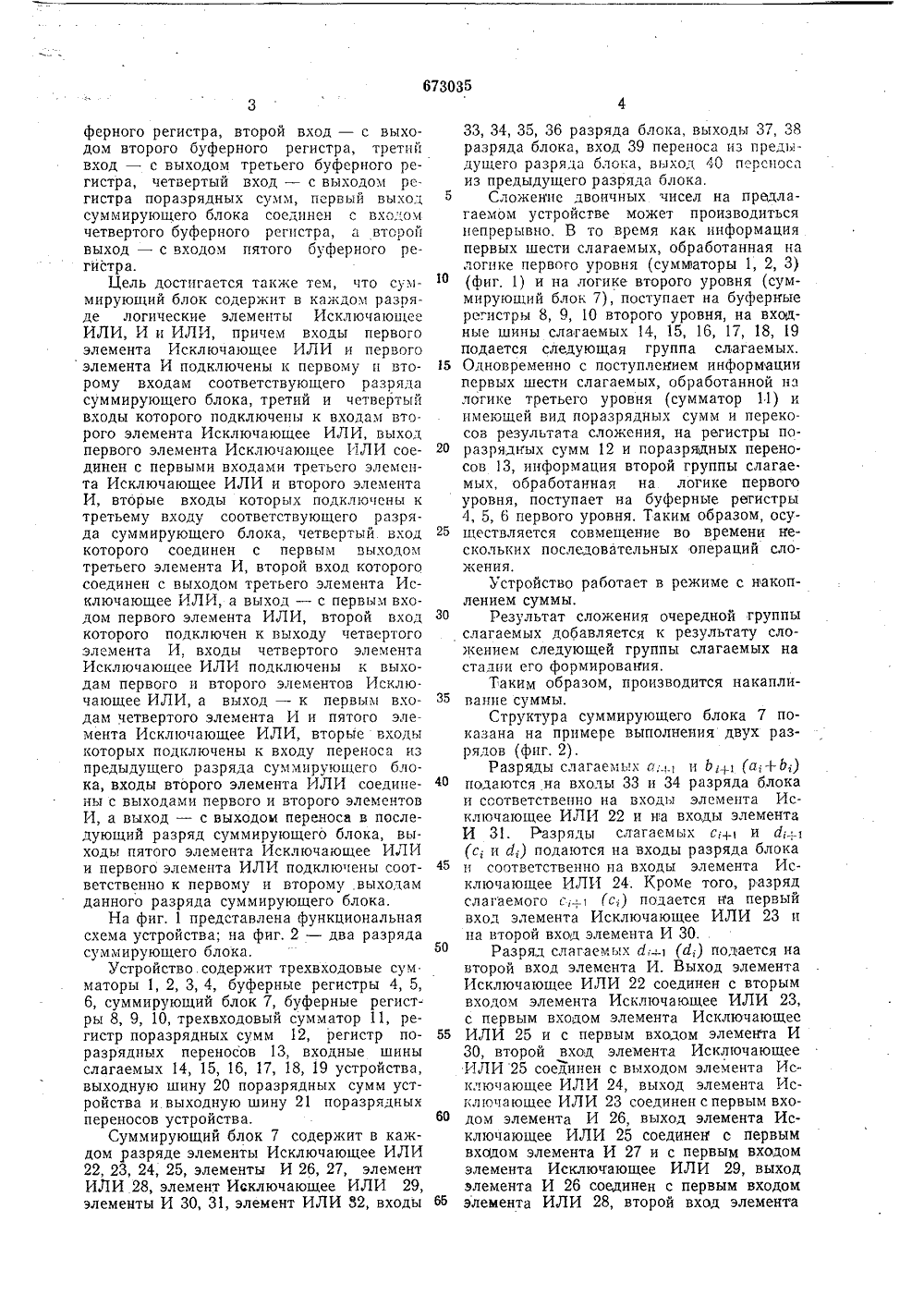

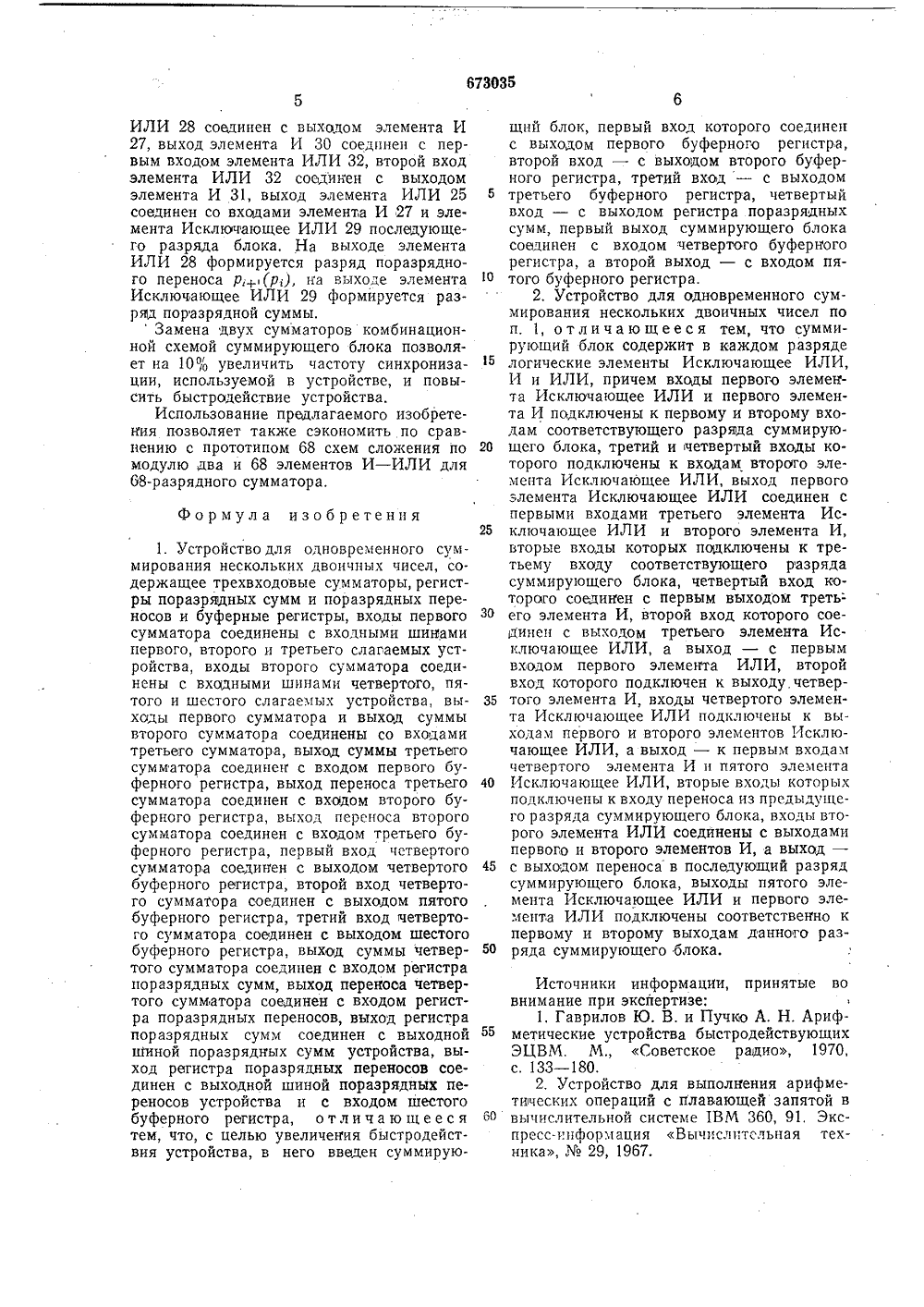

(51) М.Кл, 6 06 Г 7 7452,1 22) Заявлено 18,08.77 (21 исоединением зая Хосударственный комите ри ритет - ликовано 07.01.82 опубликования о по делам изобретени и открытий(72) Авторы изобретения люсарев, И. С. Храмцов и А, А, Аредов 1) Заявитель РД 1 ЬфЮЙ ДЛЯ ОДНОВРЕМЕННОГОКОЛЬКИХ ДВОИЧНЫХ ЧИСЕ(54) УСТРОЙСТВОММИРОВАНИЯ НЕ ия являетсстройства,этой целиий блок, пвыходом изобретенодействия устижениясуммирующоединен с в устроистервый вход первого б 1 тИзобретение относится к области вычислительной техники и может быть исполь-. зовано в универсальных цифровых вычислительных машинах высокого быстродействия,Известны устройства для одновременного суммирования нескольких двоичных чисел, представляющие собой древовидную конструкцию из сумматоров с запоминанием переносов или из сумматоров с приведением переносов 11.Однако такие устройства имеют недостаточное быстродействие в связи с большим числом последовательно соединенных сумматоров,Наиболее близким аналогом изобретения является устройство для одновременного суммирования нескольких двоичных чисел, содержащее трехвходовые сумматоры, регистры поразрядных сумм и поразрядных переносов и буферные регистры, входы первого сумматора соединены с входными шинами первого, второго и третьего слагаемых устройства, входы второго сумматора соединены с входными шинами четвертого, пятого и шестого слагаемых устройства, выходы первого сумматора и выход суммы второго сумматора соединены с входами третьего сумматора, выход суммы третьего сумматора соединен с входом первого буферного регистра, выход переноса третьего сумматора соединен с входом второго буферного регистра, выход переноса второго сумматора соединен с 5 входом третьего буферного регистра, первый вход четвертого сумматора соединен с выходом четвертого буферного регистра, второй вход четвертого сумматора соединен с выходом пятого буферного регистра, тре тий вход четвертого сумматора соединен свыходом шестого буферного регистра, выход суммы четвертого сумматора соединен с входом регистра поразрядных сумм, выход переноса четвертого сумматора соеди нсн с входом регистра поразрядных переносов, выход регистра поразрядных сумм соединен с выходной шиной поразрядных сумм устройства, выход регистра поразрядных переносов соединен с выходной ши- О ной поразрядных переносов устройства и свходом шестого буферного регистра 21.Однако это устройство имеет недостаточное быстродействие в связи с большим числом последовательно соединенных сум маторов.Целью я увеличение быстрДля дово введенкоторого сферного регистра, второй вход - с выходом второго буферного регистра, третий вход - с выходом третьего буферного регистра, четвертый вход - с выходом рсгистра поразрядных сумм, первый выход суммирующего блока соединен с входом четвертого буферного регистра, а второй выход - с входом пятого буферного регйстра.Цель достигается также тем, что суммирующий блок содержит в каждом разряде логические элементы Исключающее ИЛИ, И и ИЛИ, причем входы первого элемента Исключающее ИЛИ и первого элемента И подключены к первому и вто- Б рому входам соответствующего разряда суммирующего блока, третий и четвертый входы которого подключены к входам второго элемента Исключающее ИЛИ, выход первого элемента Исключающее ИЛИ сое динен с первыми входами третьего элемента Исключающее ИЛИ и второго элемента И, вторые входы которых подключены к третьему входу соответствующего разряда суммирующего блока, четвертый вход 25 которого соединен с первым выходом третьего элемента И, второй вход которого соединен с выходом третьего элемента Исключающее ИЛИ, а выход - с первым входом первого элемента ИЛИ, второй вход ЗО которого подключен к вьходу четвертого элемента И, входы четвертого элемента Исключающее ИЛИ подключены к выходам первого и второго элементов Исключающее ИЛИ, а выход - к первым вхо- З 5 дам четвертого элемента И и пятого элемента Исключающее ИЛИ, вторые входы которых подключены к входу переноса из предыдущего разряда суммирующего блока, входы второго элемента ИЛИ соедине ны с выходами первого и второго элементов И, а выход - с выходом переноса в последующий разряд суммирующего блока, выходы пятого элемента Исключающее ИЛИ и первого элемента ИЛИ подключены соот ветственно к первому и второму выходам данного разряда суммирующего блока.На фиг, 1 представлена функциональная схема устройства; на фиг. 2 - два разряда суммирующего блока.50Устройство. содержит трехвходовые сум маторы 1, 2, 3, 4, буферные регистры 4, 5, 6, суммирующий блок 7, буферные регистры 8, 9, 10, трехвходовый сумматор 11, регистр поразрядных сумм 12, регистр по разрядных переносов 13, входные шины слагаемых 14, 15, 16, 17, 18, 19 устройства, выходную шину 20 поразрядных сумм устройства и выходную шину 21 поразрядных переносов устройства.60Суммирующий блок 7 содержит в каждом разряде элементы Исключающее ИЛИ 22, 23, 24, 25, элементы И 26, 27, элемент ИЛИ 28, элемент Исключающее ИЛИ 29, элементы И 30, 31, элемент ИЛИ 32, входы % 33, 34, 35, 36 разряда блока, выходы 3, 38 разряда блока, вход 39 переноса из предыдущего разряда блока, выход 40 переноса из предыдущего разояда блока.Сложение двоичных чисел на предлагаемом устройстве может производиться непрерывно, В то время как информация первых шести слагаемых, обработанная на логике первого уровня (сумматоры 1, 2, 3) (фиг, 1) и на логике второго уровня (суммирующий блок 7), поступает на буферные регистры 8, 9, 10 второго уровня, на входные шины слагаемых 14, 15, 16, 17, 18, 19 подается следующая группа слагаемых. Одновременно с поступлением информации первых шести слагаемых, обработанной на логике третьего уровня (сумматор 11) и имеющей вид поразрядных сумм и перекосов результата сложения, на регистры поразрядных сумм 12 и поразрядных переносов 13, информация второй группы слагае. мых, обработанная на логике первого уровня, поступает на буферные регистры 4, 5, 6 первого уровня. Таким образом, осуществляется совмещение во времени нескольких последовательных операций сложения.Устройство работает в режиме с накоплением суммы.Результат сложения очередной группы слагаемых добавляется к результату сло;кением следующей группы слагаемых на стадии его формирования.Т 1 аким образом, производится накаплиВание суммы,Структура суммирующего блока 7 показана на примере выполнения двух разрядов (фиг. 2).Разряды слагаемых а,1 и Ь,+1 (а;+Ь;) подаются на вхолы 33 и 34 разряда блока и соответственно на входы элемента Исключающее ИЛИ 22 и на входы элемента И 31. Разряды слагаемых с,+ и А (с, и 4) подаются на входы разряда блока и соответственно на входы элемента Исключаюгцее ИЛИ 24. Кроме того, разряд слагаемого с; 1 (с;) подается на первый вход элемента Исключающее ИЛИ 23 и на второй вход элемента И 30.Разряд слагаемых д; 1 (А) подается на второй вход элемента И. Выход элемента Исключающее ИЛИ 22 соединен с вторым входом элемента Исключающее ИЛИ 23, с первым входом элемента Исключающее ИЛИ 25 и с первым входом элемента И 30, второй вход элемента Исключающее ИЛИ 25 соединен с выходом элемента Исключающее ИЛИ 24, выход элемента Исключающее ИЛИ 23 соединен с первым входом элемента И 26, выход элемента Исключающее ИЛИ 25 соединен с первым входом элемента И 27 и с первым входом элемента Исключающее ИЛИ 29, выход элемента И 26 соединен с первым входом элемента ИЛИ 28, второй вход элементаИЛИ 28 соединен с выходом элемента И 27, выход элемента И 30 соединен с первым входом элемента ИЛИ 32, второй вход элемента ИЛИ 32 соединен с выходом элемента И 31, выход элемента ИЛИ 25 соединен со входами элемента И 27 и элемента Исключающее ИЛИ 29 последующего разряда блока. На выходе элемента ИЛИ 28 формируется разряд поразрядного переноса р; (р,), на выходе элемента Исключающее ИЛИ 29 формируется разряд поразрядной суммы,Замена двух сумматоров комбинационной схемой суммирующего блока позволяет на 10 увеличить частоту синхронизации, используемой в устройстве, и повысить быстродействие устройства.Использование предлагаемого изобретения позволяет также сэкономить по сравнению с прототипом 68 схем сложения по модулю два и 68 элементов И - ИЛИ для 68-разрядного сумматора. Формула изобретения1, Устройство для одновременного суммирования нескольких двоичных чисел, содержащее трехвходовые сумматоры, регистры поразрядных сумм и поразрядных переносов и буферные регистры, входы первого сумматора соединены с входными шинами первого, второго и третьего слагаемых устройства, входы второго сумматора соединены с входными шинами четвертого, пятого и шестого слагаемых устройства, выходы первого сумматора и выход суммы второго сумматора соединены со входами третьего сумматора, выход суммы третьего сумматора соединен с входом первого буферного регистра, выход переноса третьего сумматора соединен с входом второго буферного регистра, выход переноса второго сумматора соединен с входом третьего буферного регистра, первый вход четвертого сумматора соединен с выходом четвертого буферного регистра, второй вход четвертого сумматора соединен с выходом пятого буферного регистра, третий вход четвертого сумматора соединен с выходом шестого буферного регистра, выход суммы четвертого сумматора соединен с входом регистра поразрядных сумм, выход переноса четвертого сумматора соединен с входом регистра поразрядных переносов, выход регистра поразрядных сумм соединен с выходной Шиной поразрядных сумм устройства, выход регистра поразрядных переносов соединен с выходной шиной поразрядных переносов устройства и с входом шестого буферного регистра, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, в него введен суммирую 25 ЗО 35 40 45 50 55 50 щий блок, первый вход которого соединен с выходом первого буферного регистра, второй вход - с выходом второго буферного регистра, третий вход - с выходом третьего буферного регистра, четвертый вход - с выходом регистра поразрядных сумм, первый выход суммирующего блока соединен с входом четвертого буферного регистра, а второй выход - с входом пятого буферного регистра,2. Устройство для одновременного суммирования нескольких двоичных чисел по и. 1, отличающееся тем, что суммирующий блок содержит в каждом разряде логические элементы Исключающее ИЛИ, И и ИЛИ, причем входы первого элемента Исключающее ИЛИ и первого элемента И подключены к первому и второму входам соответствующего разряда суммирующего блока, третий и четвертый входы которого подключены к входам второго элемента Исключающее ИЛИ, выход первого элемента Исключающее ИЛИ соединен с первыми входами третьего элемента Исключающее ИЛИ и второго элемента И, вторые входы которых подключены к третьему входу соответствующего разряда суммирующего блока, четвертый вход юторого соединен с первым выходом третьего элемента И, второй вход которого соединен с выходом третьего элемента Исключающее ИЛИ, а выход - с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, входы четвертого элемента Исключающее ИЛИ подключены к выходам первого и второго элементов Исключающее ИЛИ, а выход - к первым входам четвертого элемента И и пятого элемента Исключающее ИЛИ, вторые входы которых подключены к входу переноса из предыдущего разряда суммирующего блока, входы второго элемента ИЛИ соединены с выходами первопо и второго элементов И, а выход - с выходом переноса в последующий разряд суммирующего блока, выходы пятого элемента Исключающее ИЛИ и первого элемента ИЛИ подключены соответственно к первому и второму выходам данного разряда суммирующего блока. Источники информации, принятые во внимание при экспертизе:11, Гаврилов Ю. В, и Пучио А, Н, Арифметические устройства быстродействующих ЭЦВМ, М., Советское радио, 1970, с, 133 - 180.2. Устройство для выполнения арифметических операций с плавающей запятой в вычислительной системе 1 ВМ 360, 91, Экспресс-информация Вычислительная техника, Мо 29, 1967.Т рьк. фил. пред. Пате Заказ 27/32 1 ПО Поиск Изд,106Тираж 731 Подписноеосударственного комитета ГСГР по делам изобретений и открытии 113035, Москва, Ж, Раушская наб д. 4/5

СмотретьЗаявка

2517452, 18.08.1977

ПРЕДПРИЯТИЕ ПЯ М-5769

СЛЮСАРЕВ Н. А, ХРАМЦОВ И. С, АРЕДОВ А. А

МПК / Метки

МПК: G06F 7/50

Метки: двоичных, нескольких, одновременного, суммирования, чисел

Опубликовано: 07.01.1982

Код ссылки

<a href="https://patents.su/4-673035-ustrojjstvo-dlya-odnovremennogo-summirovaniya-neskolkikh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для одновременного суммирования нескольких двоичных чисел</a>

Предыдущий патент: Стабилизатор напряжения для калибровки преобразователей лазерного излучения

Следующий патент: 9-иод-6-перхлорато-3, 4-диметоксикарбонилтетрацикло 6, 1, 1, о, 0, дец-3-ен, обладающий иммунодепрессивной активностью

Случайный патент: Огнеупорная масса