Интегро-дифференциальный вычис-литель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 798902

Автор: Баранов

Текст

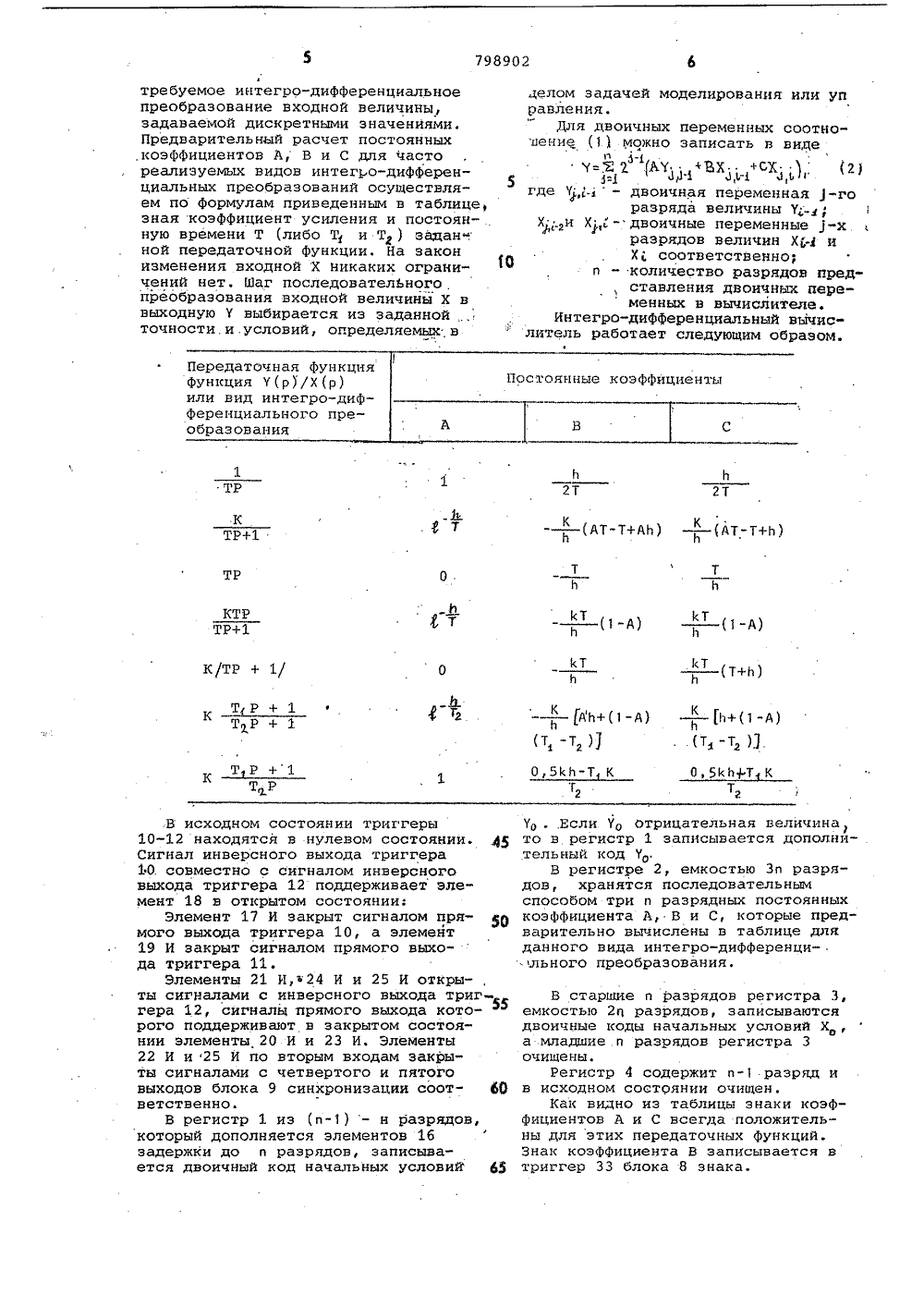

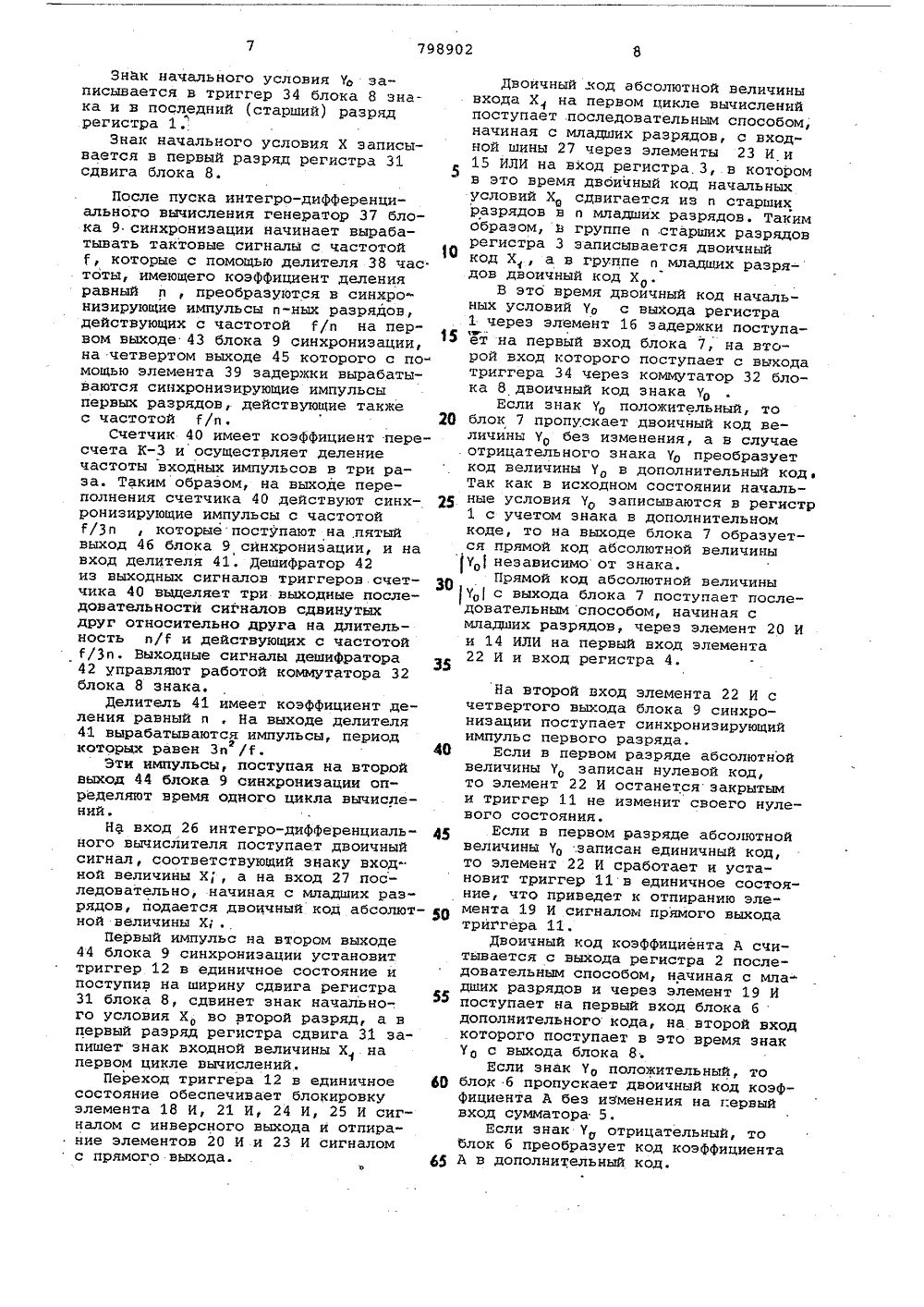

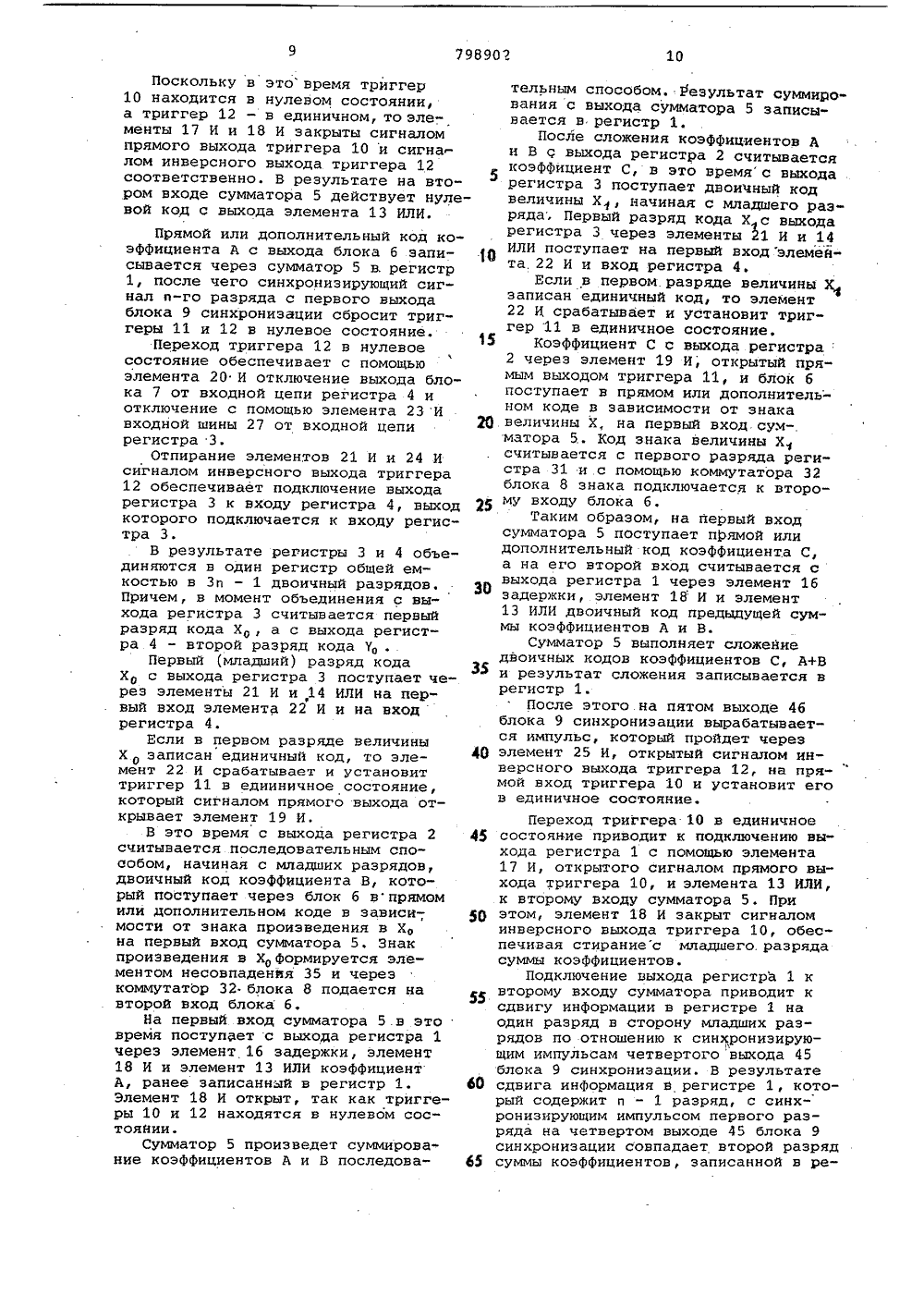

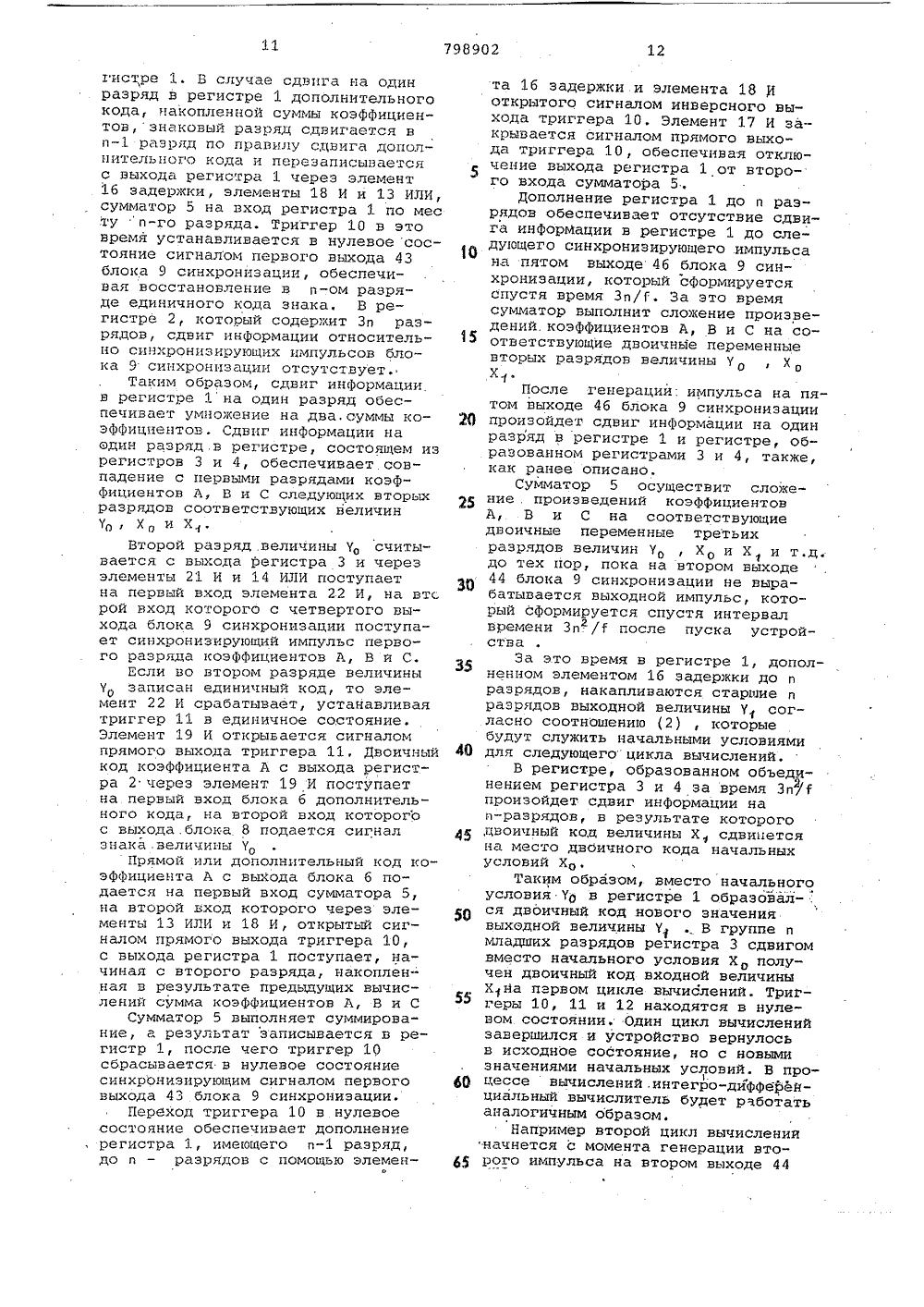

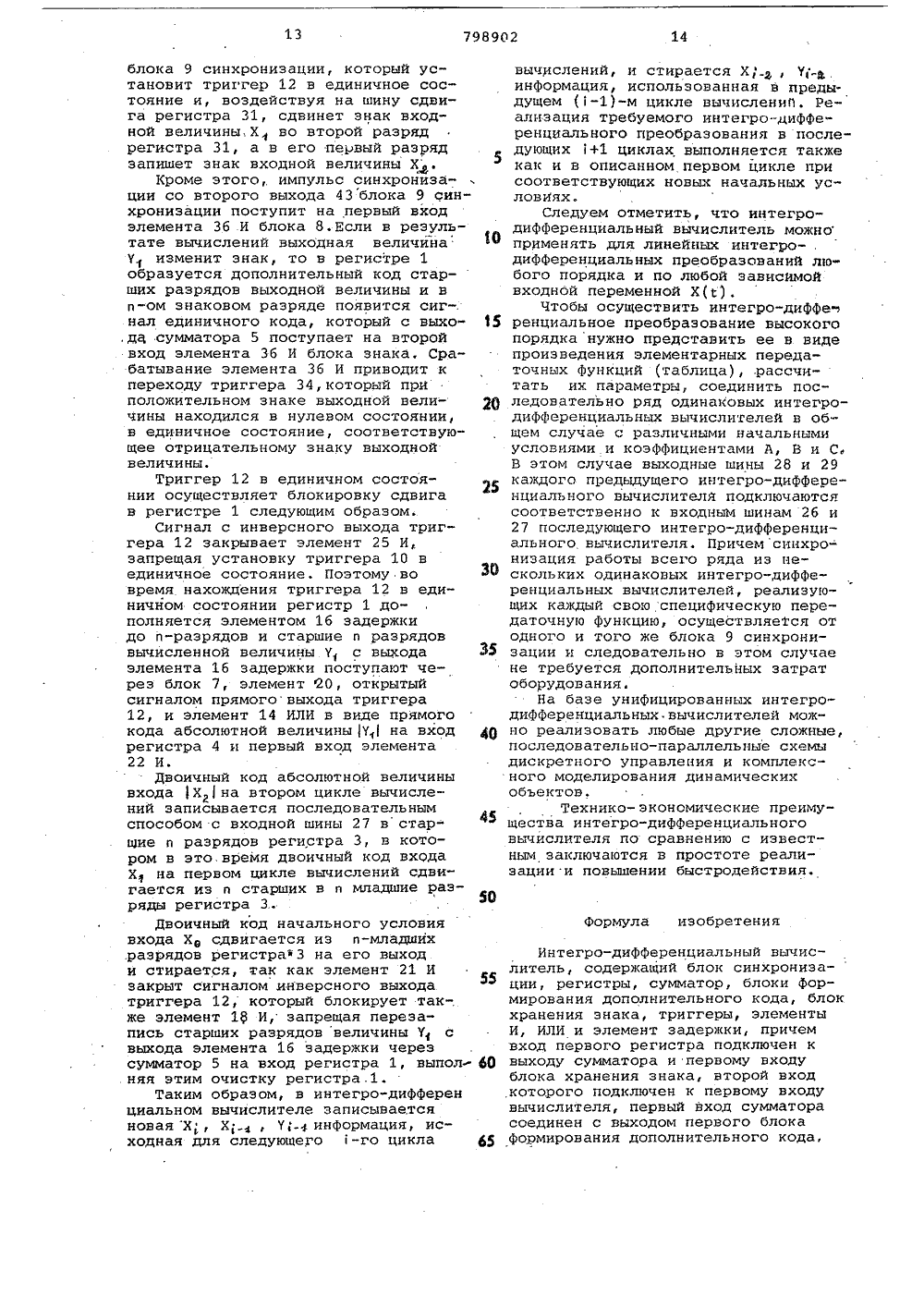

фМчмир 4 о ОП ИИЗОБРЕТЕН Союз СоветскихоциалистическихРееттублик п 1198902 Дополнительное к авт, свнд-ву Заявлено 22,0.79 (21) 2715 Кл.з б Л 1/О с прнсо некием ваяекн осударствениый комитет ссср по делам изобретений и открытийит Опубликовано Дата опублнко я 1. Г оллет описания 2 53) УДК 681,.Л. Баранов и Г.Л. Баран Ордена Ленина и институт эл ститут кибернетики АН Украинской Стродинамики АН Украинской ССР(71 Заявит 4) ИНТЕГРО-ДИФФЕРЕ НЫЙ ВЫЧИСЛИТЕЛЬ 1 О Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для моделированияи управления динамическими объектамкв различных отраслях промышленности.Известны аналоговые интегро-дифференциальные устройства, содержащиеаналоговые интеграторы,.сумматорыи масштабные блоки для задания коэффициентов передачи 13Недостатком аналоговых интегродифференциальных устройств являетсянизкая точность вычисления выходныхсигналов в случае достаточно больших значений постоянных времени,характерных для многих технологических процессов. - ,Наиболее близким техническим решением к предлагаемому являетсяинтегро-дифференциальный вычислитель, содержащий. четыре регистра,сумматор, два блока дополнительногокода, блок синхронизации, три триггера, элементы И, ИЛИ и элемент задержки, причем вход первого регистраподключен к выходу сумматора и первому входу блока знака, второй входкоторого подключен к первой входной шине, первый вход сумматора под;ключен к выходу первого блока дополнительного кода, второй вход сум матора подключен к выходу первого элемента ИЛИ, входы которого подключены к выходам первого и второго элементов И, подключенных первыми входами. соответственно к прямому и инверсному выходам первоготриггера, выход первого регистра подключен ко второму входу первого э мента И, блок синхронизации подк первым выходом к инверсным входам первого, второго и третьего триггеров, вторым вйходом - к третьему входу блока знака и третьей группой выходов - к четвертой группевходов 23Недостатками известного устройства является относительно высокие аппаратурные затраты и низкое быстродействие.Относительно высокие аппаратурные затраты на реализацию интегродифференциального вычислителя с помощью цифровых интеграторов вызваны ростом колиЧества цифровых интеграторов в зависимости от сложнос ти интегро-дифференциальногопреобразования.Низкое быстродействие цифровых дифференцильных анализаторов связаф Заказ 100 б 1/71 Тираж 756 ВНИИПИ Государственного комите по делам изобретений и откр 113035, Москва, Ж, Рауыскаяно с вычислениями одноразрядных приращений на одном шаге, что требуетзначительного количества шагов наинтервале интегрирования.Цель изобретения - упрощение вычислителя и повышения его быстродействия,Поставленная цель достигается тем,что н интегро-дифференциальном ййчЫслителе, содержащем блок синхронизации, регистры, сумматорблоки формирования дополнительного кода, блокхранения знака, триггеры, элементы И,ИЛИ, и элемент задержки, причем входпервого регистра подключен к выходусумматора и первому входу блока хранения знака,. второй вход которогоподключен к первому входу вычислителя, первый вход сумматора соеди- .нен с выходом первого блока формиро.вания дополнительного кода, второйвход сумматора подключен к выходупервого элемента ИЛИ, входы которого подключены соответственно к выходам первого и второго элементовИ, первые входы которых подключенысоответственно к прямому и инверс-.ному выходам первого триггера, выход первого регистра подключен ковторому входу первого элемента.И,первый ныход блока синхронизацииподключен к инверсным входам первого, второго и третьего триггеров,второй выход - к третьему входу блока хранения знака, группа выходовк группе входов блока хранения знака, второй вход второго элемента Иподключен к первому входу второгоблока формирования дополнительногокода непосредственно и через элементзадержки - к выходу первого регистра, первый вход первого блока формирования дополнительного кода подключен к выходу третьего элементаИ, первый вход которого подключен квыходу второго регистра, второйвход - к прямому выходу второго триггера, вторые входы первого и второго блоков формирования дополнительного кода подключены к выходу блокахранения знака и к первому выходувычислителя, выход второго блокаформирования дополнительного кодаподключен к первому входу четвертого элемента И, выход третьего регистра подключен к первому входу пятого. элемента И, входы второго элемента ИЛИ подключены соответственнок выходам четвертого и пятогоэлементов И, вход четвертого регистраподключен к выходу второго элементаИЛИ и к первому входу шестого элемента И, второй вход которого подключен к третьему выходу блока синхронизации, а выход - к прямому входувторого триггера, входы третьего элемента ИЛИ подключены соответственнок выходам седьмого и восьмого элементов И, выход третьего элемента ИЛИ соединен с входом третьегорегистра, первый вход седьмого элемента И подключен ко второму входувычислителя, второй вход - к прямому выходу третьего триггера, инверсный выход которого соединен сгретьим входом вгорого элемента И,вторым входом пятого элемента И ипервыми входами восьмого и девятогоэлементов И элемента и подключенк выходу четвертого регистра, прямой вход третьего триггера соединен с вторым выходом блока синхронизации, четвертый выход которого подключен ко второму входудевятого элемента И, выход которо 15 го соединен с прямым входом первоготриггера, второй выход вычислителясоединен с выходом четвертого элемента И,20 Ца фиг. 1 изображена структурнаясхема интегро-дифференциального вычислителя; на фиг. 2 - структурнаясхема блока знака и блока синхронизации.Я Интегро-дифференциальный вычислителы(фиг. 1) содержит четыререгистра 1-4, сумматор 5, дна блока б и 7 формирования дополнительного кода , блок 8 хранения знака,блок 9 синхронизации, три триггера10-12, три элемента 13-15 ИЛИ, элемент 1 б задержки, девять элементов17-25 И, два входа 2 би дна выхода 28-29.Интегро-дифференцильный вычислитель для каждого 1-го цикла отрабатывает рекуррентное соотношениет =АУ+ВХ + СХ (1)где У, и У- значейия выходнойвеличины соответственно на 1-м и (1-1)цикле. вычисленийА, В, С - постоянные коэффйциенты, значения кото рых зависят от шагапо независимой пере-менной, согласно которому осуществляется переход от 50 (1-1) -го к 1-му и последующим циклам вычислений, а так жеот вида реализуемогоинтегро-дифференци ального преобразонания;Х- и Хвзначения входной ве-.личины соответственно на 1-м и(1-1)-мцикле вычислений.60Для настройки вычислителя осуще.стнляется ввод постоянных коэффици- ентов А,.В и С и начальных условий Уи Х- . Далее с постоянным шау гом В согласно (1) осуществляется(АЪ+ (1(Т Т Уо от истр 1 код У. истре анятся три и ента А но выч вида и преобр Уо.Есл то в ре тельныйВ ре дов, хр способом козффици варнтел данного льного егистра 3, исываютсясловий Х, стра 3 4требуемое интегро-дифференциальное преобразование входной величины, задаваемой дискретными значениями. Предварительный расчет постоянных ,коэффициентов А, В и С для часто реализуемых видов интегро-дифференциальных преобразований осуществляем по формулам приведенным в таблице, зная коэффициент усиления и постоянную времени Т (либо Т и Т ) задан-. ной передаточной функции. На закон изменения входной Х никаких ограничений нет. Шаг последовательного преобразования входной величины Х в выходную У выбирается из заданной точности.и.условий, определяемых в.В исходном состоянии триггеры 10-12 находятся в нулевом состоянии. Сигнал инверсного выхода триггера 10. совместно с сигналом инверсного выхода триггера 12 поддерживает элемент 18 в открытом состоянии:Элемент 17 И закрыт сигналом прямого выхода триггера 10, а элемент 19 И закрыт сигналом прямого выхода триггера 11.Элементы 21 И,ф 24 И и 25 И открыты сигналами с инверсного выхода триггера 12, сигналы прямого выхода которого поддерживают в закрытом состоянии элементы 20 И и 23 И. Элементы 22 И и 25 И по вторым входам закрыты сигналами с четвертого и пятого выходов блока 9 синхронизации соот ветственно.В регистр 1 из (и) - н разрядов, который дополняется элементов 1 б задержки до о разрядов, записывается двоичный код начальных условий 65 делом задачей моделирования или уп равления.,цля двоичных переменных соотношение (1) можно записать в вице где У. - двоичная переменная 1-горазряда величины У , Хи Х,."- двоичные переменные 1-хразрядов величин ХЯ иХ; соответственно;и - количество разрядов представления двоичных переменных в вычислителе.Интегро-дифференциальный вычис" литель работает следующим образом. стоянные коэффициенты 0,5 МЬ-Т К 0,5 МЬ+Т К т, Тицательная величиназаписывается дополнй 2, емкостью Зп разряпоследовательным разрядных постоянныхВ и С, которые пред ислены в таблице для нтегро-дифференциазования. В старшие и разрядов ремкостью 2 ц разрядов, запдвоичные коды начальных уа младшие и разрядов региочищены.Регистр 4 содержит иразряд и в исходном состоянии очищен.Как видно из таблицы знаки коэффициентов А и С всегда положительны для этих передаточных функцийЗнак коэффициента В записывается в триггер 33 блока 8 знака.Знак начального условия У записывается в триггер 34 блока 8 знака и в последний (старший) разряд регистра 1,Знак начального условия Х записывается в первый разряд регистра 31 сдвига блока 8.После пуска интегро-дифференциальноГо вычисления генератор 37 блока 9 синхронизации начинает вырабатывать тактовые сигналы с частотойУ, которые с помощью делителя 38 частоты, имеющего коэффициент деленияравный и , преобразуются в синхро"низирующие импульсы и-ных разрядов,действующих с частотой Г/и на первом выходе 43 блока 9 синхронизации,на четвертом выходе 45 которого с помощью элемента 39 задержки вырабатываются синхронизирующие импульсыпервых разрядов, действующие такжес частотой Г/и,Счетчик 40 имеет коэффициент пересчета Ки осуществляет делениечастоты входных импульсов в три раза. Таким образом, на выходе переполнения счетчика 40 действуют синхронизирующие импульсы с частотойГ/3 и , которые поступают на,нятыйвыход 46 блока 9 синхронизации, и навход делителя 41. Дешифратор 42из выходных сигналов триггеров. счетчика 40 выделяет три выходные последовательности сигналов сдвинутыхдруг относительно друга на длительность и/Г и действующих с частотойГ/Зп, Выходные сигналы дешифратора42 управляют работой коммутатора 32блока 8 знака.Делитель 41 имеет коэффициент деления равный и , На выходе делителя41 вырабатываются импульсы, периодкоторых равен Зп /У.Эти импульсы, поступая на второйвыход 44 блока 9 синхронизации определяют время одного цикла вычислений.На вход 26 интегро-дифференциального вычислителя поступает двоичныйсигнал, соответствующий знаку входной величины Х;, а на вход 27 последовательно, начиная с младших разрядов, подается двоичный код абсолютной величины ХПервый импульс на втором выходе44 блока 9 синхронизации установиттриггер 12 в единичное состояние ипоступив на ширину сдвига регистра31 блока 8, сдвинет знак начально-.го условия Хо во второй разряд, а впервый разряд регистра сдвига 31 запишет знак входной величины Х напервом цикле вычислений,Переход триггера 12 в единичноесостояние обеспечивает блокировкуэлемента 18 И, 21 И, 24 И, 25 И сигналом с инверсного выхода и отпирание элементов 20 И и 23 И сигналомс прямого выхода.ъ Двоичный лод абсолютной величинывхода Х на первом цикле вычисленийпоступает последовательным способомУначиная с младших разрядов, с входной шины 27 через элементы 23 И и15 ИЛИ на вход регистра.З, в которомв это время двоичный код начальныхусловий Хд сдвигается из и старшихразрядов в и младших разрядов. ТакимОбразом, в группе и старших разрядоврегистра 3 записывается двоичныйкод Х , а в группе и младших разрядов двоичный код Х.В это время двойчный код начальных условий Уо с выхода регистра1 через элемент 16 задержки поступа 1 с "15 ет на первый вход блока 7, на второй вход которого поступает с выходатриггера 34 через коммутатор 32 блока 8 двоичный код знака УоЕсли знак Уо положительный, то 20 блок 7 пропускает двоичный код величины У без изменения, а в случае. отрицательного знака Уо преобразуеткод величины У в дополнительный кодТак как в исходном состоянии началь ные условия У записываются в регистр1 с учетом знака в дополнительномкоде, то на выходе блока 7 образуется прямой код абсолютной величиныУ независимоот знака.Прямой код абсолютной величиныУс выхода блока 7 поступает последовательным способом, начиная смладших разрядов, через элемент 20 Ии 14 ИЛИ на первый вход элемента22 И и вход регистра 4. На второй вход элемента 22 И счетвертого выхода блока 9 синхронизации поступает синхронизирующийимпульс первого разряда.40 Если в первом разряде абсолютнойвеличины У записан нулевой код,то элемент 22 И останется закрытыми триггер 11 не изменит своего нулевого состояния,Если в первом разряде абсолютнойвеличины Уо записан единичный код,то элемент 22 И сработает и установит триггер 11 в единичное состояние, что приведет к отпиранию элемента 19 И сигналом прямого выходатриггера 11.Двоичный код коэффициента А считывается с выхода регистра 2 последовательным способом, начиная с младших разрядов и через элемент 19 Ипоступает на первый вход блока бдополнительного кода, на второй входкоторого поступает в это время знакУо с выхода блока 8.Если знак Уо положительный, тоЯ блок б пропускает двоичный код коэффициента А без изменения на первыйвход сумматора 5.Если знак Уд отрицательный, тоблок б преобразует код коэффициента65 А в дополнительный код.Поскольку в это время триггер 10 находится в нулевом состоянии, а триггер 12 - в единичном, то элементы 17 И и 18 И закрыты сигналом прямого выхода триггера 10 и сигна лом инверсного выхода триггера 12 соответственно. В результате на втором входе сумматора 5 действует нуле вой код с выхода элемента 13 ИЛИ.Прямой или дополнительный код коэффициента А с выхода блока б записывается через сумматор 5 в. регистр1, после чего синхронизирующий сигнал и-го разряда с первого выхода блока 9 синхронизации сбросит триггеры 11 и 12 в нулевое состояние.Переход триггера 12 н нулевое состояние обеспечивает с помощью элемента 20 И отключение выхода блока 7 от входной цепи регистра 4 и отключение с помощью элемента 23 И входной шины 27 от входной цепи регистра 3.Отпирание элементов 21 И и 24 И сигналом инверсного выхода триггера 12 обеспечивает подключение выхода регистра 3 к входу регистра 4, выход которого подключается к входу регистра 3.В результате регистры 3 и 4 объединяются в один регистр общей емкостью в Зи - 1 двоичный разрядов. Причем, в момент объединения с выхода регистра 3 считывается первый разряд кода Хо, а с выхода регистра 4 - второй разряд кода У, .Первый (младший) разряд кода Хо с выхода регистра 3 поступает через элементы 21 И и,14 ИЛИ на первый вход элемента 22 И и на вход регистра 4.Если в первом разряде величины Х о записан единичный код, то элемент 22 И срабатывает и установит триггер 11 в едииничное состояние, который сигналом прямого выхода открывает элемент 19 И.В это время с выхода регистра 2 считывается последовательным способом, начиная с младших разрядов, двоичный код коэффициента В, который поступает через блок б впрямом или дополнительном коде в зависимости от знака произведения в Хо на первый вход сумматора 5. Знак произведения в Хо формируется элементом несовпадеййя 35 и через коммутатор 32 блока 8 подается на второй вход блока б.На первый вход сумматора 5 н это время поступает с выхода регистра 1 через элемент 16 задержки, элемент 18 И и элемент 13 ИЛИ коэффициент А, ранее записанный в регистр 1. Элемент 18 И открыт, так как триггеры 10 и 12 находятся н нулевом состоянии.Сумматор 5 произведет суммирование коэффициентов А и В последовательным способом. результат суммирования с выхода сумматора 5 записынается в регистр 1.После сложения коэффициентов Аи В с выхода регистра 2 считываетсякоэффициент С, в это время с выходарегистра 3 поступает двоичный кодвеличины Х, начиная с младшего разряда, Первый разряд кода Х с выходарегистра 3 через элементы 21 И и 14ИЛИ поступает на первый вход элемента, 22 И и вход регистра 4.Если в первом. разряде величины Хзаписан единичный код, то элемент22 И срабатывает и установит триггер 11 н единичное состояние.15 Коэффициент С с выхода регистра2 через элемент 19 И, открытый прямым выходом триггера 11, и блок 6поступает в прямом или дополнительном коде в зависимости от знакаЩ величины Х, на первый вход сум-.матора 5. Код знака величины Хсчитывается с первого разряда реги"стра 31 и с помощью коммутатора 32блока 8 знака подключается к второму входу блока б.Таким образом, на первый входсумматора 5 поступает пРямой илидополнительный код коэффициента С,а на его второй вход считывается свыхода регистра 1 через элемент 16задержки, элемент 18 И и элемент13 ИЛИ двоичный код предыдущей суммы коэффициентов А и В.Сумматор 5 выполняет сложениедвоичных кодов коэффициентов С, А+Ви результат сложения записывается врегистр 1.После этого.на пятом выходе 46блока 9 синхронизации вырабатывается импульс, который пройдет через 40 элемент 25 И, открытый сигналом инверсного выхода триггера 12, на прямой вход триггера 10 и установит егон единичное состояние.Переход триггера 10 в единичное 45 состояние приводит к подключению выхода регистра 1 с помощью элемента17 И, открытого сигналом прямого выхода триггера 10, и элемента 13 ИЛИ,к второму входу сумматора 5, При ур этом, элемент 18 И закрыт сигналоминверсного выхода триггера 10, обеспечивая стираниес младшего. разрядасуммы коэффициентов.Подключение выхода регистра 1 квторому входу сумматора приводит ксдвигу информации в регистре 1 наодин разряд н сторону младших разрядов по отношению к синхронизирующим импульсам четвертого выхода 45блока 9 синхронизации. В результате бО сдвига информация н регистре 1, который содержит п - 1 разряд, с синхронизирующим импульсом первого разряда на четвертом выходе 45 блока 9синхронизации совпадает второй разряд 65 суммы коэффициентов, записанной в регистре 1. В случае сдвига на один разряд в регистре 1 дополнительного кода, накопленной суммы коэффициентов,знаковый разряд сцвигается в п -1 разряд по правилу сцвига дополнительного кода и перезаписывается с выхода регистра 1 через элемент 16 задержки, элементы 18 И и 13 ИЛИ, сумматор 5 на вход регистра 1 по мес ту и-го разряда. Триггер 10 в это время устанавливается в нулевое состояние сигналом первого выхода 43 блока 9 синхронизации, обеспечивая восстановление в и-ом разряде единичного кода знака, В регистре 2, который содержит Зп разрядов, сдвиг информации относительно синхронизирующих импульсов блока 9 синхронизации отсутствует.Таким образом, сдвиг информации в регистре 1 на один разряд обеспечивает умножение на два,суммы коэффициентов. Сдвиг информации на один разряд в регистре, состоящем из регистров 3 и 4, обеспечивает совпадение с первыми разрядами коэффициентов А, В и С следующих вторых разрядов соответствующих величин Уо, Хо и Х 1Второй разряд величины Уо считывается с выхода регистра 3 и через элементы 21 И и 14 ИЛИ поступает на первый вхоц элемента 22 И, на втс рой вход которого с четвертого выхода блока 9 синхронизации поступает синхронизирующий импульс первого разряда коэффициентов А, В и С.Если во втором разряде величины У записан единичный код, то элемент 22 И срабатывает, устанавливая триггер 11 в единичное состояние. Элемент 19 И открывается сигналом прямого выхода триггера 11, Двоичный код коэффициента А с выхода регистра 2 через элемент 19 И поступает на первый вход блока б дополнительного кода, на второй вход которого с выхода. блока 8 подается сигнал знака величины УПрямой или дополнительный код коэффициента А с выхода блока б подается на первый вход сумматора 5, на второй вход которого через элементы 13 ИЛИ и 18 И, открытый сигналом прямого выхода триггера 10, с выхода регистра 1 поступает, начиная с второго разряда, накоплен- ная в результате предыдущих вычислений сумма коэффициентов А, В и ССумматор 5 выполняет суммирование, а результат записывается в регистр 1, после чего триггер 10 сбрасывается в нулевое состояние синхронизирующим сигналом первого выхода 43 блока 9 синхронизации.Переход триггера 10 в нулевое состояние обеспечивает дополнение регистра 1, имеющего празряд, до п - разрядов с помощью элемен- о та 16 задержки и элемента 18 Доткрытого сигналом инверсного выхода триггера 10. Элемент 17 И закрывается сигналом прямого выхода триггера 10, обеспечивая отключение выхода регистра 1 от второго входа сумматора 5.Дополнение регистра 1 до и разрядов обеспечивает отсутствие сдвига информации в регистре 1 до следующего синхрониэирующего импульсана пятом выходе 46 блока 9 синхронизации, который сформируетсяспустя время Зп/Г. За это времясумматор выполнит сложение произведений, коэффициентов А, В и С на соответствующие двоичные переменныевторых разрядов величины У , ХХо ф о1После генерации импульса на пятом пыходе 46 блока 9 синхронизациипроизойдет сдвиг информации на одинразряд в регистре 1 и регистре, образованном регистрами 3 и 4, также,как ранее описанО.Сумматор 5 осуществит сложение . произведений коэффициентовА, В и С на соответствующиедвоичные переменные третьихразрчдов величин Уо , Х и Х и т.д.одо тех пор, пока на втором выходе44 блока 9 синхронизации не вырабатывается выходной импульс, который сформируется спустя интервалвремени Зп /Г после пуска устройастваЗа это время в регистре 1, дополненном элементом 16 задержки до иразрядов, накапливаются старшие празрядов выходной величины У согласно соотношению (2) , которыебудут служить начальными условиямидля следующего цикла вычислений.В регистре, образованном объединением регистра 3 и 4 за время Зп/1произойдет сдвиг информации нап-разрядов, в результате которогодвоичный коц величины Х сдвинетсяна место двЬичного кода начальныхусловий Хо,Таким образом, вместо начальногоусловия УО в регистре 1 образовался двоичный код нового значениявыходной величины У ., В группе имладших разрядов регистра 3 сдвигомвместо начального условия Х полуочен двоичный код входной величиныХна первом цикле вычислений, Триггеры 10, 11 и 12 находятся в нулевом состоянии. Один цикл вычисленийзавершился и устройство вернулосьв исходное состояние, но с новымизначениями начальных условий. В про 1.цессе вычислений .интегро-дифферейциальный вычислитель будет работатьаналогичным образом.Например второй цикл вычисленияначнется с момента генерации второго импульса на втором выходе 44блока 9 синхронизации, который установит триггер 12 в единичное состояние и, воздействуя на шину сдвига регистра 31, сдвинет знак входной величины,Х во второй разрядрегистра 31, а в его первый разрядзапишет знак входной величины Х.Кроме этого, импульс синхронизации со второго выхода 43 блока 9 синхронизации поступит на первый входэлемента 36 И блока 8.Если в результате вычислений выходная величинаУ 1 изменит знак, то в регистре 1образуется дополнительный код старших разрядов выходной величины и ви-ом знаковом разряде появится сиг-.нал единичного кода, который с выхо,да сумматора 5 поступает на второйвход элемента 36 И блока знака. Срабатывание элемента 36 И приводит кпереходу триггера 34, который приположительном знаке выходной величины находился в нулевом состоянии,в единичное состояние, соответствующее отрицательному знаку выходной.величины.Триггер 12 в единичном состоянии осуществляет блокировку сдвигав регистре 1 следующим образом.Сигнал с инверсного выхода триггера 12 закрывает элемент 25 И,запрещая установку триггера 10 вединичное состояние. Поэтому вовремя нахождения триггера 12 в единичном состоянии регистр 1 дополняется элементом 16 задержки до и-разрядов и старшие п разрядоввычисленной величины У с выходаэлемента 16 задержки поступают через блок 7, элемент ЯО, открытыйсигналом прямого выхода триггера12, и элемент 14 ИЛИ в виде прямого кода абсолютной величины У 1 на вход регистра 4 и первый вход элемента 22 И.Двоичный код абсолютной величины входа Х на втором цикле вычислений записывается последовательным способом с входной шины 27 в стар" шие и разрядов регистра 3, в котором в это.время двоичный код входа Х на первом цикле вычислений сдвигается из и старших в и младшие разряды регистра 3Двоичный код начального условия входа Х сдвигается из и-младших разрядов регистраф 3 на его выход и стирается, так как элемент 21 И закрыт сигналом инверсного выхода триггера 12, который блокирует также элемент 1 И, запрещая перезапись старших разрядов величины У с выхода элемента 16 задержки через сумматор 5 на вход регистра 1, выпол няя этим очистку регистра,1.Таким образом, в интегро-дифферен циальном вычислителе записывается новая Х, Х; , У,"информация, исходная для следующего -го цикла вычислений, и стирается Х, , У-.информация, использованная в предыдущем (-1)-м цикле вычислений. Реализация требуемого интегро-дифференциального преобразования в последующих 1+1 циклах выполняется такжекак и в описанном первом цикле присоответствующих новых начальных ус"ловИях.Следуем отметить, что интегродифференциальный вычислитель можноприменять для линейных интегро- .дифференциальных преобразований любого порядка и по любой зависймойвходной переменной Х,Чтобы осуществить интегро-диффе15 ренциальное преобразование высокогопорядка нужно представить ее в видепроизведения элементарных передаточных функций (таблица), .рассчитать их параметры, соединить посщ ледовательно ряд одинаковых интегродифференциальных вычислителей в общем случае с различными начальнымиусловиями и коэффициентами А, В и СВ этом случае выходные шины 28 и 29каждого предыдущего интегро-дифференциального вычислителя подключаютсясоответственно к входным шинам 26 и27 последующего интегро-дифференциального. вычислителя. Причемсинхро-низация работы всего ряда из нескольких одинаковых интегро-дифференциальных вычислителей, реализующих каждый свою специфическую передаточную функцию, осуществляется отодного и того же блока 9 синхрони 35 зации и следовательно в этом случаене требуется дополнительных затратоборудования.На базе унифицированных интегродифференциальных вычислителей мож 4 О но реализовать любые другие сложные,последовательно-параллельные схемыдискретного управления и комплексного моделирования динамическихобъектов,Технико- экономические преимущества интегро-дифференциальноговычислителя по сравнению с известным заключаются в простоте реализации и повышении быстродействия.Формула изобретенияИнтегро-дифференциальный вычислитель, содержащий блок синхронизации, регистры, сумматор, блоки Формирования дополнительного кода, блокхранения знака, триггеры, элементыИ, ИЛИ и элемент задержки, причемвход первого регистра подключен кЯ выходу сумматора и первому входублока хранения знака, второй вход которого подключен к первому входувычислителя, первый вход сумматорасоединен с выходом первого блокаформирования дополнительного кода,второй вход сумматора подключен квыходу первого элемента ИЛИ, входыкоторого подключены соответственнок выходам первого и второго элементов И, первые входы которых подключены соответственно к прямомуи инверсному выходам первого триггера, выход первого регистра подключен ко второму входу первого элемента И, первый выход блока синхрониза-ции подключен к инверсным входампервого, второго и третьего триггеров, второй выход - к третьему входу блока хранения знака, группа выходов, - к группе входов блока хранения знака, о т л и ч а ю щ и йс я тем, что, с целью упрощениявычислителя и повышения его быстродействиА, второй вход второгоэлемента И подключен к первому входу второго блока формирования дополнительного кода непосредственно ичерез элемент задержки - к выходупервого регистра,.первый вход первого блока формирования дополнительного кода подключен к выходу третьего элемента И, первый вход которого подключен к выходу второгорегистра, второй вход - к прямомувыходу второго триггера, вторыевходы первого и второго блоковформирования дополнительногО кодаподключены к выходу блока хранения знака и к первому выхоцу вычислителя, выход второго блока формирования дополнительного кода подключен к первому входу четвертогоэлемента И, выход третьего регистраподключен к первому входу пятогоэлемента И, входы второго элементаИЛИ подключены соответственно к выходам четвертого и пятого элементов И, вход четвертого регистраподключен к выходу второго элементаИЛИ и к первому входу шестого элемента И, второй вход которого подключен к третьему выходу блока сихронизации, а выход - к прямомувходу второго триггера, входы третьего элемента ИЛИ подключены соответственно к выходам седьмого и восьмого элементов И, выход третЬегоэлемента ИЛИ соединен с входом третьего регистра, первый вход седьмого элемента И подключен ко второму входу вычислителя, второй вход -к прямоМу выходу третьего триггера,15 инверсный выход которогосоединенс третьим входом второго элементаИ, вторым входом пятого элементаИ и первыми входами восьмого и девятого элементов И, второй вход2 О восьмого элемента И подключен к выходу четвертого реГистра, прямойвход третьего триггера соединен свторым выходом блока синхронизациичетвертый выход которого подклю 25 чен ко второму входу девятого элемента И, выход которого соединен спрямым входом первого триггера,второй выход вычислителя соединенс выходом четвертого элемента И.Источники информации,принятые во внимание при экспертизе1. Вычислительная техника. Справочник под ред. Г.Д. Хасин иГ.А, Корка, т. 1. М-Л., "Энергия",1964, с. 63-71.2. Неслуховский К.С. Цифровые диф: ференциальные анализаторы. М., "Машиностроение", 1968, с. 84, рис. 15

СмотретьЗаявка

2715995, 22.01.1979

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕ-ТИКИ AH УКРАИНСКОЙ CCP, ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АНУКРАИНСКОЙ CCP

БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ, БАРАНОВ ГЕОРГИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: вычис-литель, интегро-дифференциальный

Опубликовано: 23.01.1981

Код ссылки

<a href="https://patents.su/10-798902-integro-differencialnyjj-vychis-litel.html" target="_blank" rel="follow" title="База патентов СССР">Интегро-дифференциальный вычис-литель</a>

Предыдущий патент: Интегрирующее устройство

Следующий патент: Аналого-цифровой функциональныйпреобразователь

Случайный патент: Способ внутриартериальной инфузиилекарственных веществ b правоелегкое