Интегро-дифференциальный вычислитель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 960813

Автор: Баранов

Текст

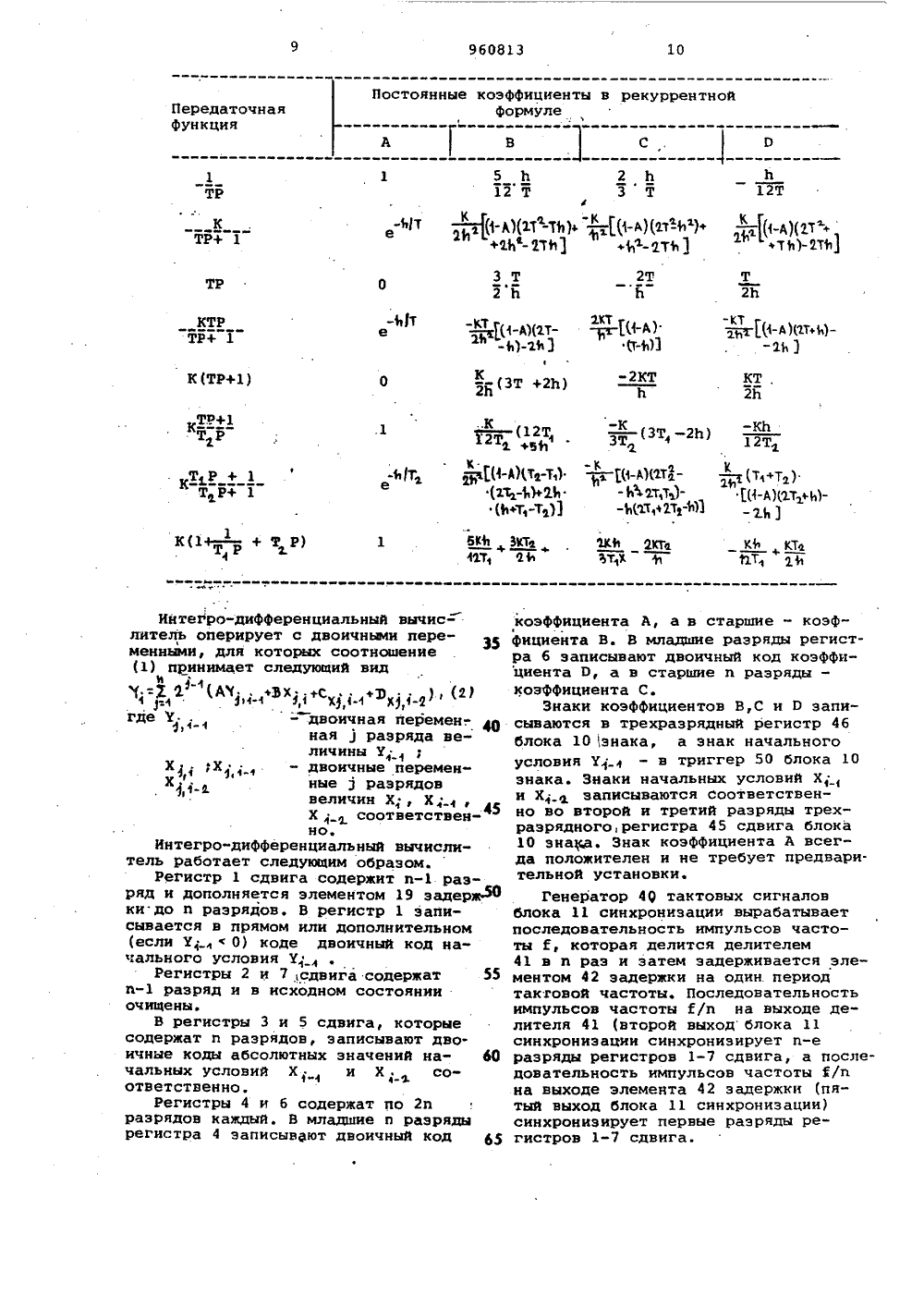

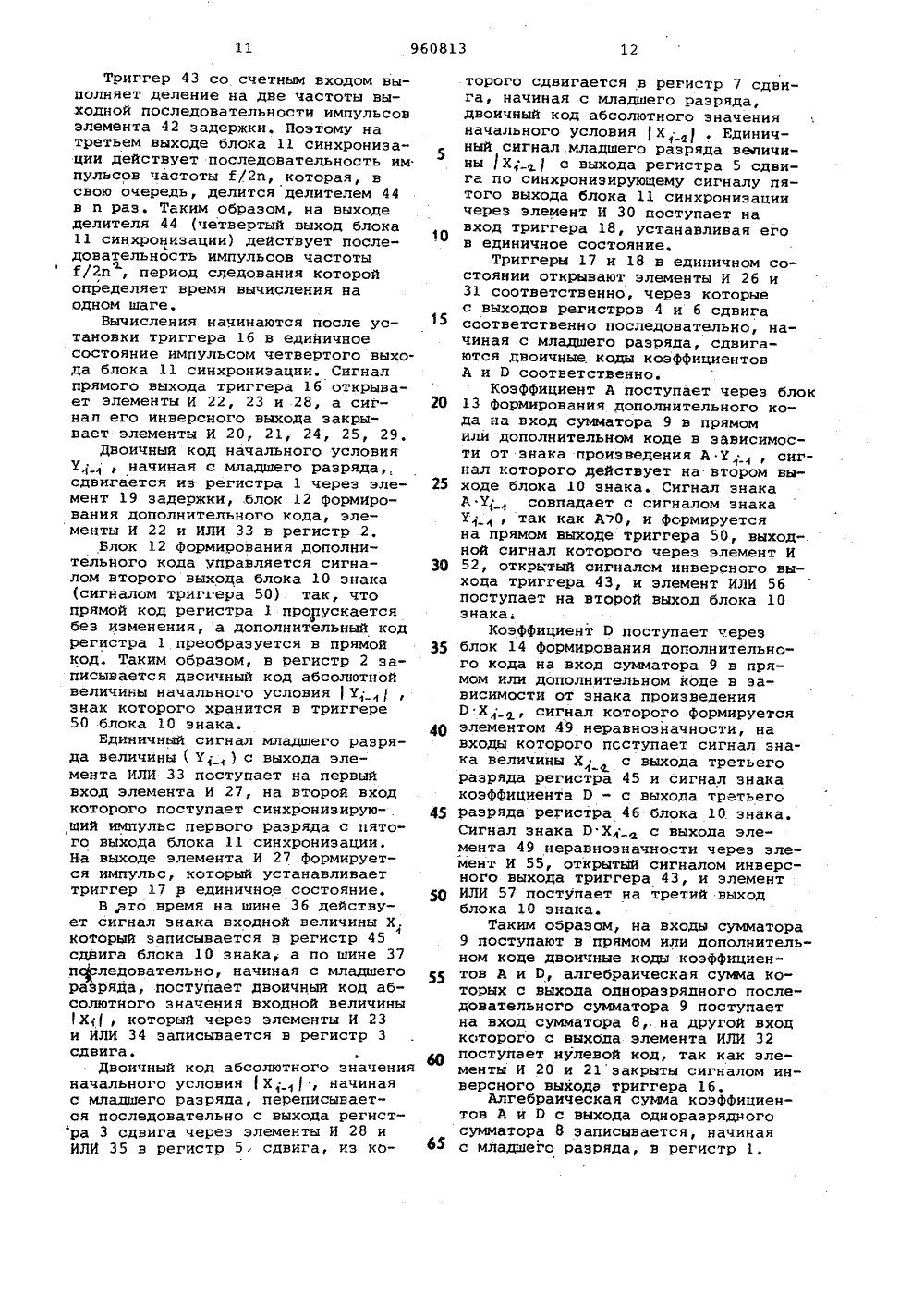

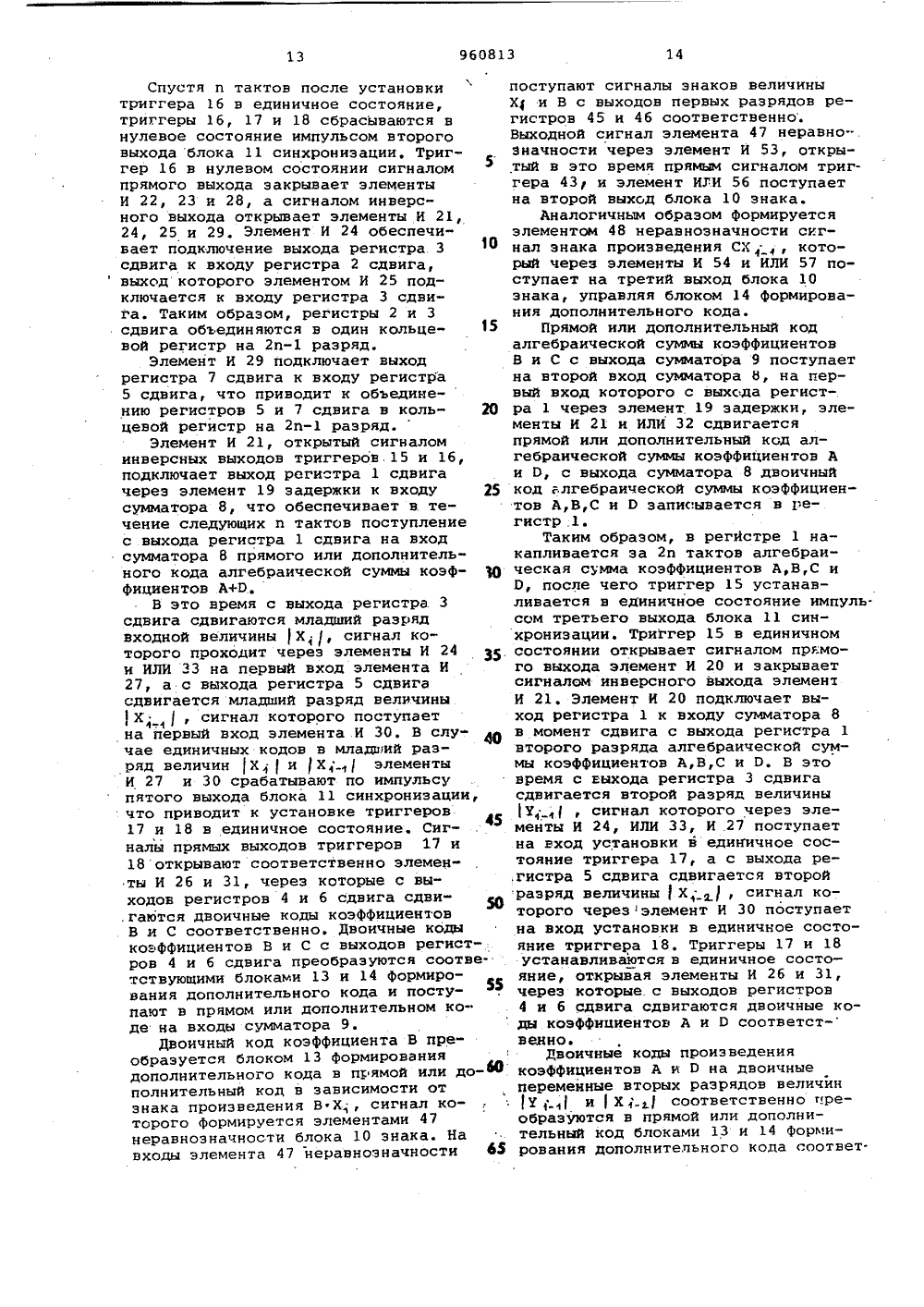

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУе Союз СоветскихСоциалистическихРеспублик оц 960813(23) Приоритет С 06 Р 7/64 Государственный комитет СССР по делам изобретений и открытий(088. 8) Опубликовано 230982. Бюллетень Мо 35 Дата опубликования описания 23.09.82(72) Авторыизобретения Г,Л.Баранов и В.Л.Бараисв а, 4ВИнститут электродинамики АН Украинской ССР и ОрденаЛенина институт кибернетики АН Украинской ССРУ(54) ИНТЕГРО-ДИФФЕРЕНЦИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ Изобретение относится к автоматыке и вычислительной технике и можетбыть использовано для моделированияи управления динамическими объектами.в различных отраслях промышленности.Известны точные цифровые интегро дифференциальные устройства типа дифференциальных анализаторов, которыесодержат ряд цифровых интеграторов,коммутируемых между собой согласнозаданному интегро-дифференциальномупреобразователю 11,Недостатками таких интегро-дифференциальных устройств являютсянизкое быстродействие и сложностьреализации.Наиболее близким к данному техническому решению является интегродифференциальный вычислитель, содержаший четыре регистра, первый сумматор, два блока формирований дополнительного кода, блок знака, блок синхронизации, восемь элементов И, триэлемента ИЛИ и элемент задержки, при.чем первая входная шина устройствасоединена с первым входом блоказнака, первый, выход которого соединен с первой выходной шиной устройства, выход первого сумматора соединен с входом первого регИстра и вторым входом блока знака, второй выход которого соединен с первыми входами первого и второго блоков формирования дополнительного кода, блОк синхронизации соединен первым выходом с третьим входом блока знака, вторым выходом - с первыми входами первого, второго и третьего триггеров, третьим выходом - с вторым входом первого триггера и четвертым выходом - с вторым входом второго триггера, выход первого регистра сое динен с входом элемента задержки и с первым входом первого элемента И, выход и второй вход которого соединены соответственно с первым входом первого элемента ИЛИ и с прямым выходом первого триггера, выход элемента задержки соединен с вторым входом первого блока формирования дополнительного кода и с первым входом второго элемента И, второй вход и выход которого соединены соответственно с инверсным выходом первого триггера и с вторым входом первого элемента ИЛИ, выход которого подключен к первому входу первого сумматора, второй триггер .соединен прямым выходом с первыми входами третьего и четвертого элементов Иродействия и точности вычислений,в него введены пятый, шестой и седьмой регистры сдвига, второй сумматор, третий блок формирования дополнительного кода, четвертый триггер,девятый, десятый, одинадцатый и двенадцатый элементы И и четвертый элемент ИЛИ, причем вход пятого регистра сдвига соединен с выходом четвертого элемента ИЛИ, первый и второйвходы которого соединены соответственно с вьбсодами девятого и десятогоэлементов И, первый и второй входыдевятого элемента И соединены соответственно с выходом третьего регистра сдвига и прямым выходом; второго 15триггера, выход пятого регистра сдвига соединен с первым входом одиннадцатого элемента И, второй вход которого соединен с пятым выходом блокасинхронизации, а выход " с первым 20входом четвертого триггера, второйвход которого соединен с вторым выходом блока синхронизации, а прямойвыход - с первым входом двенадцатогоэлемента И, второй вход которого сое 25 динен с выходом шестого регистрасдвига, а выход - с первым входомблока формирования дополнительногокода, второй вход которого соединенс третьим выходом блока знака, авыход - с.первым входом второгосумматора, второй вход которого соединен с выходом второго блока формирования дополнительного кода, авыход - с вторым входом первого сумматора, вход седьмого регистра сдвига соединен с выходом пятого регистра сдвига, первый и второй входыдесятого элемента И соединены соответственно с инверсным выходом второго триггера и выходом седьмогорегистра сдвига.Источники информации,принятые,во внимание при экспертизе1, Неслуховский К.С. Цифровые.дифФеренциальные анализаторы. И.,Машиностроение, 1968, с.84 и196, рис, 15 и 20,2. Авторское свидетельство СССР.по заявке У 2715995/18-24,кл. О 06,Х 1/02, 220179 (прототип),960813 Составитель В.ЛатышРедактор А.Шишкина Техред М.Тепер КорректорВ.Бутяга Заказ 72 писно 4/5 илиал ППП Патент, г. Ужгород, ул. Проектная,/59ВНИИПИ Госпо дела113035, Мо Тираж 731дартсвенного кизобретений иква, Ж, Рауш итета СССткрытийкая наб.и инверсным выходом - с первыми входами пятого и,нестого элементов Ии с третьими входами перного и второго элементов И, выход первого блока формирования дополнительного кода соединен с второй выходной шинойустройства и с вторым входом третьего элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход и выход которого 1 Осоединены соответственно с ныходомпятого элемента И и с входом второгорегистра, второй вход и выход четвертого элемента И соединены соответственно с второй входной шиной устройства и с первым входом третьего элемента ИЛИ, второй вход и выход шестогоэлемента И соединены соответственнос выходом второго регистра и с вторымвходом третьего элемента ИЛИ, выходкоторого соединен с входом третьего Юрегистра, который подключен выходомк второму входу пятого элемента И,выход четвертого регистра соединенс первым входом седьмого элемента И,выход и второй вход которого соедине ны соответственно с вторым входомвторого блока формирования дополнительного кода и с выходом третьеготриггера, нторой вход которого подключен к выходу восьмого элемента И, 30который соединен первым и вторымвходами соответственно с выходомвторого элемента ИЛИ и с пятымвыходом блока синхронизации 2.Однако известное устройство имеет уотносительно низкое быстродействиеи недостаточную точность при заданном шаге вычислений,Целью изобретения является понышение быстродействия устройства иточности вычисленийПоставленная цель достигаетсятем, что в интегро-дифференциальныйвычислитель, содержащий первый, второй, третий и четвертый регистрысдвига, первый сумматор, блок знака,блок синхронизации, первый и второйблоки формирования дополнительногокода, первый, второй и третий триггеры элемент задержки, первый, второй, третиФ, четвертый, пятый, шестой, седьмой и восьмой элементы И,первый, второй и третий элементыИДИ, причем вход первого регистрасдвига соединен с выходом перногосумматора, первый вход которого сое.динен с выходом первого элементаИЛИ, первый вход которого соединенс выходом первого элемента И, а второй - с выходом второго элемента И,первый вход первого элемента И соединен с выходом первого регистрасдвига и входом элемента задержки,второй вход первого элемента И соединен с прямым выходом первого триггера, первый вход второго элемента И 65 соединен с выходом элемента задержки, а второй - с инверсным выходомпервого триггера, третий вход первого элемента И соединен с третьимвходом нторого элемента И, первыйвход первого блока формирования дополнительного кода соединен с первымвходом второго блока формированиядополнительного кода, а второй - свыходом элемента задержки., первыйвход третьего элемента И соединенс первым входом четвертого элементаИ и прямым выходом второго триггера,первый нход которого соединен спервыми входами первого и третьеготриггеров, второй вход третьего элемента И соединен с выходом первогоблока формирования дополнительногокода, первый вход блоха знака является первым входом устройства,второй вход четвертого элемента Иявляется вторым входом устройства,первый выход блока знака является первым выходом устройства, выход первого блока формирования дополнительного кода является вторым выходом устройства, первый вход пятого элемента И соединен с третьим входом первого элемента И, с первым входом шестого элемента И и с инверсным выходом второго триггера, выход третьего элемента И соединен с первым входом второго элемента ИЛИ второйвход которого соединен с выходомпятого элемента И, выход второго элемента ИЛИ соединен с входом нторогорегистра сдвига, выход которого соединен с вторым входом шестого элемента И, выход четвертого элементаИ соединен с первым входом третьего элемента ИЛИ, второй нход которого соединен с выходом шестого элемента И, выход третьего элементаИЛИ соединен с входом третьего регистра сдвига, выход которого соединенс вторым входом пятого элемента И,выход четвертого регистра сдвигасоединен с первым входом седьмогоэлемента И, второй вход которого "оединен с прямым выходом третьего триггера, второй вход которого соединен с выходом восьмого элемента И,первый вход которого соединен с выходом второго элемента ИЛИ, выходседьмого элемента И соединен с вторым входом второго блока формирования дополнительного кода, второй входблока знака соединен с выходом сумматора, а третий - с первым выходомблока синхронизации, второй выходблока знака соединен с первым ьходомпервого блока формирования дополнительного кода, второй, третий четвертый и пятый выходы блока синхронизации соединены соответственно с первым и вторым входами первого триггера, вторыми входами второго триггераи восьмого элемента И, введены пятый,шестой и седьмой регистры сдвига,второй сумматор, третий блок формирования дополнительного кода, четвертый триггер, девятый, десятый, одинадцатый и двенадцатый элементы И и,четвертый элемент ИЛИ, причем входпятого регистра сдвига соединен с выодом четвертого элемента ИЛИ, перый и второй входы которого соединены соответственно с выходами девятого и десятого элементов И, первый ивторой входы девятого элемента Исоединены соответственно с выходомтретьего регистра сдвига и:прямымивыходом второго триггера, выход пятого регистра сдвига соединен с первымвходом одинадцатого элемента И, второй вход которого соединен с пятымвыходом блока синхронизации, а выход - с первым входом четвертого триггера, второй вход которого соединенс вторым выходом блока синхронизации, а прямой выход - с первым входом двенадцатого элемента И, второйвход которого соединен с выходомшестого регистра сдвига, а выход "с первым входом блока формированиядополнительного кода, второй входкоторого соединен с третьим выходомблока знака, а выход - с первым вхо- ЗОдом второго сумматора, второй входкоторого соединен с выходом второгоблока Формирования дополнительногокод-, а выход - с вторым входом первого сумматора, вход седьмого регистра сдвига соединен с выходомпятого регистра сдвига, первый и второй входы десятого элемента И соединены соответственно с инверсным выходом второго триггера и выходом седьмого регистра сдвига.На фиг,1 изображена структурнаясхема интегро-дифференциального вычислителяна фиг.2 - структурныесхемы блока знака и блока синхронизации.Интегро-дифференциальный вычислитель фиг,1) содержит семь регистров 1-7 сдвига, два сумматора 8 и 9,блок 10 знака, блок 11 синхронизации, 5 Отри блока 12-14 формирования дополкительного кода, четыре триггера 1518, элемент 19 задержки, двенадцатьэлментов И 20-31,. четыре элементаИЛИ 32-35, две входные шины 36 и 37и две выходные шины 38 и 39 устройства,Вход регистра 1 соединен с выходом;умматора 8 первый и второй входыкоторого подключены соответственнок выходу элемента ИЛИ 32 и к выходусумматора 9. Блок 10 знака соединенпервым входом с первой входной шиной 36 устройства, вторым входом -с выходом сумматора 8, третьим входом - с первым выходом блока 11 синхронизации, первым выходом - с пер вой выходной шиной 38 устройства и вторым выходом - с первыми входами блоков формирования дополнительного кода 12 и 14.Входы сумматора 9 подключены к выходам блоков 13 и 14 формирования дополнительного кода, Блок 11 синхронизации соединен вторым выходом с первыми входами триггеров 15-17, третьим выходом - с вторым входом триггера 15, четвертым выходом - с вторым входом триггера 16 и пятым выходом - с вторыми входами элементов И 27 и 30, первые входы которых соединены соответственно с выходом элемента ИЛИ 33 и с выходом регистра 5. Второй вход триггера 17 соединен с выходом элемента И 27. Триггер 18 соединен первым и вторым входами соответственно с выходом элемента И 30 и вторым выходом блока 11 синхронизации. Выход регистра 1 соединен с входом элемента 19 задержки и первым входом элемента И 20, второй вход и выход которого соединены соответственно с прямым выходом триггера 15 и с первым входом элемента ИЛИ 32, второй вход которого соединен с выходом элемента И 21, первый вход которого соединен с выходом элемента 19 задержки и вторым входом блока 12 формирования дополнительного кода. Инверсный выход триггера 15 соединен с вторым входом элементов И 21, третий вход которого соединен с третьим входом элемента И 20, с первыми входами элементов И 24, 25 и 29 и инверсным выходом триггера 16, прямой выход которого соединен с первыми входами элементов И 22 и 23. Выход блока 12 формирования дополнительного кода соединен с второй выходной шиной 39 устройства и с вторым входом элемента И 22, выход которого соединен с первым входом элемента ИЛИ 33,; выход и второй вход которого соединены соответственно с выходом регистра 2 и с выходом элемента И 24, второй вход которого соединен с первым входом элемента И 28 и выходом регистра 3 сдвига. Второй вход и выход элемента И 23 соединены соответственно с второй входной шиной 37 устройства и с первым входом элемента ИЛИ 34, выход и второй вход которого соединены соответственно с входом регистра 3 и с выходом элемента И 25, второй вход которого подключен к выходу регистра 2 сдвига.Выход регистра 4 сдвига соединен с первым входом элемента И 26, выход и второй вход которого соединены соответственно с вторым вхо-дом блока 13 формирования лополни960813 50 тельного кода и с выходом триггера17, Выход триггера 18 соединен с первым входом элемента И 31, второйвход и выход которого соединенысоответственно с выходом регистра бсдвига и с первым входом блока 14формирования дополнительного кода,второй вход которого подключен ктретьему выходу блока 10 знака.Второй вход и выход элемента И 28соединены соответственно с прямым 1 Овыходом триггера 16 и с первым входом элемента ИЛИ 35, второй вход ивыкод которого соединены соответственно с выходом элемента И 29 и свходом регистра 5 сдвига, выход которого соединен с входом регистра 7сдвига, выход которого подключен квторому входу элемента И 29.Блок 11 синхронизации (фиг,2) содержит генератор 40 тактовых сигна- флов, делитель 41, элемент 42 задержки, триггер 43 со счетным входом иделитель 44. Блок 10 знака (фиг,2)содержит трехразрядный регистр 45сдвига, трехразрядный регистр 46,три элемента 47-49 неравнозначности, триггер 50, пять элементов И51-55, дна элемента ИЛИ 56 и 57,две входные шины 36 и 58, три выходные шины 38, 59 и 60. Блок 11 синхро низации имеет выходные шины 61-64.Выход генератора 40 тактовых сигналон соединен с входом делителя 41,выход которого соединен с выходнойшиной 61 и с входом элемента 42 задержки выход которого подключен квыходкой шине 62 и к счетному входутриггера 43, выход которого соединенс выходной шиной 63 и с входом делителя 44, ныход которого соединен с 4 Овыходной шиной 64, с шиной сдвигарегистра 45 и с первым входом элемента И 51, второй вход и ныход которогосоединены соответственно с входнойшиной 58 и с входом триггера 50, 45выход которого соединен с выходнойшиной 38 н с первым входом элементаИ 52, выход которого соединен с первым входом элемента ИЛИ 56, выходкоторого подключен к ВыхОднОЙ шине 59,Входная шина 36 соединена с информационны входом регистра 45 сдвига, три выхода которого подключенысоответственно к первым входам элементов 47-49 неравнозначности, вторые нходы которых соединены с соответствуюшими выходами регистра 46. Выходы элементов 47-49 неравнозначности соединены соотнетственно с первыми входами элементов И 53-55, Вторые входы элементов И 53-54 соединены с прямым выходом триггера 43, инверсный выход которого соединен с вторыми входами элементов И 52 и 55. Второй вход элемента ЯЛИ 56 соединен с выходом элемента И 53. Выходы элементов И 54 и 55 соединены с нходами элемента ИЛИ 57, выход которого подключен к выходной шине 60.Первым и вторым входами блока 10 знака являются шины 36 и 58 соответственно. Первым, вторым и третьим выходами блока 10 знака являются шины 38, 59 и 60 соответственно. Вторым, третьим, четвертым и пятым выходами блока 11 синхронизации являются шины 61, 63, 64 и 62 соответственно.Интегродифференциальный вычислитель для каждого 1-го цикла отрабатывает рекуррентное соотношениеУ 1 =АУ, +Вх +Сх,+Рх . (1) где У и У;- значения выходной величины состветственно на 1 и1-1 шаге вычислений;Х ;Х ;Х - значения входнойвеличины соответственно на 1 1-1и 1-2 шаге вычислений;А, В, С, Р - постоянные коэфФициенты, значения которых зависят от шага понезависимой переменной и вида реа.лизуемого интегродифференциальногопреобразования.Настройка вычислителя осуществляется заданием постоянных коэффициентов А,В,С,Р и начальных условийХи Х , Предварительный расчет постоянных коэффициентов А,В,С,Р для часто реализуемых видов интегро-дифференциальных преобразователей выполняют о формулам, приведенным в таблице, где К - коэфФициент условия; Т, Т , Т -постоянные времени; Ь - шаг последователь. ного преобразования входной величины Х в выходную У, который выбирается из условия заданной точности, 960813 12Триггер 43 со счетным входом выполняет деление на две частоты выходной последовательности импульсовэлемента 42 задержки. Поэтому натретьем выходе блока 11 синхронизации действует последовательность импульсов частоты й/2 п, которая, всвою очередь, делится делителем 44в и раз. Таким образом, на выходеделителя 44 (четвертый выход блока11 синхронизации) действует последовательность импульсов частотый/2 п , период следования которойопределяет время вычисления наодном шаге,Вычисления начинаются после установки триггера 16 в единичноесостояние импульсом четвертого выхода блока 11 синхронизации. Сигналпрямого выхода триггера 16 открывает элементы И 22, 23 и 28, а сигнал его.инверсного выхода закрывает элементы И 20, 21, 24, 25, 29,Двоичный код начального условияУ , начиная с младшего разрядасдвигается иэ регистра 1 через элемент 19 задержки, .блок 12 формирования дополнительного кода, элементы И 22 и ИЛИ 33 в регистр 2,Елок 12 формирования дополнительного кода управляется сигналом второго выхода блока 10 знака(сигналом триггера 50). так, чтопрямой код регистра 1 прорускаетсябез изменения, а дополнительный кодрегистра 1 преобразуется в прямойкод. Таким образом, в регистр 2 записывается двоичный код абсолютнойвеличины начального условияУ;знак которого хранится в триггере50 блока 10 знака.Единичный сигнал младшего разряда величины ( У; ) с,выхода элемента ИЛИ 33 поступает на первыйвход элемента И 27, на второй входкоторого поступает синхронизирую-.ший ю(пульс первого разряда с пятого выхода блока 11 синхронизации.На выходе элемента И 27 формируется импульс, который устанавливаеттриггер 17 в единичное состояние.В рто время на шине 36 действует сигнал знака входной величины Х.который записывается в регистр 45сдвига блока 10 знака, а по шине 37последовательно, начиная с младшегоразряда, поступает двоичный код абсолютного значения входной величиныХ(, который через элементы И 23и ИЛИ 34 записывается в регистр 3сдвига.Двоичный код абсолютного значенияначального условия ( Х; , начинаяс младшего разряда, переписывается последовательно с выхода регистра 3 сдвига через элементы И 28 иИЛИ 35 в регистр 5. сдвига, из ко 5 10 15 20 25 ЗО 35 40 45 50 55 60 65 торого сдвигается в регистр 7 сдвига, начиная с младшего разряда, двоичный код абсолютного значения начального условияХ. Единичный сигнал. младшего разряда вьпичины (Х / с выхода регистра 5 сдвига по синхронизирующему сигналу пятого выхода блока 11 синхронизации через элемент И 30 поступает на вход триггера 18, устанавливая его в единичное состояние.Триггеры 17 и 18 в единичном состоянии открывают элементы И 26 и 31 соответственно, через которые с выходов регистров 4 и 6 сдвига соответственно последовательно, начиная с младшего разряда, сдвигаются двоичные, коды коэфФициентов А и П соответственно.КоэФФициент А поступает через блок 13 формирования дополнительного кода на вход сумматора 9 в прямом или дополнительном коде в зависимости от знака произведения А У , сигнал которого действует на втором выходе блока 10 знака. Сигнал знака А Усовпадает с сигналом знака У , так как А)0, и фсрмируется на прямом выходе триггера 50, выходной сигнал которого через элемент И 52, открьтый сигналом инверсного выхода триггера 43, и элемент ИЛИ 56 поступает на второй выход блока 10 знака.Коэффициент П поступает через блок 14 формирования дополнительного кода на вход сумматора 9 в прямом или дополнительном коде в зависимости от знака произведения П Х , сигнал которого формируется элементом 49 неравнозначности, на входы которого псступает сигнал знака величины Х с выхода третьего разряда регистра 45 и сигнал знака коэффициента Р - с выхода третьего разряда регистра 46 блока 10. знака. Сигнал знака Р Х с выхода элемента 49 неравнозначности через элемент И 55, открытый сигналом инверсного выхода триггера 43, и элемент ИЛИ 57 поступает на третий выход блока 10 знака.Таким образом, на входы сумматора 9 поступают в прямом или дополнительном коде двоичные коды коэффициентов А и О, алгебраическая сумма которых с выхода одноразрядного последовательного сумматора 9 поступает на вход сумматора 8, на другой вход которого с выхода элемента ИЛИ 32 поступает нулевой код, так как элементы И 20 и 21 закрыты сигналом инверсного выхода триггера 16.Алгебраическая сумма коэффициентов А и 0 с выхода одноразрядного сумматора 8 записывается, начиная с младшего разряда, в регистр 1,Спустя и тактон после установкитриггера 16 н единичное состояние,триггеры 16, 17 и 18 сбрасываются внулевое состояние импульсом второговыхода блока 11 синхронизации, Триггер 16 в нулевом состоянии сигналомпрямого выхода закрывает элементыИ 22, 23 и 28, а сигналом инверсного выхода открывает элементы И 21,24, 25 и 29. Элемент И 24 обеспечивает подключение выхода регистра 3сдвига к входу регистра 2 сдвига,выход которого элементом И 25 подключается к входу регистра 3 сдвига. Таким образом, регистры 2 к 3сдвига объединяются в один кольцевой регистр на 2 празряд,Элемент И 29 подключает выходрегистра 7 сдвига к входу регистра5 сдвига, что приводит к объединению регистров 5 и 7 сдвига в кольценой регистр на 2 празряд.Элемент И 21, открытый сигналоминверсных выходов триггеров.15 и 16,подключает выход регистра 1 сдвигачерез элемент 19 задержки к входу 25сумматора 8, что обеспечивает в течение следующих и тактов поступлениес выхода регистра 1 сдвига на входсумматора 8 прямого или дополнительного кода алгебраической суммы коэф- Щфицкентов А+О.В это время с выхода регистра 3сдвига сдвигаются младший разрядвходной величиныХ;(, сигнал которого проходит через элементы И 24 Зи ИЛИ 33 на первый вход элемента И27, а с выхода регистра 5 сдвигасдвигается младший разряд величины) Х , скгнал которого поступаетна первый вход элемента И 30. В слу-чае единичных кодов в младший разряд величин ХиХ) элементыИ 27 и 30 срабатывают по импульсупятого выхода блока 11 синхронизации,что приводит к установке триггеров17 и 18 в единичное состояние. Сигналй прямых выходов триггеров 17 и18 открывают соответственно элементы И 26 и 31, через которые с выходов регистров 4 и б сдвига сдви.гаются двоичные коды коэффициентовВ и С соответственно. Двоичные кодыкоэффициентов В и С с выходов регистров 4 и б сдвига преобразуются соответствующими блоками 13 и 14 формирования дополнительного кода и поступают н прямом или дополнительном ко"де на входы сумматора 9.Двоичный код коэффициента В преобразуется блоком 13 формированиядополнительного кода н прямой или до-фполнительный код н зависимости отзнака произведения В Х сигнал которого Формируется элементами 47нераннозначностк блока 10 знака. Навходы элемента 47 нераннозначности 63 поступают сигналы знаков величины Х и В с выходов первых разрядов регистров 45 и 46 соответственно. Выходной сигнал элемента 47 неравно. Значности через элемент И 53, открытый в это время прямым сигналом триггера 43 р и элемент ИГИ 56 поступает на второй выход блока 10 знака.Аналогичным образом формируется элементом 48 неравнозначности сигнал знака произнедения СХ, который через элементы И 54 и ЙЛИ 57 поступает на третий выход блока 10 знака, управляя блоком 14 формирования дополнительного кода.Прямой или дополнительный код алгебраической суммы коэффициентов В и С с выхода сумматора 9 поступает на второй вход сумматора 8, на первый вход которого с выхода регистра 1 через элемент 19 задержки, элементы И 21 и ИЛИ 32 сдвигается прямой или дополнительный код алгебраической суммы коэффициентов А и О, с выхода сумматора 8 двоичный код г.лгебраической суммы коэффициентов А,В,С и О записывается в регистр 1.Таким образом, в регйстре 1 накапливается за 2 п тактов алгебраическая сумма коэффициентов А,В,С и О, после чего триггер 15 устанавливается н единичное состояние импуль. сом третьего выхода блока 11 синхронизации. Триггер 15 в единичном состоянии открывает сигналом прямого выхода элемент И 20 и закрывает сигналом инверсного выхода элемент И 21, Элемент И 20 подключает выход регистра 1 к входу сумматора 8 в момент сдвига с выхода регистра 1 второго разряда алгебраической суммы коэффициентов А,В,С и О. В это время с выхода регистра 3 сдвига сдвигается второй разряд величины У;, сигнал которого через элемейты И 24, ИЛИ 33, И .27 поступает на вход установки в единичное состояние триггера 17, а с выхода регистра 5 сдвига сдвигается второй разряд величиныХ; ), сигнал которого черезэлемент И 30 поступает на вход установки в единичное состояние триггера 18, Триггеры 17 и 18 устанавливаются в единичное состояние, открывая элементы И 26 и 31, через которые с выходов регистров 4 и б сдвига сдвигаются двоичные коды коэффициентов А и О соответственноДвоичные коды произведения коэффициентов А и О на двоичные переменные вторых разрядов величин УиХ1 соответственно преобразуются в прямой или дополнительный код блоками 13 и 14 Формирования дополнительного кода соотнет960813 происходит сдвиг выходных сигналовотносвтельно выходных импульсов блока 11 синхронизации, что приводитк совпадению (на элементах И 27, 30)с импульсом пятого выхода блока,син хронизации следующих разрядов величинУ; Х и Х; Х; а переключение триггером 15 цепи циркуляциирегистра 1 сдвига на иразряд с выхода элемента 19 задержки непосред ственно на выход регистра 1 сдвига.обеспечивает сдвиг информации в регистре 1 сдвига на один разряд.Спустя 2 п тактов после началавычислений в регистре 1 сдвига на капливаются в прямом или дополнительном коде и старших разрядов выходной величины У;, знаковый раэ"ряд которой с выхода сумматора 8поступает на второй вход (шина 58)блока 10 знака и через элемент И 51записывается в триггер 50. К этому моменту времени в регистре 3 сдви.га содержится код величины /Х,/,в регистре сдвига 5 .- / Х / , а в д 5 регистре 7 сдвига - Х;Первыйшаг вычислений в интегро-дифференциальном вычислителе заканчивается.Вычисления ва втором шаге и всехпоследукнцих шагах осуществляется ЗО аналогичным образом, но с новых начальных условий, которые формируются на предыдущем шаге вычислений.Таким образом, интегро-дифференциальный вычислитель реализует согласно соотношению (2) любую передаточную функцию, заданную в таблице. Перестройка ивтегро-дифференциального вычислителя на заданныйвид передаточной Функции выполняется заданием коэффициентов А,В,С и Ов регистрах 4 и 6 сдвига.Интегро-дифференциальный вычислитель можно использовать длялинейных интегро-дифференциальныхпреобразований любого порядка и полюбой зависимой входной переменной.Чтобы осуществить интегро-дифференциальное преобразование высокого порядка необходимо представить этопреобразование в виде произведе 50 55 ственно, затем суммируются сумматором 9, с выхода которого алгебраическая сумма коэффициентов А и 0поступает на второй вход сумматора8, начиная с младшего разряда, а напервый вход сумматора 8 с выхода регистра 1 сдвига. сдвигается суммакоэффициентов А,В,С и О, начиная совторого разряда.Таким образом, установка триггера 15 в единичное состояние приводит к сдвигу на один разряд накопленной суммы коэффициентов в регистре 1 сдвига, обеспечивая этим выполнение операции умножения на два.После окончания суммирования сумматором 8 всех разрядов, сдвигаемыхс выхода регистра 1 сдвига, с сум-.сой коэффициентов А и 0 триггер 15, сбрасывается в нулевое состояниеимпульсомвторого выхода блока 11синхронизации. Установка триггера 15в нулевое состояние обеспечиваетподключение выхода регистра 1 сдвига через элемент 19 задержки к первому входу сумматора 8, на второй входкоторого с выхода сумматора 9 поступает двоичный код алгебраическойсуммы произведения коэФФициентов Ви С ва двоичные переменные вторыхразрядов величин / Х / и /Х,/ соответственно.Действительно, спустя и тактовпосле установки триггера 15 в единичное состояние с выхода регистра3 сдвига сдвигается второй разрядвеличины Х;/, сигнал которого черезэлементы И 24, ИЛИ 33, И 27 устанавливает, в случае единичного кода,триггер 17 в единичное состояние, ас выхода регистра 5 сдвига сдвигается второй разряд Х /, сигналкоторого через элемент Й 30 устанавливает триггер 18 в единичное состояние, если во втором разряде сдвигается единичный код. С выходов регистров 4 и 6 сдвига сдвигаются черезэлементы И 26 и 31 соответственно.двоичные коды коэффициентов В и С,которые преобразуются кодами 13 и14 формирования дополнительного кода й поступают на входы сумматора 9.Сумматор 8 суммирует накопленнуюи рдвинутую на один разряд в регистре 1 сдвига сумму коэффициентов салгебраической суммой произведениякоэффициентов В и С на двоичные переменные вторых разрядов величинХ 1/ и /Х( соответственно и результат сдвигается в регистр 1 сдвига.Дальнейшие вычисления в интегродифференциальном вычислителе выполняются,аналогичным образом. Каждые 2 п такта в кольцевых регистрах на 2 празряд, образованных объединением регистров 2 с 3 и 5 с 7.сдвига,ния элементарных передаточных функций, рассчитать их параметры и начальные условия и соединить последовательно ряд одинаковых интегродифференциальных вычислителей в общем случае с различными условиями икоэффициентами А,.В,С и П, В этомслучае выходные шины, 38 и 39 каждогопредыдущего интегро-дифференциального вычислителя подключаются соответственно к входным шинам 36 и37 последующего интегро"дифференциального вычислителя. Причем синхронизация работы всего ряда и нескольких одинаковых йнтегро-дифференциальных вычислителей, реализующихкаждый свою передаточную Функцию, осуществляется от одного и того же блока 11 синхронизации и в этом слу,чае не требуется дополнительных аппаратурных затрат оборудования.На базе унифицированных интегродифференциальных вычислителей можно реализовать любые виды интегродифференциальных преОбразований, необходимые для задач автоматического управления и моделирования сложных динамических объектов в реальном времени.Технико-экономические преимущества предложенного интегро-дифференциального вычислителя по сравнению 5 с известным заключаются в повышении быстродействия устройства и точности вычислений. Время вычислений на одном шаге для предложенного интегро-дифференциального вычислителя 20 Т =2 п/Ю а для известного Т =Зп /й, Таким образом, быстродействие предложенного устройства в 1,5 раза больше, чем бйстродействие известного устройства. Повышение точности вы числений достигается за счет дополнительного члена 0 Х;в рекуррент,- ном соотношении (1), который не учитывается в известном устройстве.Повышение точности.в предложенном 3 Ц интегро-дифференциальном вычислителе позволяет брать более крупный шаг вычислений, и этим еще более уве личить быстродействие.35Формула изобретения Интегро-дифференциальный вычислитель, содержащий первый, второй, тре-,щтий и четвертый регистры сдвига,первый сумматор, блок знака, блоксинхронизации, первый и второй блоки формирования дополнительного кода, первый, второй и третий тригге-ры, элемент задержки, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И,первый, второй и третий элементыИЛИ, причем вход первого регистрасдвига соединен с выходом первого .5 Осумматора, первый вход которого соединен с выходом первого элементаИЛИ, первый вход которого соединен с выходом первого элемента И,а второй - с выходом второго элемента И, первый вход первого элемента И соединен с выходом первого регистра сдвига и входом элемента задержки, второй вход первого элементаИ соединен с прямым выходом первоготриггера, первый вход второго эле-мента И соединен с выходом элемента задержки, а второй - с инверснымвыходом первого триггера, третийвход первого элемента И соединен с 6 третьим входом второго элемента И,первый вход первого блока формирования дополнительного кода соединен с первым входом второго блокаФормирования дополнительного кода,а второй - с выходом элемента задержки, лервый вход третьего элемента И соединен с первым входом четвертого элемента И и прямым выходомвторого триггера, первый вход которого соединен с первыми входами первого и третьего триггеров, второйвход третьего элемента И соединенс выходом первого блока формирования дополнительного кода, первыйвход блока знака является первым входом устройства, второй вход четвертого элемента И является .вторым входом устройства, первый выход блоказнака является первым выходом устройства, выход первого блока формирования дополнительного кода является вторым выходом устройства, первыйвход пятого элемента И соединен стретьим входом первого элемента И,с первым входом шестого элемента Ии с инверсным выходом второго триггера, выход третьего элемента Исоединен с первым входом второгоэлемента ИЛИ, второй вход которогосоединен с выходом пятого элементаИ, выход второго элемента ИЛИ соединен с входом второго регистра сдвига., выход которого соединен с вторым входом шестого элемента И, выход четвертого элемента И соединенс первым входом третьего элементаИЛИ, второй вход которого соединенс выходом шестого элемента И, выход третьего элемента ИЛИ соединенс входом третьего регистра сдвига,выход которого соединен с вторымвходом пятого элемента И, выход четвертого регистра сдвига соединен спервым входом седьмого элемента И,второй вход которого соединен с прямым выходом третьего триггера, второй .вход которого соединен с выходомвосьмого элемента И, первый входкоторого соединен с выходом второгоэлемента ИЛИ, выход седьмого элемента И соединен с вторым входом второго блока формирования дополнительного кода, второй вход блока знакасоединен с выходом сумматора, а третий - с:первым выходом блока синхронизации, второй выход блока знакасоединен с первым входом первого блока формирования дополнительного кода, второй, третий, четвертый ипятый выходы блока сихронизации соединены соответственно с первым и.вторым входами первого триггера, вторыми входами второго триггера и восьмого элемента И, о т л и ч а ю щ и й -с я тем, что,с целью повышения быст

СмотретьЗаявка

2895320, 18.03.1980

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УССР, ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

БАРАНОВ ГЕОРГИЙ ЛЕОНИДОВИЧ, БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: вычислитель, интегро-дифференциальный

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/11-960813-integro-differencialnyjj-vychislitel.html" target="_blank" rel="follow" title="База патентов СССР">Интегро-дифференциальный вычислитель</a>

Предыдущий патент: Управляемый генератор случайных чисел

Следующий патент: Устройство микропрограммного управления

Случайный патент: Устройство для изготовления обрезиненного кордного полотна