Устройство для передачи и приема дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 642867

Авторы: Когновицкий, Михеев, Сюрин

Текст

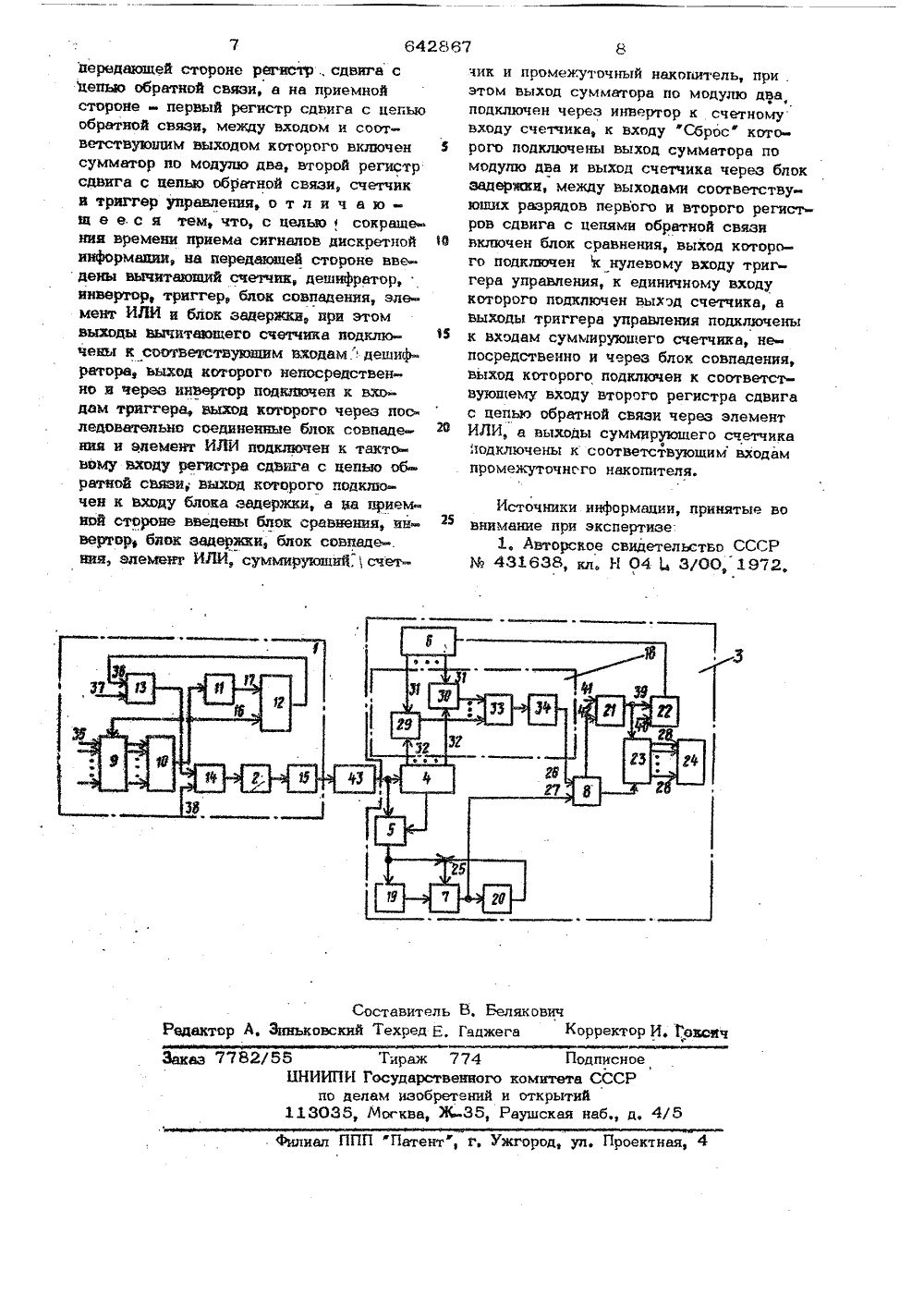

(23) Приоритет Опубликовано 15.0 рстееииай кюмататсссрделам азобретвеФн творите(53) УДК 621.39 . 14(088,8) 79,Бюллетеньпубликования описания 18.01.7 72) Авторы изобретения ин и И, С, Михеев О. гновицк 71) Заявитель им пр 54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕ ИИСКРЕТИСЙ ИНФОРМАИИИ стройст щение времени приемной информации.Дпя этого в устри приема дискретнойжашее на передаюшесдвига с цепью обрат йство для передачиинформации, содерстороне регистрной свьэи, а наИзобретение относится к рвдиотех нике и может быть использовано для передачи дискретной информации с высокой скоростью.Известно устройство для передачи и приема дискретной информации, содержащее на передающей стороне регистр сдвига с цепью обратной связи а на приемной стороне - первый регистр сдвига с цепью обратной связи, между входом и соответствующим выходом котсьрот о включен сумматор по модуупО два 9 второй регистр сдвига с цепью обратной связи, счетчик и триггер управления 11Однако в извлико время поисЦелью изобр естном у ве века сообщений,етения является сокраа сигналов дискрет пектротехнический инстнту свозиА. Бонч-БруевичаЬвъаам,приемной сторонепервый регистр сдвига с цепыа обратной связи, между входом и соответствующим выходом кото рого включен сумматор по модулю два, второй регистр сдвига с цепью обр 3 ной связи, счетчик и триггер управленияна передающей стороне введены вычитающнй счетчик, дешифратор, инвертор, григгер, блок совпадения, элемент ИЛИ и блок задержки, при этом выходы вычи тающего счетчика подключены к соот- ветствующим входам дешнфратора, выход которого непосредственно и через.инвертор подключен к входам триггера, выход которого через последовательно соединенные блок совпадения и элемент ИЛИ подключен к тактовомувходу регистра сдвига с цепью обратной связи выход которого подключен к входу блока задержки, а на приемной стороне ввэде В ны блок сравнения, инвертор, блок задержки, блок совпадения, элемент ИЛИ, суммирующий счетчик и промежуточный накопительр при этом выход сумматорапо модулю два подключен через инвертор к счетному входу счетчика, к входу"Сброс" которого подключены выход сумматора по модулю два и выход счетчикачерез блок задержки, между выходами. Соответствующих разрядов первого и второго регистров сдвига с цепями обратной связи включен блок сравнения, выход которого подключен к нулевому входу триггера управления, к единичному 1 Овходу которого подключен выход счетчика,а выходы триггера управления подключены к входам суммирующего счетчика непосредственно и через блок совпадения,выход которого подключен к соответствующему входу второго регистра сдвига с цепью обратной связи через элемент ИЛИ, а выходы суммирующегосчетчика подключены к соответствующимвходам промежуточного накопителя,20На чертеже приведена структурнаяэлектрическая схема устройства.Устройство для передачи и приемадискретной информации содержит на передакнцей стороне 1 регистр 2 сдвигас ценно обратной связи, а на приемнойстороне 3 - первый регистр 4 сдвигас цепью обратной связи, между входоми соответствующим выходом котороговключен сумматор 5 по модулю два, Зфвторой регистр 6 сдвига с цепью обратной связи, счетчик 7 и триггер 8управления, а также на .передающейстороне 1 - Вычитаюший счетчик 9, дешифратор 10; инвертор 11, триггер12, блок 13 совпадения, элемент ИЛИ14 и блок 15 задержки, при этом выходы вычитаюшего счетчика 9 подключены к соответствующим входам дешифратора 10, выход которого непосредственно и через инвертор 11 подключенк входам 16 и 17 триггера 12, выходкоторого через последовательно соединенные блок 13 совпадения и элементИЛИ 14 подключен к тактовому входурегистра 2 сДВига с цепью Обратнойсвязи, выход которого подключен к входу блока 15 задержки, а на приемнойстороне 3 - блок 18 сравнения, инвертор 19, блок 20 задержки, блок 21совпадения, элемент ИЛИ 22, суммирующий счетчик 23 и промежуточный накопитель 24, при этОм ВыхОд сумматора 8 по модулю два подключен черезинвертор 19 к счетному входу счетчика557, к входу 25 Сброс которого подключены Выход сумматора 5 по модулюдва и выход счетчика 7 через блок 20 задержки, между выходами соответствующих разрядов первого и второго регистров 4 и 6 сдвига с цепями обратной связи включен блок 18 сравнения, выход которого подключен к нулевому входу 26 триггера 8 управления, к единичному входу 27 которого подключен в ход счетчика 7, а выходы триггера 8 управления подключены к входам суммирующего счетчика 23 непосредственно и через блок 21 совпадения, выход которого подключен к соот ветствующему входу второго регистра 6 сдвига с цепью обратной связи через элемент ИЛИ 22, а выходы суммирующего счетчика 23 подключены к соответствующим входам 28 нромежуточного накопителя 24, блок 18 сравнения состоит из сумматоров 29 и 30, к вхо-, дам 31 которых подключены второй ре гистр 6 сдвига с цепью обратной связи а к входам 32 - первый регистр 4 сдвига с цепью обратной связи элемента ИЛИ 33 и инвертора 34, кроме того, на чертеже показаны входы 35 вычитаюц;его счетчика 9, входы 36 и 37 блока 13 совпадения, вход 38 элемента ИЛИ 14 для подачи "быстрых" тактовых импульсов (ТИ) входы 39 и 40 элемента ИЛИ 22, входы 41 и 42 блока 21 совпадения и канал 43 связи между передающей и приемной сторонами 1 и 3.Устройство работает следующим образом.По команде с управляющего устройства (не показано) в ячейки двоичного вычитаюшего счетчика 9 параллельным кодом по входам 35 происходит запись комбинации первичного кода. Если записанная комбинация отличается от нулевой, то на выходе дешифратора 10 появится нуль, который инвертируется инвертором 11, поступает на вход триг гера 12 и устанавливает упомянутый триггер 12 в состояние "1. Сигнал с Выхода триггера 12 поступает на вход 36 блока 13, который открывает и пропускает поступающие на вход 37 блока 13 "быстрые" тактовые импульсы, частота следования которых не менее чем в Д раз превышает номинальную тактовую частоту, где Я -выраженная в числе элементов длина комбинации вторичного кода, передаваемого в канал 43. Значение Ц должно удовлетворять неравенству И й 2 ф- , где Д -длина комбинации первичного кода.Быстрые тактовые импульсы с выходаблока 1 3 поступают на счетный вход вычитающего счетчика 9 и параллельно через элемент ИЛИ 14 на тактовый входрегистра 2, "Быстрые" тактовые импульсы будут подаваться до тех пор, покавычитаюший счетчик 9 не установитсяв нулевое состояние. В последнем случае срабатывает дешифратор 10 нулевого состояния, сигнал с выхода кото 1 Орого поступает на вход 16 триггера 12и устанавливает его в нулевое состояние, что приводит к закрыванию блока13 и прекращению подачи "быстрых тактовых импульсов (ТИ) на счетный вход 15вычитаюшего счетчика 9 и на тактовыйвход регистра 2, Таким образом, количество поступивших на тактовый входрегистра 2 быстрых" ТИ зависит оттого, какая комбинация первичного кода йбыла записана в ячейки вычитаюшегосчетчика 9, Под действием этих быстрых" тактов эа время, не превьшпцошеепериода номинальной тактовой частоты(длительности одной элементарной посылки), производится сдвиг фазы,формируемой в регистре 2 псевдослучайной последовательности (ПСП) на число шагов, равное десятичной циФре, соответствующей двоичной комбинации пер- Зфвичного кода. Под действием ТИ нощ- нальной частоты, поступающих на вход38.элемента ИЛИ 14 и далее через ньго на тактовый вход регистра 2, производится выдача на вход 41 через блок15 нсевдослучайной последовательностис новой фазой. Елок 15 необходим длятого, чтобы избажать дробления послед"него элемента предыдушей ПСП во времеформированея последующей ЙСП врегистре 2Принимаемая с выхода канала 43последовательность поступает параллельно на вход первого регистра 4 с элементом логического сложения и на пер43вый вход сумматора 5, на второй входкоторого подается последовательность,формируемая регистром 4. Если с выхода канала 43 поступает ПСП, не соИдержащая ошибок, то с выхода сумматора 5 через инвертор 19 на счетныйвход счетчика 7 поступает последовательность нулей. При наличии в принимаемой последовательности зачетногоЯ участка длинойа П +К (здесь ) еьасость счетчика 7, ц -количество разрядов регистра 4), не содержащего ошибок, происходит заполнение счетчика 7,В противном случае каждая единица с выхода сумматора 5 поступает на вход 25 счетчика 7, сбрасывает показания счетчика 7 и устанавливает его в исходное состояние,При заполнении счетчика 7 сигнал с его выхода поступает на вход 27 установки триггера 8 в единичное состояние и параллельно на вход блока 20, с выхода которого задержанный импульс подается на вход 25 Сброса счетчика 7 в исходное нулевое состояние.Триггер 8, установленный в состояние 1 выдает сигнал с прямого выхода на вход 42 блока 21, последний открывается н по входу 41 через блок 21 начинают поступать быстрые ТП на счетный вход суммирующего счетчика 23 ипараллельно на вход 39 элемента ИЛИ 22, с вьюна которого они подаются на вход второго регистра 6 с ло гической обратной связью и производят сдвиг ранее принятой (предыдущей) ПСП относительно принимаемой, Сдвиг осуществляется цо совпадения. фаз указанных последовательностей, при этом на входах 31 и 32 сумматоров 29 и 30 блока 18 будут иметь место одинаковые комбинации, поэтому на выходах сумматоров 29 и 30 будут нули, на выходе элемента 33 будет также нуль, который через иивертор 34 поступит на вход 26 триггера 8 и установит его в нулевое состояние. Сигналом с инверсного выхода чрит- гера 8 производится считывание показаний суммируюшего счетчика 23 на входы 28. Информационная комбинация с входов 28 передается в случае необходимости непосредственно потребителю или записывается в лромежуточный накопитель 24, обеспечиваюший синхронную выдау информации потребителю.Показания суммирующего счетчика 23 представляют собой комбинацию первичного кода, введенную на передаче, когорая виявлена на приеме путем подсчета числа шагов, иа которое различаются фазысоседних последовательно передаваемых ПСП. После выдачи наар малин потребителю устройство на приемйой стороне 3 возвращается в исходное состояние.Формула изобретенияУстройство для передачи и приемадискретной информации, содержащее на7782/55 Тираж 774 БНИИПИ Государственно по делам изобретений 113035, Могква, Ж 35, Подписноего комитета СССРи открытийРаушская наб., д, 4/5 иал ППП Патент", г. Ужгород, ул. Проектная, 4 передаюшей стороне регистр ., сдвига сцепью обратной связи, а на приемнойстороне - первый регистр сдвига с цепьюобратной связи, между входом и соответствующим выходом которого включенсумматор по модулю два, второй регистрсдвига с цепью обратной связи, счетчики триггер управления, о т и и ч а ющ е е с я тем, что, с целью 1 сокращении времени приема сигналов дискретнойииформапии, на передакецей стороне введеиь 1 вычитаюший счетчик, дешифратор,инвертор, триггер, блок совпадения, элемент ИЛИ н блок задержки, при этомвыходы вычитаюшего счетчика нодключены к соответствующим входам дешифратора, выход которого непосредственно и через иивертор подключен к входам триггера, выход которого через пос.ледовательно соединенные блок совпадения и элемент ИЛИ подключен к тактовому входу регистра сдвига с цепью обратной связи; выход которого цодключеи к входу блока задержки, а на приемИОЙ стороне введены блок сравнения, инвертор блок задержки, блок совпаде-.ния, элемент ИЛИ, суммирующий.счетчик и промежуточный накопитель, при .этом выход сумматора по модулю два подключен через инвертор к счетному входу счетчика, к входу Сброс кото рого подключены выход сумматора помодулю два и выход счетчика через блок задержки, между выходами соответствующих разрядов первого и второго регистров сдвига с цепями обратной связи 16 включен блок сравнения, выход которого подключен к нулевому входу триггера управления, к единичному входу которого подключен выход счетчика, а выходы триггера управления подключены к входам суммируюцего счетчика, непосредственно и через блок совпадения, выход которого подключен к соответствующему входу второго регистра сдвига с цепью обратной связи через элемент 2 ф ИЛИ, а выходы суммирующего счетчикаподключены к соответствующим входам промежуточного накопителя. Источники информации, принятые вовнимание при экспертизе 1. Авторское свидетельство СССР

СмотретьЗаявка

2420782, 15.11.1976

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФЕССОРА М. А. БОНЧ-БРУЕВИЧА

КОГНОВИЦКИЙ ОЛЕГ СТАНИСЛАВОВИЧ, СЮРИН ВЯЧЕСЛАВ НИКОЛАЕВИЧ, МИХЕЕВ ИГОРЬ СТЕПАНОВИЧ

МПК / Метки

МПК: H04L 17/00

Метки: дискретной, информации, передачи, приема

Опубликовано: 15.01.1979

Код ссылки

<a href="https://patents.su/4-642867-ustrojjstvo-dlya-peredachi-i-priema-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для передачи и приема дискретной информации</a>

Предыдущий патент: Лентопротяжное устройство

Следующий патент: Устройство для передачи данных

Случайный патент: Рабочий орган для обработки поверхностей