Управляющий процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

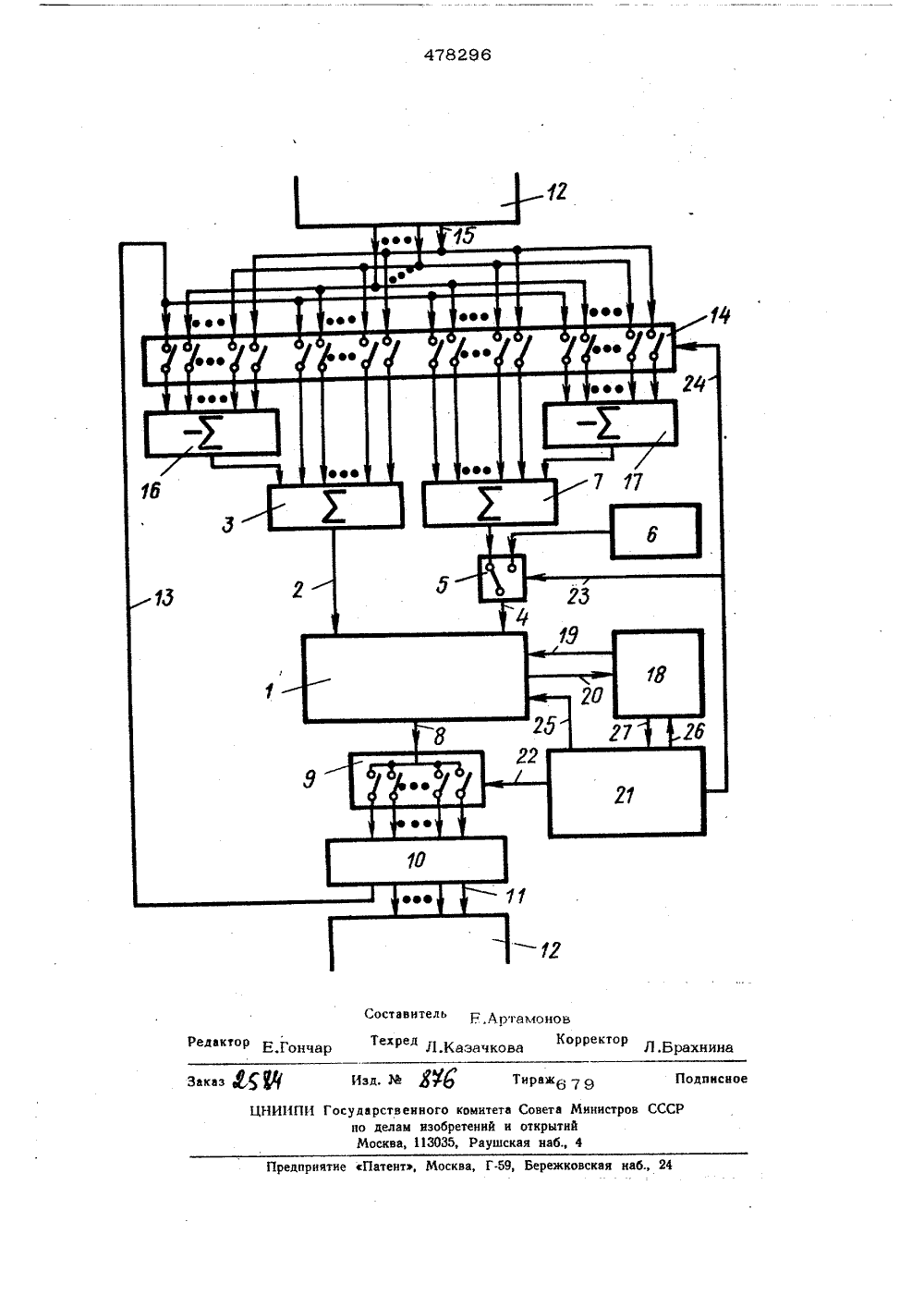

Оп ИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистичесааРеспублик/ггГасударственный квинтеСаввта Миннстров СССРв делам нзобретвннйн нтннмтнй К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(088.8) 75,Бюллетеньопнсання 05,08.7 5 ико ата о Авторы зобретення радский ордена Ленина политехнический институт" им. М. И, Калинина 71) Заявитель ЦЕССОР(54) УПРАВЛЯЮЩИ ычислительной ние в дстве инфор рвичн в ана мациой облоговой применяются управля меющие в своем соста "напряжение-код, кодма аналоговых сигнармирования выходных процессора. Известны которых часть ариф- выполняется непосред вателе напряжениеили во входных цепях ощение устройстродействия.аря тому, что го эапоминато- ммутатором входрого подключеыходы третье- рб Изобретение относится к втехнике и может найти приместемах автоматизации произвпроцессов, а также в составеонных систем для приема и иработки данных, поступающихформе.Известны и широкоющие процессоры, иве преобразовательнапряжение для приелов. от объекта и фоаналоговых сигналовтакже процессоры, вметических операцийственно в преобраэокод, код-напряжениеего.Цель изобретения - упрва и повышение его быстДостигается это благододин из выходов аналоговощего блока соединен с коных сигналов, выходы котоны ко входам сумматоров, а в.07.72 (21) 181 1881/18-24м заявкн - Ю Г. Воржев, В. Г. Колосов и С, П. Некрас го и четвертого сумматоров подсоединены соответственно к входам первого и второго сумматоров. На чертеже приведено предлагаемоеустройство,Процессор содержит преобразователь"код-напряжение, напряжение -код" 1. Одиниэ его аналоговых входов связью 2 соединен с выходом сумматора 3. Другой аналоговый вход преобразователя связью 4соединен с переключателем 5 и далее систочником эталонного напряжения 6 ивыходом сумматора 7. Аналоговый выходпреобразователя по связи 8 через коммутатор 9 соединен с аналоговым запоминающим блоком 10. Аналоговый запоминающйй блок связями 11 соединен с объектом 12, а связью 13 - с коммутаторомвходных сигналов 14, Последний в своюочередь, связан с объектом (связь 15) ис сумматорами 3, 7 и сумматорами 1617. Процессор содержит также цифровойзапоминающий блок 18, который имеетсвязи 19 20 для обмена кодами с преоб-разователем. .Работа процессора органиДополнительным достоинством предлагаемого процессора является малое число управляющих сигналов (на входы коммутаторов и переключателя), за счет возбуждения которых могут выполняться различныекоманды и программы. Управляющий процессор, содержащий преобразователь, первый вход которого подключен к выходу первого сумматора, а второй вход через переключатель - к выходу второго сумматора и к источнику эталонного напряжения, третий вход и первый выход преобразователя соединены с цифровым запоминающим блоком, второй выход через коммутатор выходных сигнаазв подключен к аналоговому запоминающему блоку, блок управления соединен с преобразователем, коммутаторами входных и выходных сигналов, переключателем и цифровым запоминающим блоком, о т л и ч а ю щ и йс я тем, что, с целью упрощения устройства и повышения его быстродействия один из выходов аналогового запоминающего блока соединен с коммутатором входных сигналов, выходы которого подключе-ны к входам сумматоров,а выходы третье-: го и четвертого сумматоров подсоединены (соответственно к входам первого и второ-, го сумматоров. чения большей гибкости процессора при реализации программ в нем предусмотрена, возможность запоминания результатов, вг аналоговой форме с последующей подачей: .их по связи 13 для дальнейших вычисле 5 , ний.Например, умножение двух величин К и К, представленных кодами, выполняет-;ся в два этапа, Сначала величина К 1 пре . образуется в напряжение и запоминается, затем умножается наКкак это уже было рассмотрено.Все вычислительные операции выполня ;:ются без специального арифметического устройства с помощью преобразователя, аналогового запоминающего блока и комму. таторов, которые обязательно входят в состав управляющего процессора для связи с щ объектом. Тем самым достигается экономия оборудования и повышается надежность процессораПо быстродействию процессора также достигается определенный выигрыш, потому что совмещаются процессы вычисления и преобразования в цифровой код. Кроме того, операции умножения и деления выполняются за время одного преобразования, что обычно по количеству необходимых так- З 0 тов работы много выгоднее, чем при реаызации этих операций в арифметическом устройстве с цифровыми сумматорами. Предмет изобретения478296 едактор аказЩ зд, М Тиражб 7 9 Подписи НИИПИ Государственного комитета Совета Мини но делам изобретений н открытий Москва, 113035, Раушская наб., 4 в СССР дприятие сПатеитэ, Москва, Г, Бережковская наб., 24 СоставительГончар р д Л.Казачкова Л.Брахн

СмотретьЗаявка

1811881, 17.07.1972

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

ВОРЖЕВ ВЛАДИМИР ГРИГОРЬЕВИЧ, КОЛОСОВ ВЛАДИМИР ГРИГОРЬЕВИЧ, НЕКРАСОВ СТЕПАН ПЕТРОВИЧ

МПК / Метки

МПК: G06F 1/00

Метки: процессор, управляющий

Опубликовано: 25.07.1975

Код ссылки

<a href="https://patents.su/4-478296-upravlyayushhijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Управляющий процессор</a>

Предыдущий патент: Струйный генератор колебаний

Следующий патент: Элемент ассоциативной матрицы

Случайный патент: Устройство для автоматического регулирования режима работы транспортного средства