Программируемый процессор спектральной обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

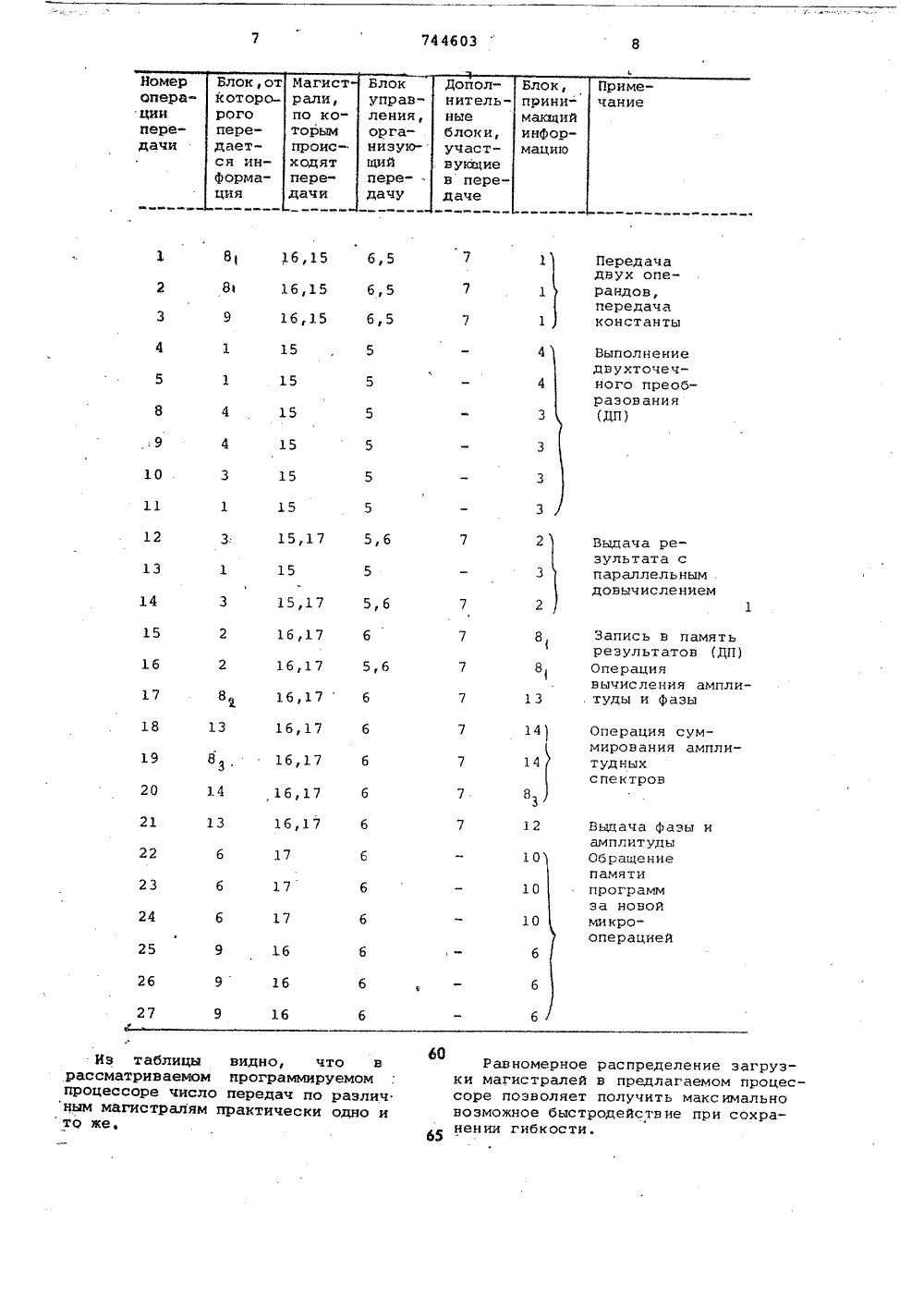

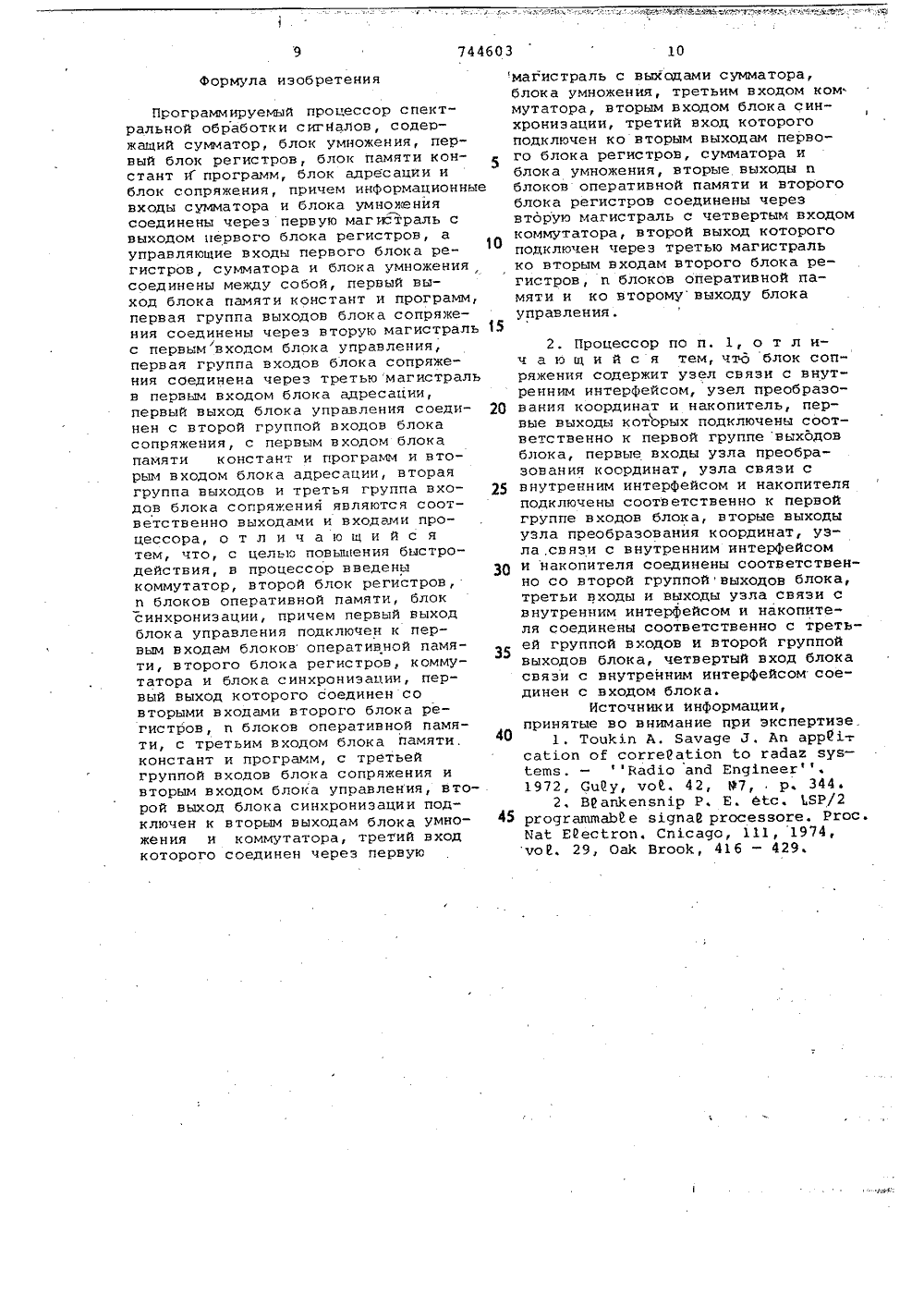

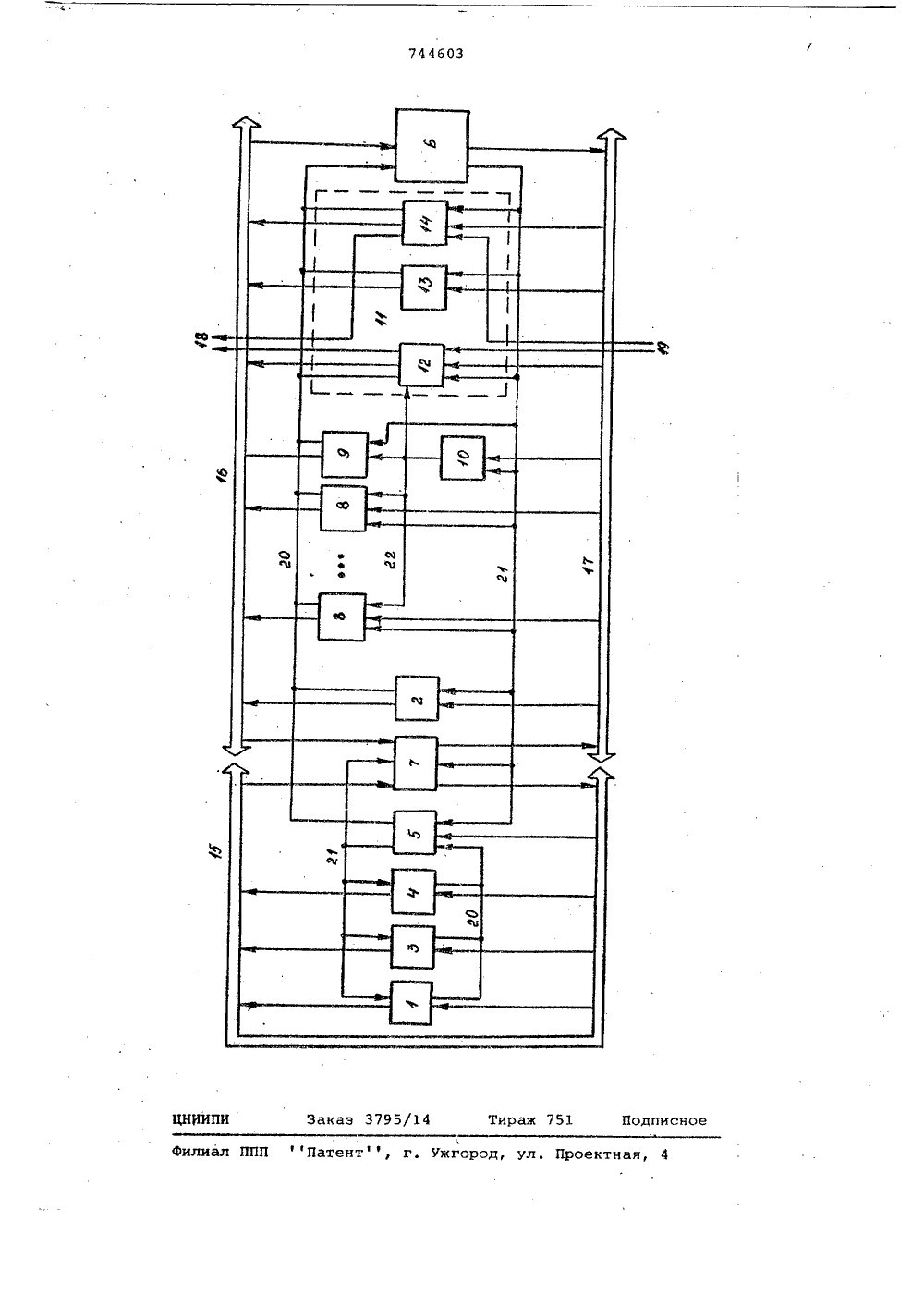

Союз Советских Социалистических Республик(22) Заявлено 200378 (21) 2591929/18-24 Р)М2 с присоединением заявки М С 06 Г 15/34 Государственный комитет СССР по делам изобретений и открытий(23) Приоритет Опубликовано 3006.80, Бюллетень %24 Дата опубликования описания 300680(54) ПРОГРАММИРУЕМЬЙ ПРОЦЕССОР СПЕКТРАЛЬНОЙ ОБРАБОТКИ СИГНАЛОВ Изобретение относится к вычислительной технике и может использоваться в вычислительных системах иустройствах циФровой обработки инФормации,Известно устройство, которое содержит четыре умножителя, шесть сум-,маторов, блоки памяти, индексноеустройство, устройство управления 111.10Это устройство обладает единымалгоритмом вычисления, вОплощеннымв жесткой структуре, эффективностьтаких процессоров требует согласования по быстродействию всех входящих в него блоков,Недостатком устройства являетсяневозможность реализовать другой. алгоритм вычисления, более производительный при имекщихся характеристиках отдельных блоков.Наиболее близким по техническойсущности к предлагаемому изобретению является программируемый процессор обработки сигналов, применяемыйтакже для спектральной обработкисигналов, в котором можно реализоватьразличные алгоритмы вычислений. Онсодержит блок суммирования-вычитания, блок умножения, входные шины данных которых подсоединены к первой магистрали данных, первый блокрегистров общего назначения, выходные шины данных которого также соединены с первой магистралью данных,управляющие входы всех указанныхблоков соединены между собой, блокпамяти программ и кбнстант, блоксопряжения и обмена, выходные шиныданных которых соединены со второймагистралью данных, индексный блок,выход которого соединен с адресными шинами блока памяти программ .и констант и адресными шинами блока сопряжения и обмена, входныешины последнего блока, а также индексного блока соединены с третьеймагистралью данных, блок управления,входные шины данных которого соединены со второй магистралью данных,управляющие выходы - со входами управления блока памяти программ иконстант, индексного блока, блокасопряжения и обмена; блоки нормализации и деления, первые и вторыевходы которьпс соединены соответственно со второй и третьей магистралями данных, выходы - с первой магистралью данных, управлякщие входыс выходом блока управления, индексный блок, второй информационный вход которого соединен с третьей маги- стралью данных, вход первого блока регистров общего назначения и выхода блоков умножения и суммирования- вычитания соединены с первой магистралью данных, при этом дополнительные входы - выходы блока сопРяжения и обмена являются входами й выходами программируемого процессора 12) .Недостатком этого процессора, имеющего модульную структуру, является малое быстродействие, что объясняется ориентацией модульной структуры этого процессора на широкий класс 15 задач и, в связи с этим, недостаточным учетом особенностей спектральных алгоритмов обработки сигналон .Цель изобретения - повышение бы стродейстния.Поставленная цель достигается тем, что.в программируемый процессор спектральной обработки сигналов, содержащий сумматор, блОк умножения, 25 первый блок регистров, блок памяти констант и программ, блок адресации и блок сопряжения, причем информационные входы сумматора и блока умножения соединены через первую магистраль с выходом первого блока регистров, а управляющие входы первого блока регистров, сумматора и блока умножения соединены между собой, первый выход блока памяти констант и программ, первая группа выходов блока сопряжения 35 соединены через вторую магистраль с первым выходом блока управления, первая группа входов блока сопряжения соединены через третью магистраль с первым входом блока адресации, 40 первый выход блока управления соединен с второй группой входов блока сопряжения, с первым входом блока памяти констант и программ и вторым входом блока адресации, вторая группа выходов и третья группа входов блока сопряжения являются соответственно выходами и входами процессора, введены коммутатор, второй блок, регистров, и блоков оперативной па-мяти, блок синхронизации, причем первый выход блока управления подключен к первым входам и блоков оперативной памяти, второго блока регистров, коммутатора и блока синхронизации, первый выход которого 55 соединен со вторыми входами второго блока регистров, и блоков оперативной памяти, с третьим входом блока памяти констант и программ, с третьей группой входов блока сопряжения щ 0 и вторым входом блока управления, второй выход блока синхронизации подключен к вторым выходам блока умножения и коммутатора, третий вход которого соединен через первую магистраль с выходами сумматора, блока умножения,третьим входом коммутатора и вторымвходом блока синхронизации, третийвход которого подключен ко вторымныходам первого блока регистров, сумМатора и блока умножения, вторые выходы и блоков оперативной памяти ивторого блока регистров соединены через вторую магистраль с четвертымвходом коммутатора, второй выход котоРого подключен через третью магист-раль ко вторым входам второго блокарегистров, п блоков оперативной памяти и ко второму выходу блока управления, а также тем, что блок сопряжения содержит узел связи с внутренниминтерфейсом, узел преобразованиякоординат и накопитель,. первые выходы которых подключены соответственно к первой группе выходов блока,первые нходы узла преобразованиякоординат, узла связи сннутренниминтерфейсом и накопителя подключенысоответственно к первой группе входов блока, их вторые входы сОЕдИНЕны соответственно со второй группойвходон блока, вторые выходы узлапреобразования координат, узла связи с внутренним интерфейсом и накопителя соединены соответственно совторой группой выходов блока, третьивходы и выходы узла связи с внутренним интерфейсом и накопителя, соединены соответственно с третьей группой входов и второй группой выходовблока, четвертый вход блока связис внутренним интерфейсом соединенс входом блока.На чертеже представлена блок-схема программируемого процессораспектральной обработки сигналов,Блок-схема содержит блоки 1, 2регистров, сумматор 3, блок 4умножения, блок 5 управления, блокб синхронизации, коммутатор 7, иблоков 8 оперативной памяти, блок 9памяти констант и программ, индексный блок 10 адресации, блок 11 сопРяжения, который состоит иэ блока12 связи с внутренним интерфейсом,блока 13 преобразования координати накопителя 14, магистрали 15, 16,17, выходы 18 процессора, входы 19процессора, управляющие входы ивыходы 20, 21 блоков управления,адресные шины 22,Работа программируемого процессора спектральной обработки сигналов определяется конкретностьювыбранного алгоритма быстрогопреобразования Фурье (БПФ) 3, алгоритмов умножения на весовую функцию,вычисления амплитуды и фазы, алгоритмов усреднения (накопления)спектров.Так можно реализовывать напредложенной структуре алгоритмыБПФ на основе элементарных операцийдвухточечногопреобразования Фурье,четырехточечного преобраэовайияФурье и т.п. Формулы для двухточеч.ного преобразования Фурье имеютвидх1 л = Х . - Х е / 2 йкп 2"Оп 21 ехгде 1 - номер итерации (1О, 1, 2, од 2(И - 1),Сама элементарная операция выполняется на блоках умножения и сумматоре 3, а также с использованиемпервого блока 1 регистров и под управлением блока 5, Все передачимежду указанными блоками выполняются по первой магистрали данных.В первом блоке 1 регистров хранитсяисходная информация, записываемаяв них иэ блоков 8 оперативнойпамяти, константы, выбираемые из блока,результаты четырехточечного преобразования, которые из регистров заносятся в блоки 8,Все пересылки между любым блоком 8, 9 памяти и первым блоком 1 регистров обеспечиваются через коммутатор 7, который управляется блоками 6 и 5 с помощью управляющих шин 21.Вся адресация памяти в рассматриваемом программируемом процессоре осуществляется блоком 10, в частности, этот блок обеспечивает выработку четырех текущих адресов для считывания новых операнцов и адресов для записи результатов обработки четырехточечного преобразования Фурье, а также для выработки адреса константы, Все передачи адресов производятся ло шинам 22,Возможность подключения нескольких блоков 8 оперативной памяти позволяет получить высокую производительность алгоритмов БПФ ввиду организации конвейерного способа обращения к блокам памяти, Тем самым имеется возможность согласовать быстродействие блоков 3 и 4.В зависимости от назначения процессора спектральной обработки сигналов блок 11 сопряжения может быть либо в минимальной комплектации, либо в максимальной, В последнем случае этот блок включает блок 12 связи с внутренним интерфейсом вычислительной системы, блок 13 преобразования координат, реализующий операцию х + 1 у,= А ехр ( 1 Ч)гдеА:П +У, Ю:сюгсд -накопитель 14, Последний блок осуществляет выдачу по сигналам, поступающим по шинам 19, результата Аодной из следукщих операций:О = 11 йо- + йо:1и = 1 2 сАо = К) + К 2 Ад 2 + А,(,1 О и = 1,2,на внешние средства отображения либорегистрации информации.Управление всем программируемымпроцессором осуществляется по прог 15 рамме, которая составляется дляконкретных характеристик имеющихсяотдельных модулей и выбранного алгоритма БПФ. Блок 5 управления адресуется через третью магистраль иочерез индексный блок 10 к блоку 9памяти и выбирает эа одно обращениеочередную порцию команд, содержащихся в одном формате операндов,хранимых в этой памяти. Далее блок5 управления реализует эти команды,управляя второй и третьей магистра- .лями 16, 17 и коммутатором 7.Блок 2 регистров служит некоторой сверхоперативной памятью, его-объем определяется количеством различных модулей и принятыми алгоритмамиобработки,Связь выхода блока 10 с однимиз входов блока 12 обеспечивает формирование адресов как для внутренней35 оперативной памяти блока 8, так идля памяти вычислительной системы,с которой идет обращение блока связипри обмене по внутреннему интерфейсу.Рассмотрим один иэ,примеров вы 40 полнения задачи вычисления прямогодискретного преобразования Фурье отодной порцииинфбрмации, хранимойв блоке памяти 84 с параллельнымвычислением амплитуды и фазы от ре,45 .зультата, полученного в предыдущемцикле при выполнении прямого дискретного преобразования Фурье.Предыдущий результат хранится вблоке памяти 82. Причем происходитнакопление (простое суммирование массивов) амплитудного спектра и передача его в третий блок оперативнойпамяти 8 з.Последовательность операций передачи по магистралям для этого примера и для одного цикла вычисленийпредставлена в таблице.744603 16,1 5 15,17 5,5 5,16,17 7 амять в (ДП) 16,1 я амзы 8 6,17 ум- ампли 6,17 6,О 23 О 6цы видно, что вмом программируемомло передач по различм практически одно и Равномерное распределение загрузки магистралей в предлагаемом процессоре позволяет получить максимально возможное быстродействие при сохранении гибкости. Из табли рассматривае процессоре чи ным магистрал то же.16,15 16,15 Передачадвух операндов,передачаконстанты ыполнениевухточечого преоб аэования ДП) Выдача результата спараллельныдовычислени Запись в результа Операция вычислен туды и ф Операциямированнятудныхспектров Выдача фазы иамплитудыОбращениепамятипрограмм а новой ми кро- перациеФормула изобретения Программируемый процессор спектральной обработки сигналов, содержащий сумматор, блок умножения, первый блок регистров, блок памяти констант Мпрограмм, блок адресации иблок сопряжения, причем информационныевходы сумматора и блока умножениясоединены через первую магистраль свыходом первого блока регистров, ауправляющие входы первого блока регистров, сумматора и блока умножения,соединены между собой, первый выход блока памяти констант и программ,первая группа выходов блока сопряжения соединены через вторую магистраль 15с первым входом блока управления,первая группа входов блока сопряжения соединена через третью магистральв первым входом блока адресации,первый выход блока управления соеди Онен с второй группой входов блокасопряжения, с первым входом блокапамяти констант и программ и вторым входом блока адресации, втораягруппа выходов и третья группа входов блока сопряжения являются соответственно выходами и входами процессора, о т л и ч а ю щ и й с ятем, что, с целью повышения быстродействия, в процессор введены 30коммутатор, второй блок регистров,и блоков оперативной памяти, блоксинхронизации, причем первый выходблока управления подключен к первым входам блоков оперативной памяти, второго блока регистров, коммутатора и блока синхронизации, первый выход которого соединен совторыми входами второго блока регистров, и блоков оперативной памяти, с третьим входом блока памяти,констант и программ, с третьейгруппой входов блока сопряжения ивторым входом блока управления, второй выход блока синхронизации подключен к вторым выходам блока умножения и коммутатора, третий входкоторого соединен через первую магистраль с выходами сумматора,блока умножения, третьим входом коммутатора, вторым в ходом блок а с инхрониэации, третий вход которогоподключен ко вторым выходам первого блока регистров, сумматора иблока умножения, вторые выходы иблоков оперативной памяти и второгоблока регистров соединены черезвторую магистраль с четвертым входомкоммутатора, второй выход которогоподключен через третью магистралько вторым входам второго блока регистров, и блоков оперативной памяти и ко второму выходу блокауправления,2. Процессор по и. 1, о т л ич а ю щ и й с я тем, что блок сопряжения содержит узел связи с внутренним интерфейсом, узел преобразования координат и накопитель, первые выходы которых подключены соответственно к первой группе выходовблока, первые входы узла преобразования координат, узла связи свнутренним интерфейсом и накопителяподключены соответственно к первойгруппе входов блока, вторые выходыузла преобразования координат, узла,связи с внутренним интерфейсоми накопителя соединены соответственно со второй группой выходов блока,третьи входы и выходы узла связи свнутренним интерфейсом и накопителя соединены соответственно с третьей группой входов и второй группойвыходов блока, четвертый вход блокасвязи с внутренним интерфейсом соединен с входом блока.Источники информации,принятые во внимание при экспертизе,1. Тоцк 1 п А. Бачаде д. Ап арр 01 тса 1 оп ой соггеРа 11 оп 1 о гайаз вувещэ. - 1 Вад 1 о апй Епу 1 пеег,1972, Сцену, чоВ. 42, 97, р, 3442, Ваап)сепвп 1 р Р, Е. Е 1 с. ,БР/2ргодгащваЫе в 1 упай ргосевзоге, Ргос.Иа 1 Е 0 ес 1 гоп. Сп 1 садо, 111, 1974,чо 1. 29, ОаК ВгооК, 416 - 429.

СмотретьЗаявка

2591929, 20.03.1978

ПРЕДПРИЯТИЕ ПЯ Г-4677

ГРИБКОВ ИГОРЬ ГЕОРГИЕВИЧ, КОШЕЛЕВ ВЛАДИМИР ПАВЛОВИЧ, МОШКОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, МУСАТОВ ИГОРЬ ФЕДОРОВИЧ, СТЕПУКОВА ТАМАРА ЛЕОНИДОВНА

МПК / Метки

МПК: G06F 17/14

Метки: программируемый, процессор, сигналов, спектральной

Опубликовано: 30.06.1980

Код ссылки

<a href="https://patents.su/6-744603-programmiruemyjj-processor-spektralnojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый процессор спектральной обработки сигналов</a>

Предыдущий патент: Стохастический кусочно-линейный аппроксиматор

Следующий патент: Устройство для определения дисперсии

Случайный патент: Релейный распределитель