Устройство для суммирования и вычитания чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

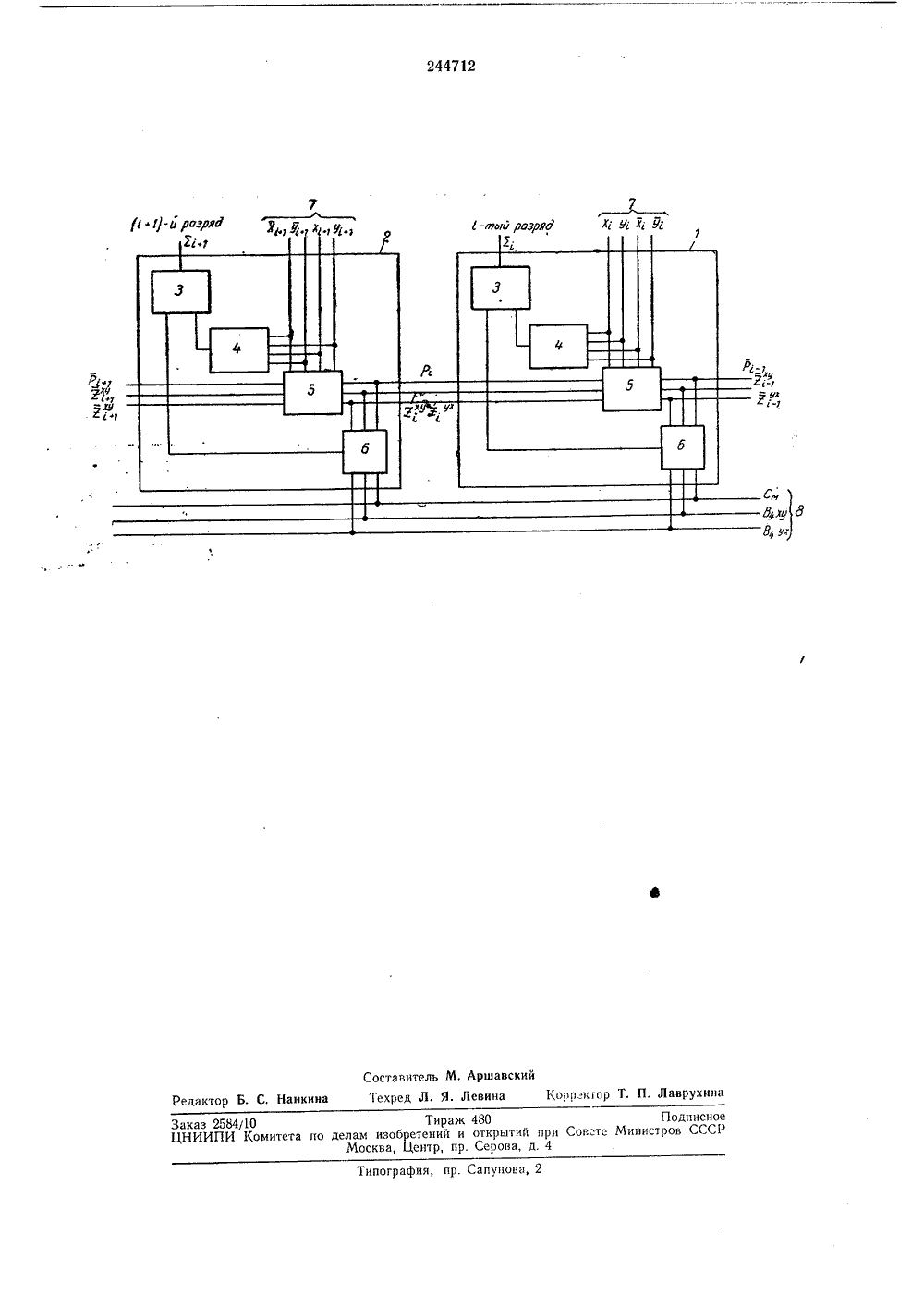

О П И С А Н И Е 244712ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскик Соцналистическик Республик.,1 К 6 ПриоритетОпубликовано 28 Л.1969, БюллетеньДата опубликования описания 22.Х.19 Комитет по дел зобретений и открытийпри Совете МинистровСССР ДК 681.325.55 (088.8) 1 кс Р 1 ъ Р 4 Автор зобретенА,со аявител Я СУММИРОВАНИЯ И ВЫЧИТАНИЯ ЧИ УСТРОЙСТ Предлагаемое устройство относится к области вычислительной техники и может быть использовано в универсальных вычислительных машинах.Известны устройства для суммирования и вычитания чисел, комбинационного типа со сквозным распространением переноса и заемов, состоящие из суммирующе-вычитающих разрядов, содержащих полусумматор частичной суммы, полусумматор разрядной суммы- разности, логический узел и коммутатор.В известных суммирующих-вычитающих устройствах наблюдается повьошенный расход элементов, в частности транзисторов, изза необходимости формирования в каждом разряде не только прямых кодов частичной суммы 5, переноса Р и заемов Л", Л, но и их обратных кодов 5, Р, Б, Л. Предлагаемое устроиство отличается тем, что оно выполнено в виде двух последовательно чередующихся суммирующе-вычитающих разрядов, в одном из которых шины прямых кодов первого и второго чисел соединены с первыми и вторыми входами логического узла и полусумматора частичной суммы, имеющего только один выход, подсоединенный к первому входу полусумматора разрядной суммы-разности. Шины обратных кодов первого и второго чисел соединены с третьими и четвертыми входами 1 полусумматора частичной суммы и логического узла, Во втором разряде шина обратного кода первого числа соединена с первыми входами полусумматора частичной суммы и логического узла, шина обратного кода второго числа соединена с четвертым входом полусумматора частичной суммы и вторым входом логического узла.Шина прямого кода первого числа соединена 10 с третьими входами полусумматора частичной суммы и логического узла, шина прямого кода второго числа соединена со вторым,входом полусумматора частичной суммы и четвертым входом логического узла, второй 15 вход полусумматора разрядной суммы-разности соединен с единственным выходом коммутатора.Это повышает быстродействие и надежность устройства.На чертеже изображена блок-схема предлагаемого устройства на два разряда (т-тый и (т + 1)-й).В состав суммирующе-вычитающего устройства входят суммирующе-вычитающий разряд 1 первого вида, суммирующе-вычитающий разряд 2 второго вида, полусумматор 3 разрядной суммы-разности, полусумматор 4 частичной суммы, логический узел 5, коммутатор б, разрядные шины 7, управляющие 30 шины 8.244712 5 10 15 Е,. =- 5;С; + 51 + С 1. 45 50 55 51: Х 1 У 1+ Х 1 Ч 1 60 65 Суммирующе-вычитающее устройство выполнено из чередующихся между собой суммирующе-вьгчитающих разрядов первого и второго вида, общее количество которых равно п.В каждом суммирующе-вычитающем разряде управляющие входы коммутатора б соединены с управляющими шинами 8. Выходы переноса и заемов логического узла 5 младшего разряда соединены со входами переноса и заемов логического узла и коммутатора последующего, более старейшего разряда; выходы коммутатора и полусумматора 4 частичной суммы соединены с различными входами полусумматора 3 разрядной суммы- разности. В суммирующе-вычитающем разряде 1 первого вида, например в 1-том, шины прямых кодов 1-тых разрядов первого и второго чисел соединены с, перовыми и вторыми входами полусумматора частичной суммы и логического узла 5 соовветственно; шины обратных, кодов 1-тых разрядов первого и второго чисел соединены с третьими и четвертыми входами полусумматора частичной суммы и логического узла соответственно. В суммирующе-вычитающем разряде второго вида, например в (1+1)-м разряде, шина обратного кода (1+ 1)-го разряда первого числа соединена с первыми входами,полусумматора 4 и логического узла 5, шина обратного кода (1+ 1)-го разряда второго числа соединена с четвертым входом,полусумматора частичной суммы 4 и вторым входом логического узла 5, шина прямого кода (1+ 1)-го разряда первого числа соединена с третьими входами полусумматора 4 частичной суммы и логического узла, шина прямого кода (1+ 1)-го разряда второго числа соединена со вторым входом полусумматора частичной суммы 4 и четвертым входом логического узла 5. Предлагаемое суммирующе-вычитающее устройство работает следующим образом.В суммирующе-вычитающем разряде первого вида, например в 1-том разряде, из поступающих по разрядным шинам 7 на вход полусумматора 4 частичной суммы, прямых и обратных кодов 1-тых разрядов двух чисел х 1 у;, х у; в полусумматоре 4 формируется прямой код частичной суммы 51 данных разрядов этих чисел в соответствии с выражением: Этот сигнал подается на один из входов полусумматора 3 разрядной суммы. На другой день вход полусумматора 3 с выхода коммутатора б подается сигнал С который формируется в коммутаторе из сигналов Р 1 1 21 У 1 Ж" 1. под воздействием управляющих сигналов СВ,ху, В 4 ух, поступаюго 25 30 35 40 щих с управляющих шин 8, в соответствии свыражением: С; = Р 1-1 С+ 7:у 1 В,ху+ 7 у 1 В,ух. Смысл этого выражения заключается в том, что при наличии одного из управляющих сигналов, определяемого производимой арифметической операцией - сложением или вычитанием и соотношением чисел по абсолютной величине, на выходе коммутатора б появляется сигнал С равный либо прямому коду переноса Р 1 1, либо одному из прямых кодов заемов 2. 1, 2 - 1, поступающих изху ухсоседнего, младшего (1 - 1)-го разряда,Полусумматор разрядной суммы-разности из гоступающих на его входы прямого кода частичной суммы 5, и сигнала с выхода коммутатора б С 1, являющегося прямым кодом одного из сигналов или переноса Р 1 1 или одного из заемов Ж - ъ 21 в зависимости от производимой арифметической операции - сложения или вычитания, формирует сигналкоторый является либо прямым кодом разрядной суммы, либо прямым кодом разрядной разности 1-тых разрядов двух чисел с учетом переноса или заемов из младшего (1 - 1)-го разряда, в соответствии с выражением: Из прямых и обратных ходов 1-тых разрядов обоих чисел х у;, х;, У 1, поступающих на входы логического узла 5 с разрядных шин 7, и обратных кодов переноса Р 1 1 и заемов Ж 1, А" 1, поступающих из младшеху ухго (1 - 1) -го разряда, логическим узлом 5 формируются прямые коды переноса Р, и заемов 2 Г, 2 Г в соответствии с выражениями: Р, = х, У, -1- Х,Р 1 1+ у, Р; 1,21 = Х 1 У 1+ Х 121 - 1+ УА - 1 2 Г = х 1 У;+х,2 Г 1+у,й 1 С соответствующих выходов логического узла 5 прямые коды переноса Р, и заемов 2, 2 Г передаются в последующий, более старший, (1+1)-й разряд.В (1+1)-м разряде, являющемся суммирующе-вычитающим разрядом 2 второго вида, из прямых и обратных кодов (1+ 1)-х разрядов двух чисел хеч 1 у 1 х 1 - ,1 уе 1, поступающих на вход полусумматора 4 частичной суммы по разрядным шинам 7, в полусумма- торе 4 формируется обратный код частичной суммы 5, 1 данных разрядов этих чисел в соответствии с выражением: 5,1 = х;1 У;,1+ х 1+1 У 11.Этот сигнал подастся на олин из входов,полусумматора 3 разрядной суммы, На другой вход полсуммато 1)1,3 с выхода коммутатора б по;1 ается сигнал С;+1, который формиху руется,в ком мутаторе из сигн алов Рг, А, Л пол воздействием управляющих сигналов С, В.;ху, г." ух, поступающих с управляющих ши г 8, з соответствии с выражением:С 1 РС+АВху+ЛВ 4 ухСмысл этого выражения заключается в том, что при наличии одного из управляющих сигналов, определяемого производимой арифметической операцией - слоиением или вычитанием - и соотношением чисел по абсолютной величине, на выходе коммутатора б существует сигнал С; 1 равный либо обратному коду переноса Р;, либо обратному колу одного из заемов Л, 21, поступаюу У 1щих из соседнего, младшего г-того разряда.Полусумматор 3 разрядной суммы-разности из поступающих на его входы обратного кода частичной суммы Бг.г и сигнала с выхода коммутатора б Сгг, являющегося либо обратным колом переноса Рлибо обратным кодом одного из заемов Ж,УГ, в зависимости от производимой арифметической операции - сложения или вычитанияформирует сигнал 1,1, который является или прямым кодом разрядной суммы, или прямым кодом разрядной разности (г+ 1) -х разрядов двух чисел с учетом переноса или заемов из младшего г-того разряда, в соответствии с выражением:";+1 = 51 С, + 5;+1 + Сг+1,логическое значение которого эквивалентновыражению (1),Из поступающих с разрядных шин 7 навходы логического узла б гпрямых и обратныхкодов (1 + 1)-х разрядов обоих чиселуг 1, х; 1, у 1.1 и прямых кодов переноса Р,и заемов Ж, Л из младшего г-того разряда логическим узлом б формируются обратные коды переноса 1 Рг 1 и заемов 51.У211 .в соответствии с выраукениями:Рс 1 - хс - 1 ус 1 + хю -1 г + чг.;1 11211 - хгч гуг1+ хг + угт" У "У,У.уг р 1(7,;. 1х; гу;. -1- х;Д -(- у; 7;". С соответствующих выходов логическогоузла б обратные коды переноса Р;1.1 и заеу ухмов А+1, 2,.1 передаются в последующий, более старший (1+2)-й разряд.Такая последовательность чередованиясуммирующе-вычитающих разрялов первого и второго видов, пде в разрядах первого вида 10 полусумматором 3 разрядной суммы и логичсским узлом 5 формируются прямые коды частичной суммы, переноса и заемов соответственно, а в разрядах второго вида аналогичными узлами формируются обратные ко лы частичной суммы, переноса и заемов, сохраняется во всех разрядах суммирующего устройства. 20Предмет изобретенияУстройство для суммирования и вычитаниячисел комбинационного типа со сквозным распространением лереноса и заемов, состоящее из суммирующе-вычитающих разрядов, 25 содержащих полусумматор частичной суммы,полусумматор разрядной суммы-разности, логический узел и коммутатор, отличающееся тем, что, с целью сокращения элементов, повышения быстролействия и надежности, оно ЗО выполнено в виде лвух последовательно черслуюшихся суммирующе-вычитающих разрялов, в одном из которых шины прямых колов первого и второго чисел соединены с первыми и вторыми входами логического узла ч 35 полусумматора частичной суммы, имеющеготолько олин выход, подсоединенный к первому входу полусумматора разрядной суммы- разности, а шины обратных колов первого и второго чисел - с третьими и четвертыми 40 входами полусумматора частичной суммы илогического узла, а во втором шина обратного кола первого числа соединена с первыми входамн полусумматора частичной суммы и логического узла, шина обратного кола вто рого числа соелинсна с четвертым входом полусумматора частичной суммы и вторым входом логического узла, шина прямого кода первого числа соединена с третьими входами полусумматора частичной суммы и логичес кого узла, цгина прямого кода второго числасослинсна со вторым входом полусумматора частичной суммы и четвертым входом логического узла, второй вход полусумматора разрядной суммы-разности соединен с един ственным выходом коммутатора.. Сапунова, 2 пограф Заказ 2584/10 Тираж 480 ПодписцоЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССРМосква, Центр, пр. Серова, д. 4

СмотретьЗаявка

1212949

кЧ, ЕСчА БИБЛИОТЕКА, А. К. Денисов

МПК / Метки

МПК: G06F 7/50

Метки: вычитания, суммирования, чисел

Опубликовано: 01.01.1969

Код ссылки

<a href="https://patents.su/4-244712-ustrojjstvo-dlya-summirovaniya-i-vychitaniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования и вычитания чисел</a>

Предыдущий патент: Магнитный дешифратор

Следующий патент: Матричное устройство для сложения десятичных чисел

Случайный патент: Способ раскроя авровых тканей