Дельта-кодек

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

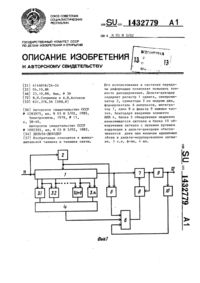

.Гаджиев,лоненко именев М.: 00 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗО К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к технике связи и вычислительной технике и позволяет повысить помехоустойчивость кодека и обеспечить независимость его характеристик от тактовой частоты. Дельта-кодек состоит из кодера и декодера. Кодер содержит фильтр 1 нижних частот, блок 2 сравнения, дискретизатор 3 и интегратор 6. Благодаря введению делителя 4 частоты на два, аналогового сумматора 5, интегратора 7 и ключевых элементов 8 - 11 обеспечивается размыкание цепи мгновенной обратной связи и исключение интеграторов 6 и 7 из цепи обратной связи операционного усилителя 30 сумматора 5. 1 з.п. ф-лы, 3 ил.Изобретение относится к технике связи и вычислительной технике и может использоваться в системах передачи информации,Цель изобретения - повышение поме хоустойчивости кодека и обеспечение независимости его характеристик от тактовой частоты.На фиг.1 и 2 изображены функциональные схемы соответственно кодера и декаде ра; на фиг,З - сигналы, поясняющие работу . кодека.Кодек состоит из кодера и декодера. Кодер содержит (фиг.1) фильтр 1 нижних,15 частот (ФНЧ), блок 2 сравнения, дискретиэатор 3, делитель 4 частоты на два, аналоговый сумматор 5, первый б и второй 1 интеграторы, первый - четвертый ключевые элементы 8 - 11. На фиг,1 обозначены ин формационный 12 и тактовый 13 входы и выход 14 кодера.Декодер содержит (фиг,2) формирователь 15 импульсов, делитель 16 частоты на два, аналоговый сумматор 17, первый 18 и 25 второй 19 интеграторы, первый - четвертый ключевые элементы 20 - 23 и ФНЧ 24, На фиг.2 обозначены информационный 25 и тактовый 26 входы и выход 27.30Блок 2 сравнения кодера включает в себя вычитатель 28 и компаратор 29.Дискретизатор 3 кодера и формирователь 15 импульсов декодера представляют собой О-триггеры, При этом первый и вто рой их выводы являются прямым и инверсным выходами соответствующего триггера,Делители 4 и 16 частоты на два выполнены на счетных триггерах. 40Аналоговый сумматор 5 (11) выполнен на операционном усилителе (ОУ) 30 и первом - пятом резисторах 31-35.На фиг.З обозначены следующие сигналы: а - тактовые импульсы на входе 13 (26); 45 б, в - сигналы на прямом и инверсном выходах делителя 4 (16) частоты на два; г - сигналы на первом С(т) и втором Х(т) входах блока 2 сравнения; д, е - напряжение на выходах соответственно первого и второго 50 интеграторов 6 и 7; ж - выходной сигнал кодера.В кодере аналоговый сумматор 5, интеграторы 6 и 7 и ключевые элементы 8-11 образуют местный декодер - предсказатель. 55Дельта-кодек работает следующим образом.Входной аналоговый сигнал С(т) после фильтрации в ФНЧ 1 поступает на первый вход вычитателя 28 в блоке 2 сравнения, на второй вход которого подается сигнал Х(т) местного декодера-предсказателя. Вычитатель 28 блока 2 формирует положительный выходной уровень, если С(т) Х(т), и отрицательный, если С(т)Х(т), т.е,0 = С(т) - Х(т), если С(т)Х(1) (1) О = С(т) - Х(т), если С(1)Х(т).Компаратор 29 в блоке 2 преобразует уровни 0 и 0 в "Лог.1", когда имеют место О, или "Лог.0" при О. Эти последовательности нулей или единиц записываются в О- триггер дискретизатора 3 в моменты, определяемые фронтами (например, положительными) тактовых импульсов (ТИ), Таким образом, на прямом выходе О-триггера дискретиэатора 3 формируется изохронная случайная последовательность цифрового сигналаС(КДт ) = С(т) - Х(т)/т = Дт, (2) где Дт - равно периоду последовательности тактовых импульсов ТИ. Последовательность импульсов с прямого выхода О-триггера дискретизатора 3 является выходным сигналом дельта-кодера. Кроме того, прямая С(КДт) и инверсная С(КДт ) последовательности поступают на соответствующие входы аналогового сумматора 5. Задача местного декодера-предсказателя состоит в том, чтобы иэ цифровых потоков С(КДт) и С(КДт) сформировать наиболее приближенную копию Х(т) входного сигнала С(т), как можно меньше отличающуюся в каждый тактовый момент от С(т). Управляющие входы ключевых элементов 8-11 получают импульсы с выходов делителя 4 частоты на два так, что, например, в и-й тактовый интервал замкнуты ключевые элементы 9 и 10 и разомкнуты элементы 8 и 11, а в следующий (и+1)-й - замкнуты элементы 8 и 11, а 9 и 10 разомкнуты. Таким образом, на каждом тактовом интервале (например, на том же и-м) напряжение интегратора 1 является выходным сигналом местного декодера-предсказателя и постоянно в течение всего и-го тактового интервала, э заряд интегратора 6 корректируется выходным током операционного усилителя 30 сумматора 5 в зависимости от напряжения интегратора 7, являющегося в данный момент выходным, и знака разности 0 или 0 (1), сформированной на входе компаратора 29, и соответственно на выходах О-триггера дискретизатора 3. На следующем такте (например, (и+1)-м) замкнуты ключевые элементы 8 и 11, а 9 и 10 разомкнуты, и напряжение интегратора 6 является выходным сигналом местного декодера-предсказателя и посто 168841210 15 20 поток единиц/нулей С(КД 1 ) после предвари55 янно в течение(п+1)-го тактового интервала,а заряд интегратора 7 корректируется, и т.д. Если в О-триггер дискретизатора 3 записана единица, то единичный символ окажется и на первом (прямом) выходе дискретизатора 3, Этот сигнал через резистор 31 попадает на инвертирующий вход операционного усилителя 30 (при этом на неинвертирующем входе оказывается нуль, поступающий с инверсного выхода дискретизатора 3), что приводит к появлению отрицательного потенциала на выходе усилителя 30 и его выходной ток через резистор 35 уменьшает напряжение интегратора 6 или 7, заряд которого корректируется. Если в О-триггер дискретизатора 3 записан нуль, то единичный потенциал через резистор 32 попадает на прямой вход оперативного усилителя 30 (при этом на инверсном оказывается нулевой потенциал), и,следовательно, корректирующий выходной ток усилителя 30 оказывается положительным,Другими словами, импульсная цепь отрицательной обратной связи стремится уменьшить заряд интеграторов 6 и 7 на тактах подстройки, если С(1)Х(т), и увеличить этот заряд, если С(т)Х(с).Таким образом, поскольку в очередном такте в одном из интеграторов 6 или 7 ведется подстройка через замкнутый ключевой элемент 8 или 10, а в другом интеграторе 7 или 6 в этом же такте напряжение постоянно и через ключевой элемент 11 или 9 подается на второй вход блока 2 сравнения, цепь мгновенной отрицательной обратнбй связи через местный декодер-предсказатель оказывается разомкнутой, что существенно повышает устойчивость дельта-кодера.Кроме того, интеграторы 6 и 7 не входят в цепь обратной связи операционного усилителя 30, следовательно, токи дрейфа его дифференциальных входов в интеграторах 6 и 7 не накапливаются. Резисторы 33-35 служат для поддержания коэффициента передачи сумматора 5 на операционном усилителе 30 равным постоянной заданной величине.В декодере (фиг,2) поинятый цифровой тельного восстановления временных положений поступает на информационный вход формирователя 15 импульсов, на тактовый вход которого поданы тактовые импульсы ТИ. Задача декодера заключается в восстановлении наиболее приближенной формы исходного аналогового сигналу С(1) по принятому цифровому потоку С(КДт ) .По существу схема декодера повторяет структуру и функции местного декодера 25 30 35 40 45 предсказателя кодера. Сформированная копия Х(с) входного цифрового потока С(КДс) после фильтрации в ФНЧ 24 поступает на выход 27.Таким образом, поскольку цепь мгновенной обратной связи разомкнута, а интеграторы 6 и 7 не входят в цепь обратной связи ОУ 30, помехоустойчивость дельта-кодека повышается и не зависит от тактовой частоты.Формула изобретения 1. Дельта-кодек, состоящий иэ кодера и декодера, кодер содержит фильтр нижних частот, вход которого является информационным входом кодера, а выход соединен с первым входом блока сравнения, выход которого подключен к информационному входу дискретизатора, первый выход которого является выходом кодера, и первый интегратор, декодер содержит формирователь импульсов, информационный вход которого является информационным входом декодера, первый интегратор и фильтр нижних частот, выход которого является выходом декодера, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости кодека и обеспечения независимости его характеристик от тактовой частоты, в кодер и декодер введены аналоговый сумматор, второй интегратор, первый - четвертый ключевые элементы и делитель частоты на два, вход которого в кодере объединен с тактовым входом дискретизатора и является тактовым входом кодера, первый вход аналогового сумматора в кодере подключен к первому выходу дискретизатора, второй выход которого соединен с вторым входом аналогового сумматора, в декодере тактовый вход делителя частоты на два объединен с тактовым входом формирователя импульсов и является тактовым входом декодера, первый и второй выходы формирователя импульсов декодера соединены с одноименными входами аналогового сумматора, в кодере и декодере прямой и инверсный выходы делителя частоты на два подключены к управляющим входам соответственно второго, третьего и первого, четвертого ключевых элементов, выход аналогового сумматора соединен с информационными входами первого и третьего ключевых элементов, выходы которых через соответственно первый и второй интеграторы подключены к информационным входам соответственно второго и четвертого ключевых элементов,выходы которых объединены и подключены в кодере к второму входу блока сравнения и третьему входу аналогового сумматора, а в декодере - к третьему11о л/ Фос 3 Составитель О. РевинскийРедактор М, Кобылянская Техред М.Моргентал Корректор Л, Бескид Заказ 3717 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж. Раушская наб 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 входу аналогового сумматора и входу фильтра нижних частот.2. Дельта-кодек по и.1, о т л и ч а ющ и й с я тем, что аналоговый сумматор содержит операционный усилитель и первый - пятый резисторы, первые выводы первого - третьего резисторов являются соответственно первым - третьим входами сумматора, второй вывод первого и первый вывод четвертого резисторов подключены к инвертирующему входу операционного усилителя, вторые выводы второго и третьего резисторов подключены к неинвертирую щему входу операционного усилителя, выход которого соединен с первым выводом пятого резистора, вторые выводы четвертого и пятого резисторов объединены и являются выходом сумматора,10

СмотретьЗаявка

4740749, 07.08.1989

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

БАЙДАН ИГОРЬ ЕМЕЛЬЯНОВИЧ, БАСЮК ОЛЕГ ПЕТРОВИЧ, ГАДЖИЕВ МАТИН МАГСУД-ОГЛЫ, СПОЗИТО ОЛЕГ ОЛЕГОВИЧ, РОЖОК АЛЕКСАНДР ДМИТРИЕВИЧ, ФИЛОНЕНКО ВЯЧЕСЛАВ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодек

Опубликовано: 30.10.1991

Код ссылки

<a href="https://patents.su/4-1688412-delta-kodek.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодек</a>

Предыдущий патент: Функциональный аналого-цифровой преобразователь

Следующий патент: Устройство для регенерации биимпульсных сигналов

Случайный патент: Шихта для наплавки