Устройство для суммирования двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1578709

Авторы: Гайда, Квитка, Кожемяко, Короновский, Стратиенко

Текст

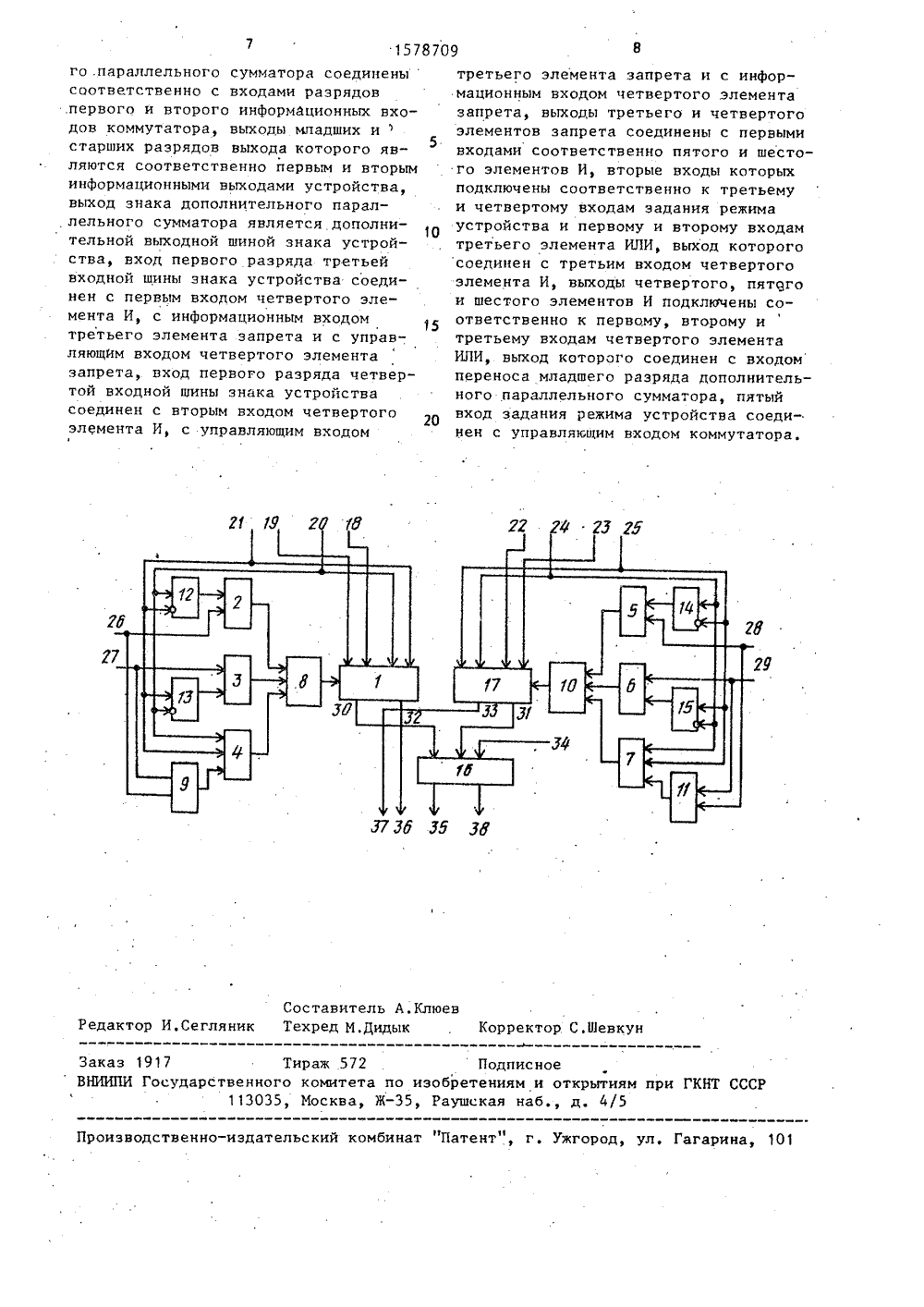

СОЮЗ СОНЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 15787 ЕНИЯ нии арифа также ети пе- шиельных ах роб Бюл,26политехнический ин тизиия дл ло чисел с иррацио лььм основ рной инфор,А,Квитка, .Гайда, .Квитка 8) ме координат, ется расширени остей эа счет ия чисел с ирм 12 как в до(56) Авт119366 (54) УСТ ДВОИЧНЫХ (57) Из о лительно ССС 984 рациональнымполнительноУстройство рское с кл, С Юдетельст 6 Г 7/50 Я СУММИР основание такодержитменты И обратном кодах. раллельный сум 7, ИЛИ 8-11, тор 16 и дополсумматор 17 зями1 ил. 0 ЙСТВ 0ЧИСЕЛретениетехник ВАНИ матор 1, эл запрета 12- нительный п 5, коммута раллельньп носится к выч с соответс жет быть исюркими евя исел,УстрР Ж ент6ут ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР(53) 68 1,325.5 (088. Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЗВМ, а также в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием -12 и обработки "векторной" информации в двумерной системе координат и является усовершенствованием изобретения по авт.св.1193665.Цель .изобретения - расширение функциональных возможностей за счет обеспечения суммирования чисел с иррациональным основанием -2 как в дополнительном, так и в обратном колах. 1)5 .С 06 Г 7/49, 7/50 ользовано при построе еских устройств ЭВМ, иализированных вьчис ах и цифровых устройс ованных систем управл ием и обработки "век ации в двоичной сист елью изобретения явл ункциональных возмож беспечения суммирова На чертеже представлена схема ус ройства для суммировация двоичных чойство содержит параллельный сумматор 1, второй и третий элемент И 2 и 3 соответственно, первый элем И 4, пятый и шестой элементы И 5 и соответственно, четвертыц элемент И второй элемент ИЛИ 8, первый элемен ИЛИ 9, четвертый элемент ИЛИ 10, третий элемент ИЛИ 11, с первого по четвертый элементы 12-1 запрета, коммутатор 16, дополцительцый параллельный сумматор 17, первую и вторую входные числовые шпнь 1819 устрой ства, первую и вторую вхолцые вицы 20 и 21 знака устройства, третью ичетвертую входные числовые шины 22 и 23 устройства, третью и четвертую входные шины 24 и 25 знака устройства, с первого по четвертый входы 26-29 задания режима устройства, выходы 30 и 3 1 разрядов параллельного сумматора 1 и дополнительного параллельного сумматора 17 соответственно, выходы 32 и 33 знака параллельного сумматора 1 и дополнительного параллельного сумматора 17 соответственно, пятый вход 34 задания режима устройства, первый информационный выход 35 устройства, выходная шина 36 знака устройства, дополнительная выходная шина 37 знака устройства, второй информационный выход 38 устройства.Устройство для суммирования двоичных чисел предназначено для сложения операндов (векторов), представленных, в двоично-кодированной позиционной системе счисления с иррационаЛьным основанием 42 как в дополнительном, так и в обратном коде.25В этой системе счисления любое число (вектор) представляется в виде Х=Х д-, ( Г 2)" " +Х -ъ(42) ++ +Х 47) +Х о ЬГ 2), (1)30В связи с тем, что веса разрядов данного кода являются последовательностью степеней основания .Г 28 2 О 4.2 4 2-2 2 42 четные степени которой представляют веса разрядов двоичного кода, а нечетные - веса разрядов двоичного кода, умноженные на 42, то выражение (1). можно записать таки2- и-г (г40Х = 2 Х 2 +Х,2, (2)1 аЪгде величины принимают значения Х, Х;6 0,1; 1 б 1,3,и;10,2,4и 45Первый член формулы (2) составляет сумму нечетных разрядов кода, а вторЬй член - сумму четных разрядов кода с основанием 2.Особенностью такого изображения является то,что код с основанием Г 2, используемый для записи числа единыйи в тоже время члены выражения (2) независимы друг от друга,Это позволяет при сложении двух операндов осу 55 ществлять параллельное. и независимое сложение составных частей операндов..Если использовать операцию сжатия (опускание нулей) четных и нечетных разрядов, то при этом выражения длячетных и нечетных разрядов примут видиу -1, 1н. Х,2;Х 2, (3)1-"О 1 огде 1,1 е 0, 1,2 -- 11.Сжатию. нечетных разрядов предшествуетих сдвиг вправо на один разрядДля суммирования операндов, четныеи нечетные разряды которых представлены выражением (3), используютсяобыкновенные двоичные сумматоры. Кроме того;эа счет наличия двух сумматоров получена возможность .одновременного и независимого сложения двух пардвоичных чисел как в дополнительном,так и обратном кодах.Устройство для суммирования двоичных чисел может работать в двух режимах: в режиме сложения 2 п-разрядныхоперандов (векторов) с иррациональнымоснованием .12 как в дополнительном,так и обратном коде; в режиме сумми-,рования и разрядных двоичных чиселв дополнительном и обратном кодах.Устройство в первом режиме работает следующим образом,Числа А и В в виде сжатых четных разрядов АВи сжатых нечетных разрядов АВ, поступающие на соответствующие входные шины 18, 20, 19, 21 и 22, 24, 23, 25 устройства, представлены и числовыми и, двумя знаковыми разрядами, а результат С (в сжатом состоянии) в виде четных разрядов С и нечетных разрядов С соответст-. венно на выходах 30, 32 и 31, 33 представлен также и числовыми и двумя знаковыми разрядами, При этом четные АВ, разряды слагаемых и нечетные А 3 2 разряды, поступающие на соответствующие шины 18,20, 19, 21 и 22, 24, 23, 25 устройства, кодируются обратными или дополнительными модифицированными кодами, а результат в виде четных С 1 и нечетных С разрядов на выходах 30, 32 и 31, 33 - только в дополнительном модифицированном коде. Если числа А и В представлены в дополнительных модифицированных кодах, то на входах 26, 28 и 27, 29 задания режима устройства должны быть нулевые, сигналы. При этом результат суммирования С (четные С и нечетные С разряды) также представлены в дополни 5157870тельном модифицированном. коде. Если число А представлено в обратном модифицированном коде а число В - в дополнительном модифицированном коде,то на входах 26, 28 задания режима5устройства должен быть единичныйсигнал, а на входах 27 и 29 нулевойсигнал, При этом, если число А отрицательное (отрицательные четные А 1 и нечетные А разряды), а число В положительное (положительные четные В и .нечетные В разряды), то на выходах элементов 12 и 14 запрета, а следовательно, и на выходах элементов И 2, 5и ИЛИ 8, 10 будут единичные сигналы, вследствие чего в младшие разряды сумматоров 1 и 17 поступает дополнительная единица. При условии, что числа А и В отрицательные, то на вы ходах элементов И 4, 7, а следовательно, и на выходах элементов ИЛИ 8,10 будут единичные сигналы, вследствие чего в младшие разряды сумматоров 1,17 также поступит дополнительная еди ,ница, В том случае, когда числа А и В положительные или число А,положительное, а число В отрицательное, то на выходах элементов 12, 14 запрета И 2, 5 р И 4, 7 и ИЛИ 8, 10 будут нулевые 30сигналы, вследствие чего в младший разряд сумматоров 1, 17 дополнительная единица не поступает, Результат суммирования С представлен в дополнительном модифицированном коде.35Если число А представлено в допол,нительном модифицированном коде, а число В в обратном модифицированном коде, то. на входах 27, 29 задания режима устройства должен быть единич О ный сигнал, а на входах 26, 28 нулевой. Если число В отрицательное, а число А положительное, то на выходах элементов 13, 15 запрета, а следовательно, и на выходах элементов И 45 3, 6 и ИЛИ 8, 10 будут единичные сигналы, вследствие чего в младшие разряды сумматоров 1, 17 поступает дополнительная единица. В том случае, когда числа А и В отрицательные, то на выходах элементов И 4, 7, а следовательно, и на выходах элементов ИЛИ 8,10 будет единичный сигнал, вследствие чего в младшие разряды сумматоров 1, 7 также поступает дополнительная единица. При условии, что числа А и В положительные или число В положитель. ное, а число А отрицательное, то на выходах элементов 13, 15 запрета И 3,о6; И 4, 7 и ИЛИ 8, 10 будут нулевые сигналы, вследствие чего в младшие разряды сумматоров 1, 17 дополнительная единица не поступает, Результат суммирования С представлен в дополнительном модифицированном коде. Сложение четных и нечетных (в сжатом виде) разрядов операндов осуществляется параллельными сумматорами 1, 17 по правилам двоичной информации. Для представления результата суммирования в коде с основанием 2 необходимо ко входу 34 приложить единичный сигнал,тогда числовая информация в виде чет" ных и нечетных разрядов, присутствующая на первом и втором входах коммутатора 16 с помощью его распределится таким образом, что нечетные разряды кода займут места между четными разрядами, т,е. будет сформирован окончательный код с основанием 2,Работа устройства для суммирования двоичных чисел в режиме сложения двух пар и-разрядных двоичных операндов ничем не отличается от первого режима. Различие состоит в том, что для формирования результатов сложения следует приложить ко входу 34 нулевой сигнал, Тогда первый результат с вы- хода сумматора 1 передается в младшие и разрядов, а второй результат с выхода сумматора 17 в старшие и разрядов выхода коммутатора 16.Формула изобретенияУстройство для суммирования двоичных чисел по авт. св. Р 1193665, о т л и ч а ю. щ е е с я тем, чтб, с целью раСширения функциональных возможностей за счет обеспечения суммирования чисел с иррациональным основанием 42 как в дополнительном, так и в обратном кодах, оно содержит четвертый, пятый и шестой элементы И, третий и четвертый элементы ИЛИ, третий и четвертый элементы запрета, коммутатор и дополнительный параллельный сумматор, прйчем третья и четвертая входные числовые шины устройства соединены соответственно с входами первого и второго слагаемь;х дополнительного параллельного сумматора, первый и второй входы знака которого соединены соответственно с третьей и четвертой входными шинами знака устройства, выходы разрядов параллельного сумматора и дополнительно1578709 оставитель А,Клюевехред М.Дидык Корректор. С,Шев актор И.Сегля 72 Подписноеета по изобретениям и открытиям а, Ж, Раушская наб., д, 45 1917 ТиражГосударственного комит113035, Москв ака НТ СССР 1 11оиэводственно-издательский комбинат Патент , г, Ужгород Гагарина, 1 го .параллельного сумматора соединенысоответственно с входами разрядовпервого и второго информационных входов коммутатора, выходы младших и "старших разрядов выхода которого являются соответственно первым и вторыминформационными выходами устройства,выход знака дополнительного параллельного сумматора является дополнительной выходной шиной знака устройства, вход первого разряда третьейвходной шины знака устройства соединен с первым входом четвертого элемента И, с информационным входомтретьего элемента запрета и с управляющим входом четвертого элементазапрета, вход первого разряда четвертой входной шины знака устройствасоединен с вторым входом четвертогоэлемента И, с управляющим входом третьего элемента запрета и с информационным входом четвертого .элементазапрета, выходы третьего и четвертогоэлементов запрета соединены с первымивходами соответственно пятого и шестого элементов И, вторые входы которыхподключены соответственно к третьемуи четвертому входам задания режимаустройства н первому и второму входамтретьего элемента ИЛИ, выход которогосоединен с третьим входом четвертогоэлемента И, выходы четвертого, пятогои шестого элементов И подключены соответственно к первому, второму итретьему входам четвертого элементаИЛИ, выход которого соединен с входомпереноса младшего разряда дополнительного параллельного сумматора, пятыйвход задания режима устройства соединен с управляющим входом коммутатора.

СмотретьЗаявка

4488403, 29.09.1988

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОЖЕМЯКО ВЛАДИМИР ПРОКОФЬЕВИЧ, КВИТКА НИКОЛАЙ АНДРЕЕВИЧ, КОРОНОВСКИЙ АЛИМ ИВАНОВИЧ, ГАЙДА ВАЛЕРИЙ БОРИСОВИЧ, СТРАТИЕНКО ВИКТОР СЕРГЕЕВИЧ, КВИТКА СВЕТЛАНА НИКОЛАЕВНА

МПК / Метки

Метки: двоичных, суммирования, чисел

Опубликовано: 15.07.1990

Код ссылки

<a href="https://patents.su/4-1578709-ustrojjstvo-dlya-summirovaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования двоичных чисел</a>

Предыдущий патент: Арифметическое устройство

Следующий патент: Параллельный накапливающий сумматор

Случайный патент: Способ непрерывного литья металлов