Устройство для сложения и вычитания чисел по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

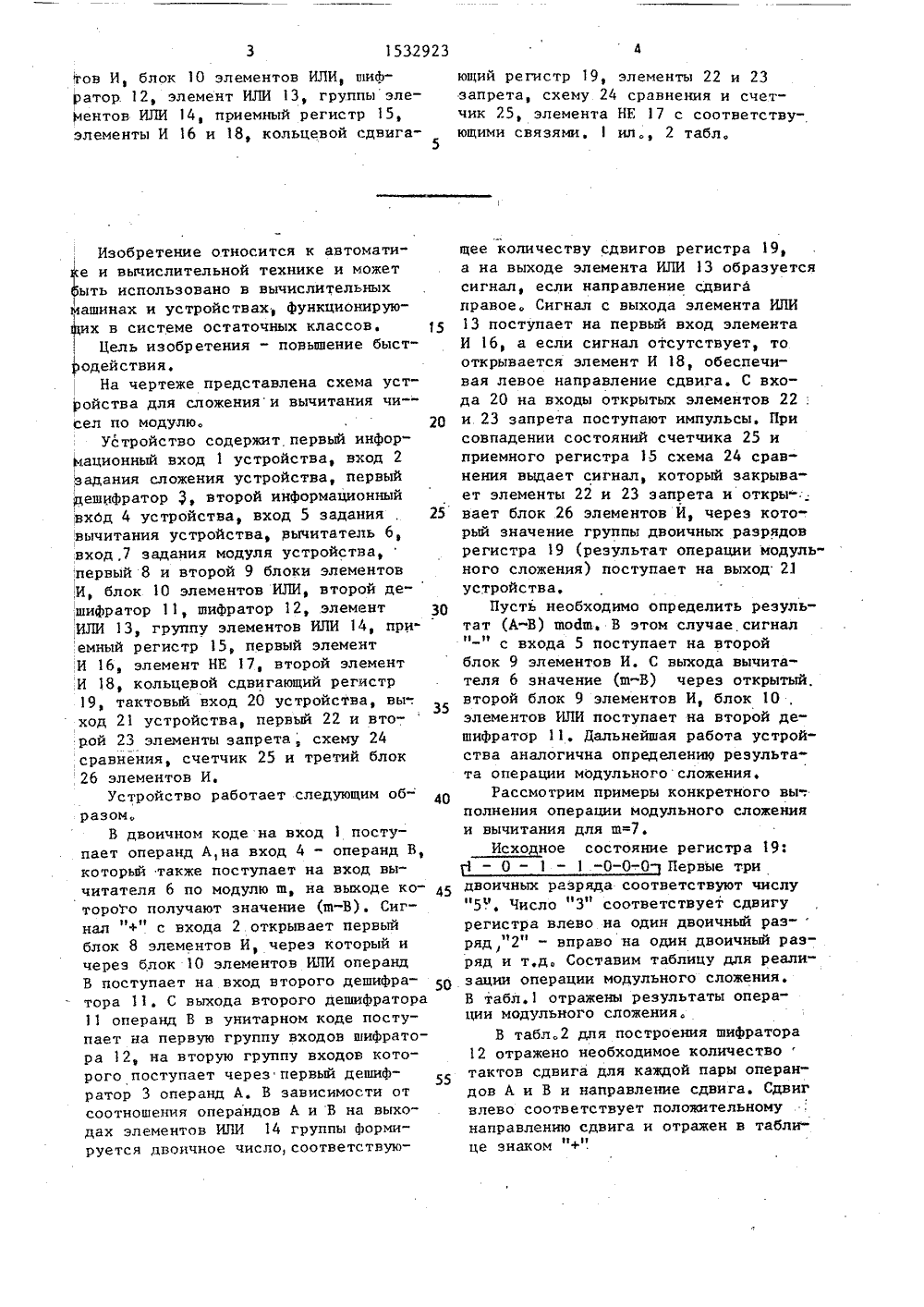

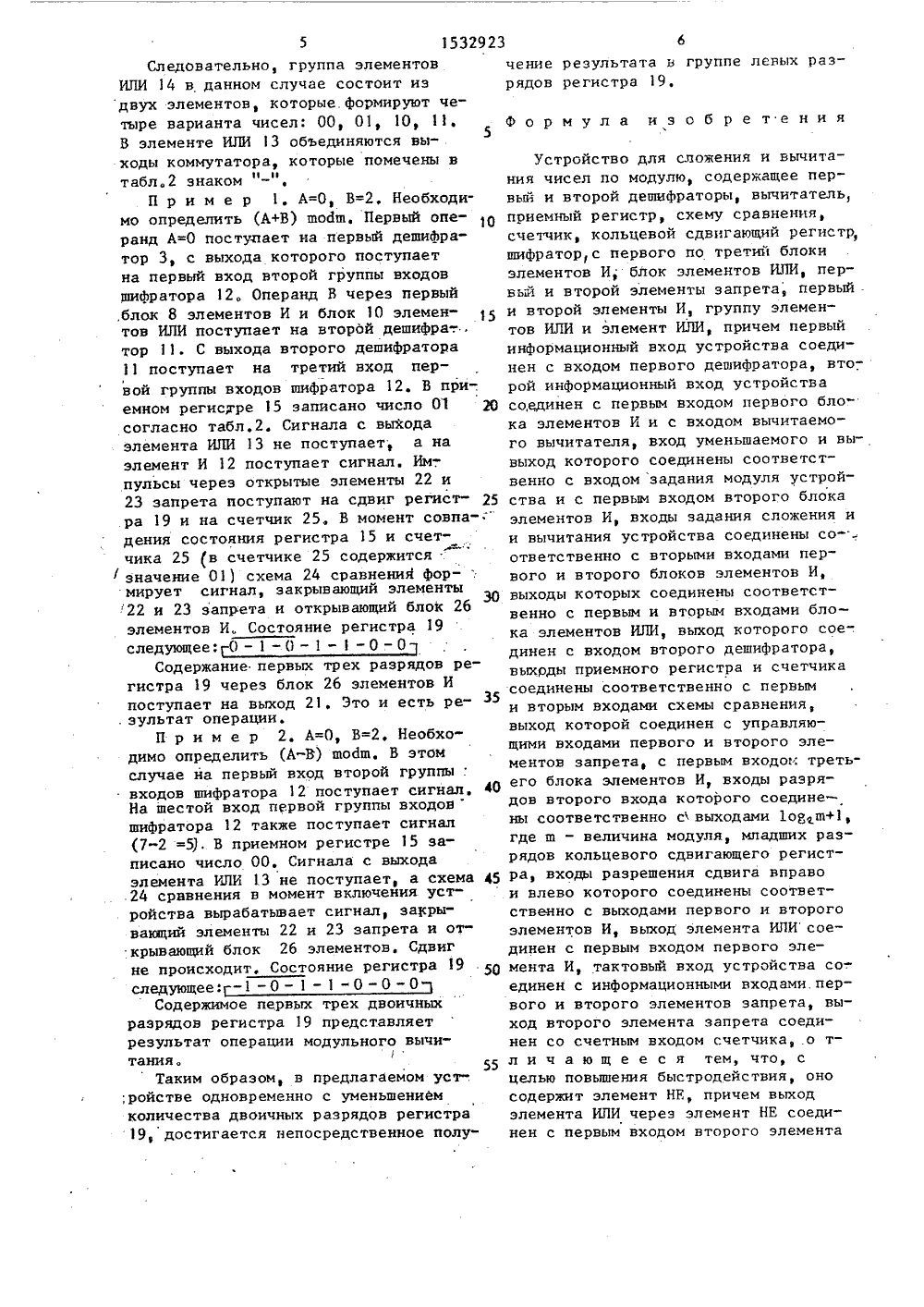

.и может тельныхционирую классов,в,влев.,ние быс ся за сч избыточн сдвигающе тат опера вычитания содер тел ГОСУДАРСТВЕННЫЙ НОМИТЕПО ИЗОБРЕТЕНИЯМ И ОТКРЫТПРИ ГННТ СССР Н АВТОРСМОМУ СВИ(56) Авторское свидетельство СССРР 1312572, кл. С 06 Р 7/72, 1985,Авторское свидетельство СССРВ 1388850, кл, С 06 Г 772, 1986,(54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИ ТАНИЯ ЧИСЕЛ ПО МОДУЛЮ 2 ретение относится к области и и вычислительной .техники ыть использовано в вычислиашинах и устройствах, функих в системе остаточных Цель изобретения - повышеодействия, Цель достигаетт устранения информационной сти разрядов кольцевого го регистра, хранящих резул ций модульного сложения ипутем введения в устройст жащее шифраторы 3 и 11, вы, блоки 8, 9 и 26 злемен1532923гов И, блок 10 элементов ИЛИ, шифратор. 12, элемент ИЛИ 13, группы элементов ИЛИ 14, приемный регистр 15, элементы И 16 и 18 кольцевой сдвигаю5 ющий регистр 19, элементы 22 и 23запрета, схему 24 сравнения и счетчик 25, элемента НЕ 17 с соответствующими связями,ил ., 2 табл.Изобретение относится к автоматие и вычислительной технике и может ыть использовано в вычислительных машинах и устройствах, функционируюих в системе остаточных классов. 15Цель изобретения - повышение быстодействия.На чертеже представлена схема устройства для сложенияи вычитания чи-" сел по модулю, 20Устройство содержит, первый инфорМационный вход 1 устройства, вход 2 ,задания сложения устройства, первый дешифратор , второй информационный вход 4 устройства, вход 5 задания , 25 вычитания устройства, вычитатель 6, вход,7 задания модуля устройства, первый 8 и второй 9 блоки элементов ;И, блок 10 элементов ИЛИ, второй де,шифратор 11, шифратор 12, элемент ИЛИ 13, группу элементов ИЛИ 14, приемный регистр 15, первый элемент И 16, элемент НЕ 17, второй элемент И 18, кольцевой сдвигающий регистр 19, тактовый вход 20 устройства, вы". ход 21 устройства, первый 22 и второй 23 элементы запрета, схему 24 сравнения, счетчик 25 и третий блок 26 элементов И,Устройство работает следующим об разомВ двоичном коде на вход 1 поступает операнд А,на вход 4 " операнд В, который также поступает на вход вычитателя 6 по модулю ш, на выходе ко торого получают значение (в-В). Сигнал "+" с входа 2 открывает первый блок 8 элементов И, через который и через блок 10 элементов ИЛИ операнд В поступает на вход второго дешифратора 11. С выхода второго дешифратора 11 операнд В в унитарном коде поступает на первую группу входов шифратора 12, на вторую группу входов которого поступает через первый дешифратор 3 операнд А. В зависимости от соотношения операндов А и В на выходах элементов ИЛИ 14 группы формируется двоичное число, соответствующее количеству сдвигов регистра 19,а на выходе элемента ИЛИ 13 образуетсясигнал, если направление сдвигаправое, Сигнал с выхода элемента ИЛИ13 поступает на первый вход элементаИ 16, а если сигнал отсутствует, тооткрывается элемент И 18, обеспечивая левое направление сдвига. С входа 20 на входы открытых элементов 22:и 23 запрета поступают импульсы. Присовпадении состояний счетчика 25 иприемного регистра 15 схема 24 сравнения выдает сигнал, который закрывает элементы 22 и 23 запрета и откры".вает блок 26 элементов И, через который значение группы двоичных разрядоврегистра 19 (результат операции модульного сложения) поступает на выход 21устройства.Пусть необходимо определить результат (А-В) шорш. В этом случае, сигнал"-" с входа 5 поступает на второйблок 9 элементов И, С выхода вычитателя 6 значение (ш-В) через открытый.второй блок 9 элементов И, блок 10,элементов ИЛИ поступает на второй дешифратор 11, Дальнейшая работа устройства аналогична определению результата операции модульного сложения.Рассмотрим примеры конкретного вы-.полнения операции модульного сложенияи вычитания для ш=7.Исходное состояние регистра 19:- 0 - 1 - 1 -0-0-0 Первые тридвоичных разряда соответствуют числу"5. Число "3" соответствует сдвигурегистра влево на один двоичный разряд,"2" - вправо на один двоичный разряд и т,д, Составим таблицу для реализации операции модульного сложения.В табл.1 отражены результаты опера"ции модульного сложения,В табл.2 для построения шифратора12 отражено необходимое количествотактов сдвига для каждой пары операндов А и В и направление сдвига. Сдвигвлево соответствует положительномунаправлению сдвига и отражен в таблице знаком +Следовательно, группа элементовИЛИ 14 в данном случае состоит издвух элементов, которые, Формируют четыре варианта чисел: 00, 01, 10, 11,5В элементе ИЛИ 13 объединяются выходы коммутатора, которые помечены втабл.2 знакомП р и м е р 1, А=О, В=2, Необходимо определить (А+В) шорш, Первый операнд А=О поступает на первый дешифратор 3, с выхода которого поступаетна первый вход второй группы входовшифратора 12, Операнд В через первый,блок 8 элементов И и блок 10 элементов ИЛИ поступает на второй дешифра-тор 11. С выхода второго дешифратора11 поступает на третий вход первой группы входов шифратора 12, В приемном регистре 15 записано число 01 20согласно табл,2, Сигнала с вьЖодаэлемента ИЛИ 13 не поступает, а наэлемент И 12 поступает сигнал, Им-,пульсы через открытые элементы 22 и23 запрета поступают на сдвиг регист.ра 19 и на счетчик 25, В момент совпа- "дения состояния регистра 15 и счет"чика 25 (в счетчике 25 содержитсязначение 01) схема 24 сравнений Формирует сигнал, закрывающий элементы22 и 23 запрета и открывающий блок 26элементов И. Состояние регистра 19следующее: 0 - 1 - 0 - 1 - 1 - 0 - 0Содержание первых трех разрядов регистра 19 через блок 26 элементов Ипоступает на выход 21. Это и есть ре. зультат операции,П р и м е р 2. А=О, В=2. Необходимо определить (А-В) шорш, В этомслучае на первый вход второй группы .входов шифратора 12 поступает сигнал, 40На шестой вход первой группы входовшифратора 12 также поступает сигнал(7-2 =5. В приемном регистре 15 записано число 00, Сигнала с выходаэлемента ИЛИ 13 не поступает, а схема 4524 сравнения в момент включейия устройства вырабатывает сигнал, закрывающий элементы 22 и 23 запрета и открывающий блок 26 элементов, Сдвигне происходит, Состояние регистра 19следующее; -1 - 0 - 1 - 1 - О - 0 - ОСодержимое первьх трех двоичныхразрядов регистра 19 представляетрезультат операции модульного вычитания,55Таким образом, в предлагаемом уст-.;ройстве одновременно с уменьшениемколичества двоичных разрядов регистра19, достигается непосредственное получение результата в группе левых разрядов регистра 19,Формула изобретенияУстройство для сложения и вычитания чисел по модулю, содержащее первый и второй дешифраторы, нычитатель, приемный регистр, схему сравнения, счетчик, кольцевой сдвигающий регистр, шифратор, с первого по третий блоки элементов И, блок элементов ИЛИ, первый и второй элементы запрета, первый . и второй элементы И, группу элементов ИЛИ и элемент ИЛИ, причем первый информационный вход устройства соединен с входом первого дешифратора, второй информационный вход устройства соЕдинен с первым входом первого бло" ка элементов И и с входом вычитаемого вычитателя, вход уменьшаемого и вывыход которого соединены соответственно с входом задания модуля устройства и с первым входом второго блока элементов И, входы задания сложения и и вычитания устройства соединены соответственно с вторыми входами первого и второго блоков элементов И выходы которых соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого сое-. динен с входом второго дешифратора, выхрды приемного регистра и счетчика соединены соответственно с первым и вторым входами схемы сравнения, выход которой соединен с управляющими входами первого и второго элементов запрета, с первым входом третьего блока элементов И, входы разрядов второго входа которого соединены соответственно с выходами 1 орш+1, где ш - величина модуля, младших разрядов кольцевого сдвигающего регистра, входы разрешения сдвига вправо и влево которого соединены соответственно с выходами первого и второго элементов И, выход элемента ИЛИ соединен с первым входом первого элемента И, тактовый вход устройства со-. единен с информационными входами.первого и второго элементов запрета, выход второго элемента запрета соединен со счетным входом счетчика, .о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит элемент НЕ, причем выход элемента ИЛИ через элемент НЕ соеди" нен с первым входом второго элемента1532923 Т а б л и ц а 1 И, второй вход которого объединен с в в горым входом первого элемента И и соединен с выходом первого элемента запрета, выход третьего блока элементов И является выходом устройства, . выходы второго и первого дешифраторов соединены соответственно с входапервой и второй групп шифратора, в осоды которого соединены с соответс вующими входами элемента ИЛИ и элентов ИЛИ группы, выходы элементовИ группы соединены с входами сооттствующих разрядов приемного рестра. 15 0 1 2 3 4 5 6 1 2 3 4 5 6 0 2 3 4 5 6 03 4 5 6 0 1 2 4 5 6 О 1 2 3 5 6 О2 34 6 0 1 2 3 4 5 0 1 2 3 4 5 6 Таблица 2 3- 2- 2- 1" 1- 1+ 1+ 3+ 3+ 0 0 2+ 2+ 33+ О 2+ О 2+ 3- 2+ 3" 21+ 1+ 3+ 3+ 0 0 2+ 2+ 3- 3- 22- 1- 1+ 1- 1+ 3+ 1+ 3+ 0 Составитель А.Клюевская ТехредЛОлийнык Редактор Л,Пчо Кучерявая Коррек Заказ 8100/53 Тираж 668 ПодписноеЗНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 изводстненно-издательский комбинат "Патент", г,ужгород, ул. Гагарина,0

СмотретьЗаявка

4430083, 24.05.1988

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ФОМЕНКО ОЛЕГ НИКОЛАЕВИЧ, КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ, ИРХИН ВАЛЕРИЙ ПЕТРОВИЧ, ПАНКОВ ВЛАДИМИР МИХАЙЛОВИЧ, ЖУРАВЛЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ИВАНОВ СЕРГЕЙ ВИКТОРОВИЧ, КУЦЫЙ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: вычитания, модулю, сложения, чисел

Опубликовано: 30.12.1989

Код ссылки

<a href="https://patents.su/4-1532923-ustrojjstvo-dlya-slozheniya-i-vychitaniya-chisel-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сложения и вычитания чисел по модулю</a>

Предыдущий патент: Устройство цифрового интегрирования

Следующий патент: Устройство для формирования позиционного признака в модулярной арифметике

Случайный патент: Способ получения органоциансиланов