Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

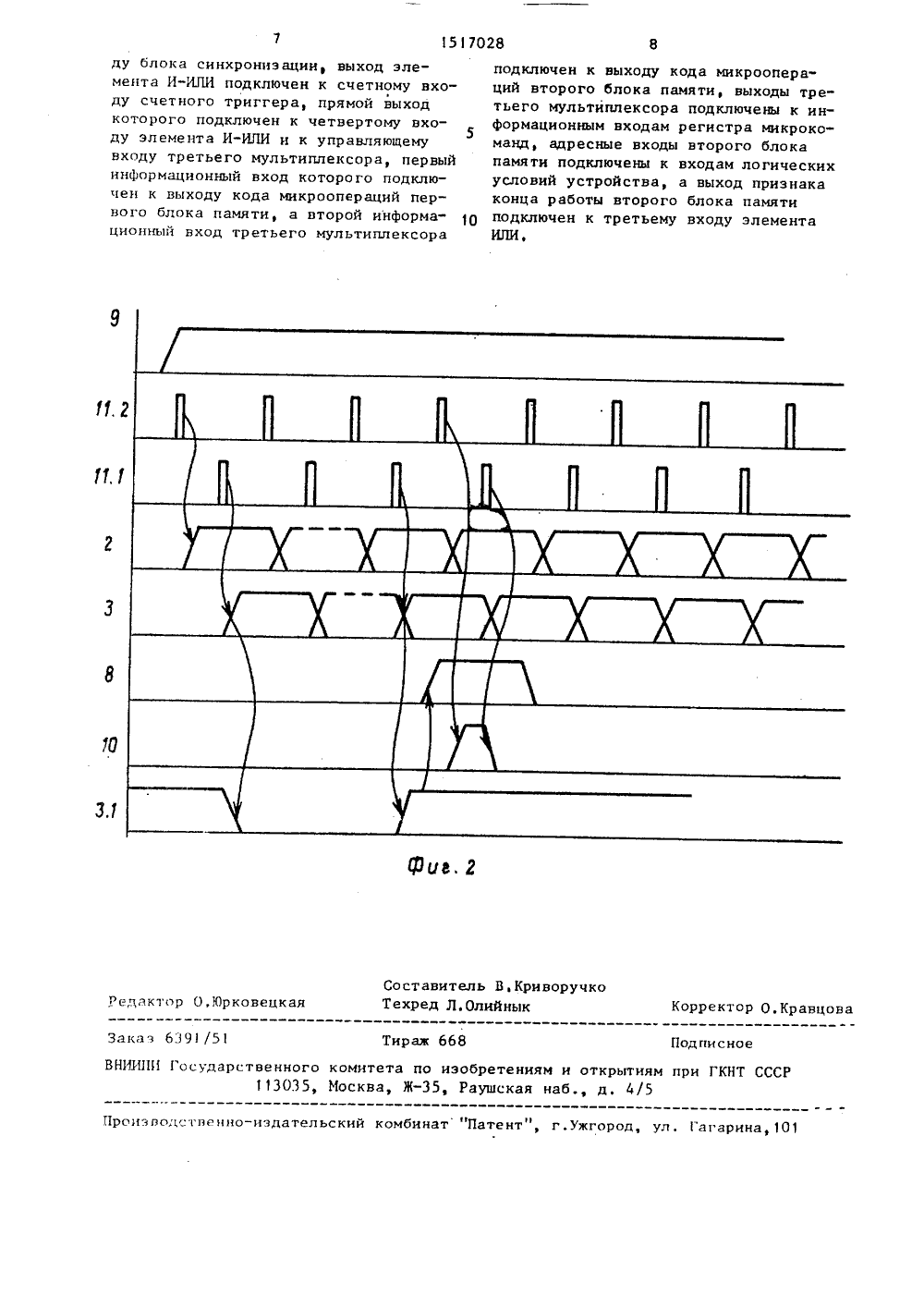

(51)4 С 06 Г 9/22 ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ М Ф К) Фиг ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССРВ 114021, кл. С 06 Г 9/22, 1984.Майоров С,А., Новиков Г,И. Структура электронных вычислительных машин,-Л.: Машиностроение, 1979, с, 314,,рис. 10.4. 254) МИКРОПРОГРАММНОЕ УСТРОЛСТВО УПРАВЛЕНИЯ(57) Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системахпрограммного логического управлениятехнологическими процессами. Цельизобретения - повышение быстродействия, Устройство содерящт первый блокпамяти 1, регистры адреса 2 и микрокоманд 3, с первого по третий мультиплексоры 4-6, второй блок памяти 7,дешифратор 8, КЯ-триггер 9, счетный4триггер 1 О, блок синхронизации 11,элемент И-ИЛИ 12, элемент ИЛИ 13 иэлемент И 14, 2 ил, 157028зобретенце относится к вычислительной технике и Может быть использовацо в автоматизированных системахпрограммшого логического управления5технологическими процессами,.елью изобретения является повыше 1 п 1 с быстродействия устройства,1 а фцг.представлена функциональная схема микропрограммного устройст Ова упр,.вленця, на фиг, 2 - временнаядиаграмма работы устройства,1 Шкропрограммное устройство управления содерсит первый блок 1 памяти,нмеюшцй выход 1,1 кода адреса, старший разряд 11кода и адреса, выход 1,2 кода условия и выход 1,3 код мцкроопсраццйрегистр 2 адреса,регистр 3 микрокоманд, имеющий ьыходы признаков конца команды 3.1 и конца работы 3,2, с первого по третиймультиплексоры 4-6, второй блок 7 памяти имеющий выход 7,1 кода мцкрооперацпй и тзыход 7,2 признака конца работы, дешц,ратор 8, КВ-триггер 9, 25четный триггер 1 О, блок 11 синхронизации, имеющий выходы 11,1 и 11,2первого и второго режимов синхронизации, элемент ИлИ 12 элемент ИП 1 13,элс.ент 11 14 входы 15 код операции,Овыходе. 16 микраопграций вход 17 пусвхэд 18 останова и входы 19 логических условий.1 пкропрс граммцое устройство управлеп,.я раоотает следующим образом,11 а входы 15 устройства подаетсякод операции, а на вход 17 пуска - импульс пуска, по которому устанавливается в "1" ВЛ-триггер 9, Выхоцной сигнал триггера 9 запускает блок 11 син Охроппэ ациц, который начинает генерироьа чь дпееперекрывающиеся последовате-,льности импульсов на выходах 11.1 и1,2, Б исходном положении все регистры ц триггеры обнулены(цепи не покззьнь 1) . поэтому информация с выходовму.:ьз цплексора 4 записывается в регцср 2 по заднему фронту импульсавыходе 11,2 блока 11, так как актпьпре:эп первый (инверсный) вход элемент,. 11 14. Выходные сигналы регистра2 ядре уст первый блок 1 памяти, и наего ь.:. дах уст;навливается информацц : па вых-де 1, 1 - адрес следующейячейки ппя п; старший разряд 1, 1, 1выхс 1 ц;: 1, 1 епользуется для безусловиог 1 формирования адреса следующеия сйкпэмятц, на выходе 1.2 устанав:пм;петен ед логического условия, поступающего на мультиплексор 5Приналичии нулевой информации на выходе1,2 мультиплексор 5 коммутирует насвой выход информацию с выхода 1,1,1первого блокапамяти и происходитбезусловное формирование адреса следующей ячейки памяти независимо отлогических условий на входах 19, Навыходе 1,3 первого блока 1 памятиустанавливается информация микроопераций, поступающая на мультиплексор6, которая и коммутируется на его выходы, так как счетный триггер 10, управляющий его входами, обнулец, Информация микроопераций записывается врегистр 3 по заднему фронту импульсана выходе 11.1 блока 11 синхронизации,Таким образом на выходах 16 устройства устанавливается информация микроопераций, а на выход 3,1 регистра 3подается логическая "1", По следующему импульсу на выходе 11,2 блока 11синхронизации в регистр 2 с выходовмультиплексора 4 записывается адресочередной ячейки первого блока 1 памяти, С первого блока 1 памяти вновьсчитывается информация об адресе следующей ячейки памяти (выход 1.1), коде логических условий (выход 1.2) имикрооперациях (выход 1,3), В зависимости от логических условий, кодалогических условий выход 1.1 в конкатенации с выходом мультиплексора5 формируют адрес следующей ячейкипамяти, Так же по импульсу на выходе11.1 блока 11 очередная информациямикроопераций записывается в регистр3 и устанавливается ца выходах 16 устройства, Далее устройство работаетаналогично до тех пор, пока на выходе3,1 регистра 3 не появится логический"О, свидетельствующий о завершениикоманды, Тогда в регистр 2 будет записан адрес очередной команды с входов 15 кода операции,Далее устройство работает аналогично до появления на выходе 3,2 регистра 3 логической , свидетельствующей об окончании работы, Это приводит к сбросу ВБ-триггера 9 по второму входу элемента ИЛИ 13. В связи с этим останавливается блок 11 синхронизации и работа устройства завершается, ЕБ в тригг 9 может быть также обнулен сигналом на входе 18 останова по первому входу элемента ИЛИ 13151702 Причем по окончании обработки очередного кода, операции, поступившего на входы 15 устройства, на выходе 3.1 регистра 3 устанавливается сигнал логической "1", который активирует вход разрешения дешифратора8, дешифрующего код операции с соответствунщих входов 15 устройства, В случае, если этот код соответствует операции по вычислению системы булевых функций, активируется выход дешифратора 8, Выход дешифратора Я активирует первый вход элемента И-ИЛИ 12 блокирует по первому входу элемент И 14, поэто му очередной импульс на выходе 11,2 блока 11 по второму входу элемента И-ИЛИ 12 задним фронтом устанавливает счетный триггер 10, Выходной сигнал счетного триггера 10, равный логичес кой "1 п активирует четвертый вход элемента И-ИЛИ 12 и управляющий вход мультиплексора 6, в связи с чем он коммутирует на свои выходы выход кода микроопераций второго блока 7 па мяти, Последний реализует аппаратно заданную систему булевых функций над аргументами логических условий, выставленных на входах 19 устройства, Поэтому управляющие сигналы, сформированные на выходе 7,1 по импульсу на выходе 11,1 блока 11 синхрониз ации, записываются в регистр 3 и устанавливаются на выходах 16 устройства, Одновременно этим же импульсом по третьему входу элемента И-ИЛИ 12 обнуляется счетный триггер 10, На входы 15 кода операции поступает код очередной операции, поэтому мультиплексор 4 коммутирует на свои выходы информацию, По очередному импульсу на выходе 11,2 блока 11 информация с входов 15 устройства записывается в регистр 2, так как первый вход элемента И4 не активирован выходом дешифратора 8, В дальнейшем устройство работает аналогично, При появлении на выходе 7,2 второго блока 7 памяти логической "1" по третьему выходу элемента ИЛИ 13 обнуляется ВБ-триггер 9, и работа устройства прекращается,формула изобретения Иикропрограмное устройство управ 35ления, содержащее блок синхронизации,первый блок памяти, регистр адреса,регистр микрокоманд, первый и второймультиплексоры, 1,й-триггер и элемент 8 6ИЛИ, причем первый информационньй вход первой группь первого мультиплексора соединен с выходом второго мультиплексора, первый информационный вход которого соединен с выходом модифицируемого разряда адреса первого блока памяти, выходы поля немодифицируемых разрядов адреса которого соединены с остальными информационными входами первой группы первого мультиплексора, остальные инФормационные входы второго мультиплексора являются входами логических условий устройства управляющий вход второго мультиплексора подключен к выходу кода условий первого блока памяти, вторая группа информационных входов первого мультиплексора является входами кода операции устройства, управлякщий вход первого мультиплексора подключен к выходу признака конца команды регистра микрокоманд, выходы первого мультиплексора подключены к информационным входам регистра адреса, выходы которого подключены к адресным входам первого блока памяти, Б-вход В 1- триггера является входом пуска устройства, В -вход ББ-триггера подключен к выходу элемента ИЛ 1 первый вход которого является входом оста- нова устройства, а второй вход элемента ИЛИ подключен к выходу признака конца работы регистра микрокомаид, прямой вьход Р 5-триггера подключен к входу пуска блока синхронизации, первый выход которого подключен к входу синхронизации регистра юкрокоманд, выходы кода микроопераций которого являются одноимеиыми выходами устройства, о т л и ч а ю - щ е е с я тем, что, с целью 1 выевя быстродействия, оио содержит второй блок памяти, счетный триггер, третий мультиплексор, дешифраторэлемент И- ИЛИ и элемент И, при;ем информационные входы дешифратора подкл чеиы к входам кода операции устройства, а вход разрешения депифратора подслючен к выходу признака конца команды регистра микрокомаид, выход дешифратора подключен к перво входу элемента И и к первому входу элементе 11-1.И второй вход которого подключе к к,- ходу второго блока сихроижи и к второму входу элемента И, я.хе эле - мента И подключен к входу сихро- ции регистра адреса, третй вх, и э:емента И-ИЛИ подключен кс ру выхо -15 7028 О Составитель В,Криворучко Техред Л.Олийнык Корректор О,Кравцова едактор О ецкая Подписноепри ГКНТ СС Тираж 6 каэ 639/51 ИИПИ Государственного комитета по изобретениям и открытия 113035, Москва, Ж, Раушская наб., д. 4/5 роиэлодстленно-издательский комбинат пПатент , г.ужгород, ул. Гагарина,10 ду блока синхронизации, выход элемента И-ИЛИ подключен к счетному входу счетного триггера, прямой выходкоторого подключен к четвертому входу элемента И-ИЛИ и к управляющемувходу третьего мультиплексора, первыйинформационный вход которого подключен к выходу кода микроопераций первого блока памяти, а второй информационный вход третьего мультиплексора подключен к выходу кода микроопераций второго блока памяти, выходы тре" тьего мультиплексора подключены к информационным входам регистра микрокоманд, адресные входы второго блока памяти подключены к входам логических условий устройства, а выход признака конца работы второго блока памяти подключен к третьему входу элемента ИПИ,

СмотретьЗаявка

4404986, 01.03.1988

ПРЕДПРИЯТИЕ ПЯ Г-4651

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.10.1989

Код ссылки

<a href="https://patents.su/4-1517028-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Функциональный преобразователь координат

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Способ цементации стальных изделий