Устройство нисневича для обнаружения и исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1474654

Автор: Нисневич

Текст

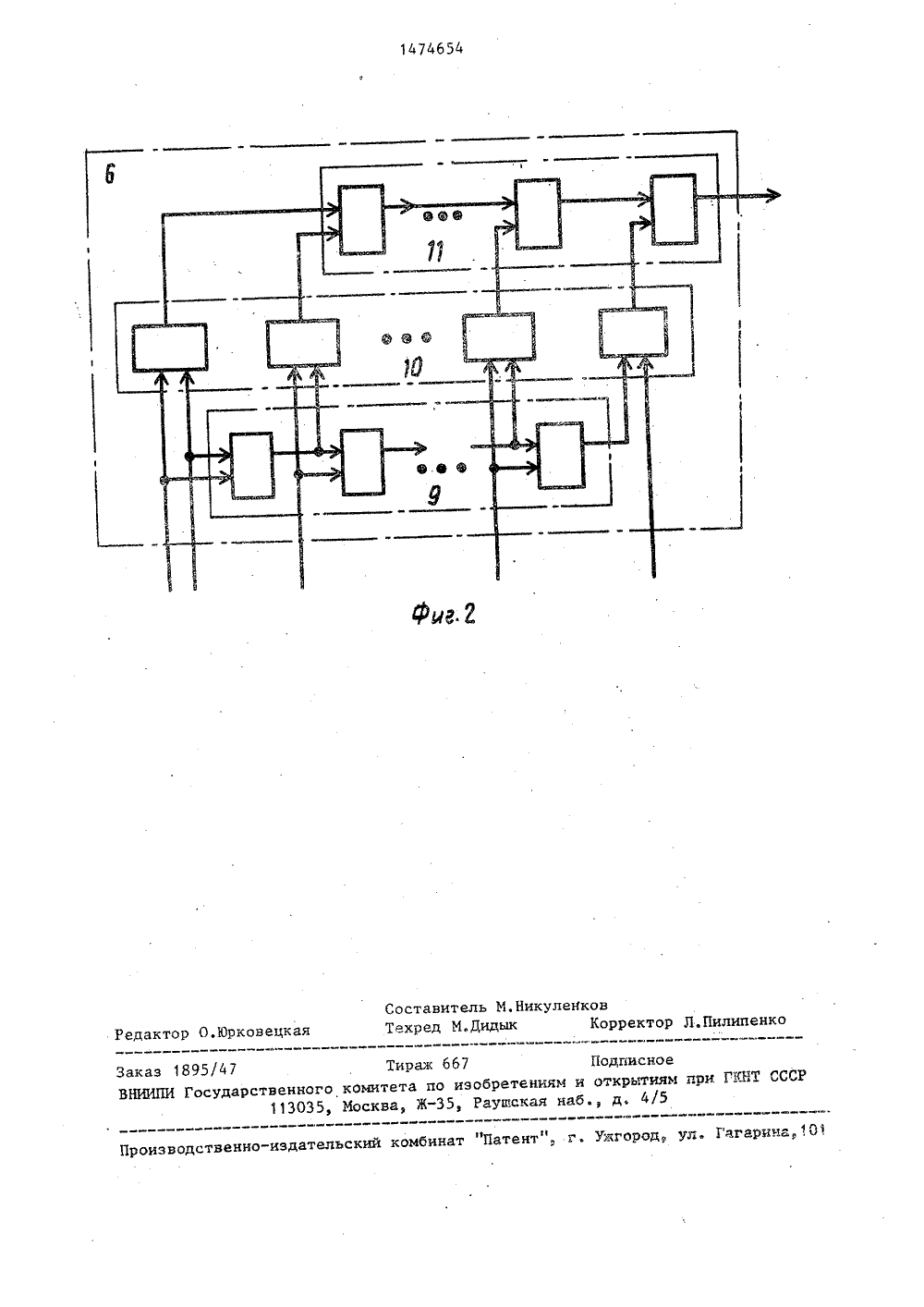

сэ 03 сОВетснихсоцидлистичеснихРЕСПУБЛИН 4 С 06 28 Н 03 М 13 СР 83 82. ОБНАРУктГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯпРи пнт сссР АВТОРСКОМУ СВМДЕТЕЛЬСТ(56) Авторское свидетельство СВ 1162053, кл. Н 03 К 13/00, 1Авторское свидетельство ССС9 1136168, кл, С 06 Р 11/22, 1(54) УСТРОЙСТВО НИСНЕВИЧА ДЛЯЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК(57) Изобретение относится к эросвязи, вычислительной техникможет использоваться в система 801474654 работки, хранения и передачи информации. Устройство обнаруживает многократные и исправляет одиночные ошибки двоичной информации, переданнойв парафазном коде, что обеспечиваетповышение достоверности устройства,Устройство содержит группу 1 элементов РАВНОЗНАЧНОСТЬ, сумматоры 2,3 по модулю два, элементы 4, 5 ИЛИ,блок 6 обнаружения ошибок, группу 7элементов И и групгу 8 элементов НЕРАВНОЗНАЧНОСТЬ. Устройство позволяетобнаруживать многократные и исправлять одиночные ошибки. 1 з,п. ф-лы,2 ил.Изобретение относится к электросвязи, вычислительной технике и может использоваться в системах обработки, хранения н передачи информацииЦелью изобретения является повышение достоверности работы устройства.На Фиг, 1 представлена Функциональная схема устройства Нисневича для обнаружения и исправления ошибок на фиг. 2 - функциональная схема. блока обнаружения ошибок.Устройство Нисневича для обнаружения и исправления ошибок содержит (фиг. 1) группу 1 элементов РАВНОЗНАЧНОСТЬ, первый и второй сумматоры 2 и 3 по модулю два, первый и второй элементы ИЛИ 4 и 5, блок 6 обнаружения ошибок, группу 7 элемен" тов И и группу 8 элементов НЕРАВНОЗНАЧНОСТЬ.Блок 6 обнаружения ошибок содержит (фиг. 2) группу 9 элементов ИЛИ, группу 10 элементов И и группу 11 элементов ИЛИ.Устройство реализовано на следующих микросхемах: группа 1 элементов РАВНОЗНАЧНОСТЬ - 155 ЛП 5 и 155 ЛН 1, сумматоры 2 и 3 по модулю два - 155 ИП 2, элементы ИЛИ 4 и 5 - 155 ЛЛ 19 группы 7 и 10 элементов И - 155 ЛИ 1, группа 8 элементов НЕРАВНОЗНАЧНОСТЬ - 155 ЛП 5, группы 9 и 11 элементов ИЛИ - 155 ЛЛ 1.Устройство работает следующим образом.На входы устройства информация поступает в парафазном коде, т.е, каждый разряд передается двумя сигналами - "0" и "1". Оба сигнала каждого из разрядов подаются на соот. - ветствующие элементы РАВНОЗНАЧНОСТЬ группы 1, на которых обнаруживается наличие ошибки в разрядах.,На ошибку указывают одинаковые значения сигналов на входах элементов РАВНОЗНАЧНОСТЬ.Нулевые и единичные значения разрядов контролируемого кода поступают соответственно на сумматоры 2 и 3 по модулю два. Единичное значение сигнала на выходе сумматоров 2 и 3 указывает на ошибки нулевых или единичных значений кода числа соответственно.Исправление одиночных ошибок дсуществляется следующим образом.Пусть на один из парафаэных входов устройства вместо правильной ком 30 35 40 группы 1. Это число подсчитывается блоком 6 в параллельном коде. Если число выявленных искажений (логических "1" на выходах элементов РАВНОЗНАЧНОСТЬ) равно или более двух, то исправить такую ошибку устройство не может, На выходе блока 6 появляется уровень логической "1", означающий неисправимую ошибку.Сигнал ошибки формируется даже в тех случаях, когда прототип ее либо не выявляет (число искажений только в прямом или инверсном кодах четно), либо распознает и исправляет ошибочно (когда условие контроля чет 45 50 55 ности вызывает срабатывание только одного из сумматоров 2 или 3).Устройство выявляет эти ошибки, извещает о них внешние приборы и блокирует работу элементов И .группы 7, оставляя выходной код идентичным входному на случай, если внешние приборы смогут использовать или восстановить информацию другими средствами.Блок 6 обнаружения многократных ошибок работает следующим образом (фиг, 2).Если на первых двух входах блока 6 присутствуют уровни логических "1",бннации 10 поступает комбинация 00.Ошибка обнаруживается соответствующим элементом РАВНОЗНАЧНОСТЬ группы 1. Сигнал с его выхода поступает на входы, соответствующих двух элементов И группы 7. Одновременно ошибка обнаруживается сумматором 2, с выхода которого на вход элементов И группы 7 поступает единичньй сигнал,.10 с выхода нечетного элемента И группы 7соответствующей пары на вход соответствующего элемента НЕРАВНОЗНАЧНОСТЬ группы 8 поступает сигнал логической "1". На второй вход этого элемента НЕРАВНОЗНАЧНОСТЬ поступает ошибочный нулевой сигнал, на выходе данного элемента НЕРАВНОЗНАЧНОСТЬ формируется откорректированный сигнал 11 ц20Обнаружение искажений двойной иболее кратности осуществляется следующим образом.Каждое искажение входного кода(совпадение логических уровней прямого и инверсного кодов) выделяется элементами РАВНОЗНАЧНОСТЬ группы 1.Числу выявленных искажений соот-ветствует число логических единиц на выходах элементов РАВНОЗНАЧНОСТЬто последовательно срабатывают соответствующие элементы И группы 10 и элементы ИЛИ группы 11,и на выходе блока 6 появляется уровень логической "1", Если уровень логической "1" - только на первом входе блока 6, то первый элемент И группы 10 не срабатывает, сигнал логической "1" транслируется первым элементом ИЛИ группы 9 для сложения с уровнем на третьем входе блока 6, Если на третьем входе - уровень логической "1", то срабатывает второй элемент группы 10, "1" с выхода которого через элементы ИЛИ группы 11 ретранслируется на выход блока 6. Если на третьем входе блока 6 - уровень ло,гического "0", то "1" транслируется элементами ИЛИ группы 9 до конца группы и, если на пути встречается еще хотя бы одна логическая "1" на одном из входов, то срабатывает соответствующий элемент И группы 10 "1" с выхода которого передается на выход блока б элементами ИЛИ группы 11.Таким образом, устройство позволяет повысить достоверность при контроле и восстановлении информации по модулю два, обнаруживая многократные ,и исправляя одиночные ошибки.формула изобретения1, Устройство для обнаружения иисправления ошибок, содержащее группу элементов РАВНОЗНАЧНОСТЬ и группу элементов НЕРАВНОЗНАЧНОСТЬ, сумматоры, первые входы элементов РАВНОЗНАЧНОСТЬ группы объединены с соответствующими входами первого сумматора и первыми входами соответствующих нечетных элементов НЕРАВНОЗНАЧНОСТЬ группы и являются первыми входами устройства, вторые входы элементов РАВНОЗНАЧНОСТЬ группы объеди 45 нены с соответствующими входами второго сумматора и первыми входами соответствующих четных элементов НЕ" РАВНОЗНАЧНОСТЬ группы и являются вторыми входами устройства, группу элементов И, выходы которых соединены с вторыми входами одноименных элемен-) тов НЕРАВНОЗНАЧНОСТЬ группы, выходы которых являются информационными выходами устройства, о т л и ч а ющ е е с я тем, что, с целью повыше ния достоверности работы устройства,в него введены элементы ИЛИ и блокобнаружения ошибок, выход первогосумматора соединен с первым входомпервого элемента ИЛИ, выход которогосоединен с первыми входами нечетныхэлементов И группы, выход второгосумматора соединен с первым входомвторого элемента ИЛИ, выход которого соединен с первыми входами четных элементов И группы, выходы эле"ментов РАВНОЗНАЧНОСТЬ группы соединены с соответствующими входами блока обнаружения ошибок и вторыми входами соответствующих попарно объединенных четных и нечетных элементовИ группы, выход блока обнаруженияошибок соединен с вторыми входамипервого и второго. элементов ИЛИ иявляются контрольным выходом устройства,. .2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок обнаружения ошибок содержит группы элементов ИЛИ и группу элементов И, первый вход первого элемента ИЛИ первой группы объединен с первым входом первого элемента И группы и является соответствующим входом блока обнаружения ошибок, выход каждого -го элемента ИЛИ первой группы (х1, Мсоединен с первьм входом (+1)-го элемента ИЛИ первой группы и (+1.1-го элемента И группы, выход Ч-го элемента ИЛИ первой группы соединен с первым входом (И+13-го элемента И группы, второй вход которого является соответствующим входом блока обнаружения ошибок, выход первого элемента И группы соединен с первым входом первого элемента ИЛИ второй группы, выход каждого предыдущего элемента ИЛИ второй группы соединен с первым входом последующего элемента ИЛИ второй группы, выход -го элемента И группы (х = 2, И+1 соединенс вторыми входом (-11-го элемента ИЛИ второй группы, выход последнего элемента ИЛИ второй группы является выходом блока обнаружения ошибок.ректор Л,Пилипенко Под тенинм и отк скан наб., д изводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101 аз 1895/47 Тиоаж бб 7 НИИПИ Государственного коиитета по изоб 113035, Москва, Ж, Ратини при ГКЯТ СС4/5

СмотретьЗаявка

4275963, 06.07.1987

М. С. Нисневич

НИСНЕВИЧ МАРКС СОЛОМОНОВИЧ

МПК / Метки

МПК: G06F 11/28, H03M 13/05

Метки: исправления, нисневича, обнаружения, ошибок

Опубликовано: 23.04.1989

Код ссылки

<a href="https://patents.su/4-1474654-ustrojjstvo-nisnevicha-dlya-obnaruzheniya-i-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство нисневича для обнаружения и исправления ошибок</a>

Предыдущий патент: Устройство для включения и перезапуска микропроцессора при сбоях питания

Следующий патент: Устройство для контроля времени выполнения программы

Случайный патент: Устройство для измерения времени переключения радиостанции