Устройство для обнаружения ошибок в блоках памяти программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

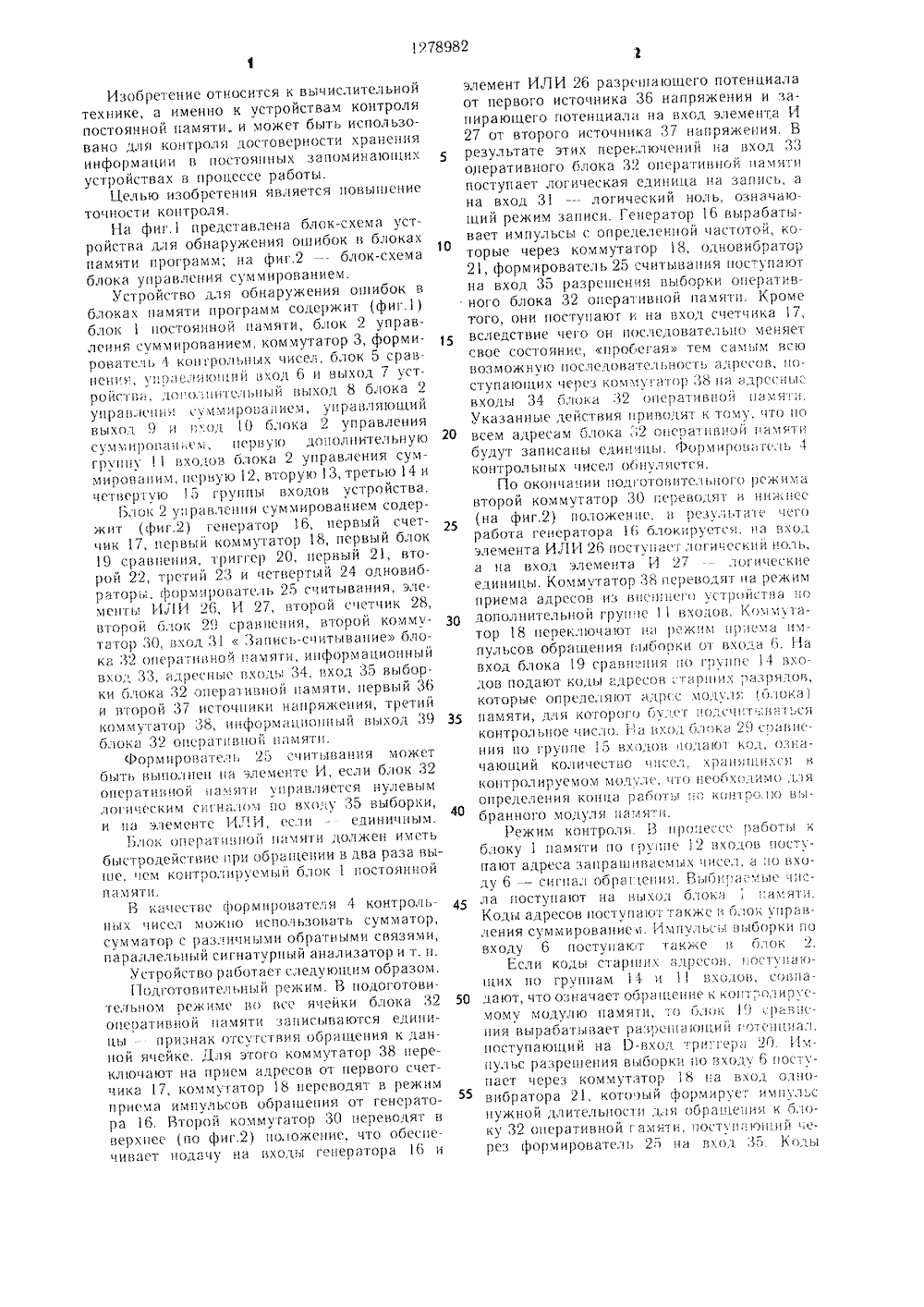

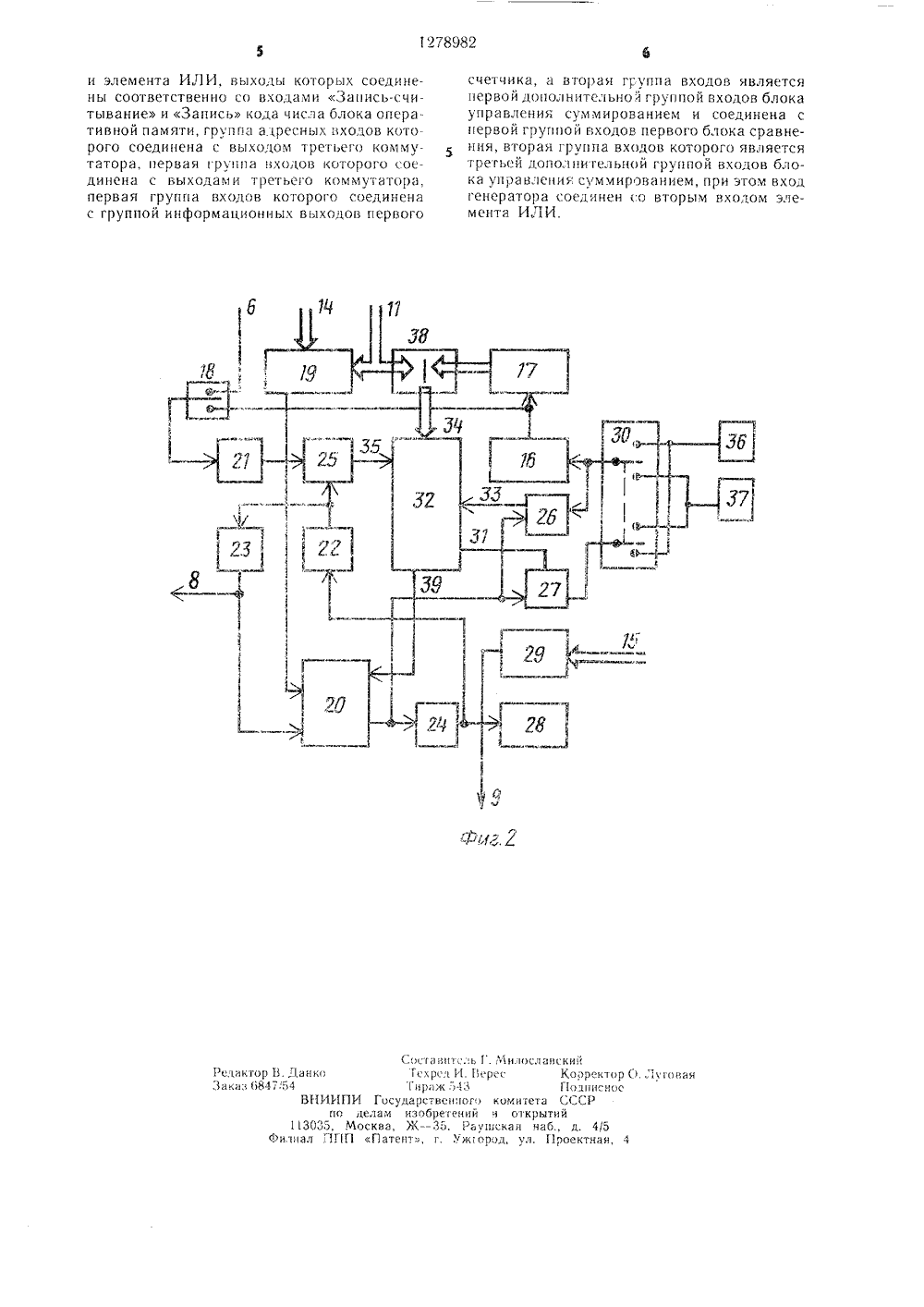

(19) (1 78982 11 С 29 ФЪД1 ИСАНИЕ ИЗОБРЕТЕНИ ГОСУДАРСТВЕННЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ А ВТОРСНОМУ СЕИД.".ТЕПЬСТ 3474308/24-2423.07.82(71) Московский ордена Ленина и ордена Октябрьской Революции энергетический институт(54) УСТРОИСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В БЛОКАХ ПАМЯТИ ПРО- ГРАММ(57) Устройство для обнаружения ошибок в блоках памяти программ относится к области вычислительной техники. Изобретение позволяет повысить точность контроля блоков памяти программ за счет обнаружения ошибок непосредственно в процессе работы. Обнаружение ошибок производится за счет вычисления контрольного числа совокупности считанных слов, принадлежащих контролируемому модулю памяти, и сравнения с эталонной константой. Устройство позволяет обеспечить однократный учет каждого считанного слова даже при многократном обращении к нему. Устройство содержит блок 1 памяти программ, блок 2 управления суммированием, коммутатор 3, формирователь 4 контрольных чисел, блок 5 сравнения. 2 з.п. ф-лы, 2 ил,Изобретение относится к вычислительной технике, а именно к устройствам контроля постоянной памяти, и может быть использовано Лля контроля достоверности хранения информапии в постояцных запоминающих устройствах в процессе работы.Целью изобретения является повышецие точности контроля.На фиг.1 представлена блок-схема устройства для обнаружения ошибок в блоках памяти программ; ца фиг.2 -- блок-схема блока управлеция суммированием.Устройство для обнаружения ошибок в блоках памяти программ содержит (фиг.1) блокпостоянной памяти, блок 2 управлеция суммированием, коммутатор 3, формирователь 4 коцгрольцых чисел, блок 5 сравцец 5., )110;)вл;11 с)1151 вход 6 и выход 7 мстройств, лоол;1 цтслгиый выход 8 блока 2 управ,1 сИР 151 сх мл 1 ироьациеы, управ.151 Ощий выход 9 и цхо,Е О блока 2 управления суммцрошц,ем, первую дополнительную группу 11 вход)в блока 2 управления суммировыцим, первую 12, вторую 13, третью 14 и цетвертукэ 15 группы входов устройства.Блок 2 упрывлеция суммированием содержит (фРг,2) генератор 16, первый счетчик 7, первый коммутатор 18, первый блок 19 сравнения, триггер 20, первый 21, второй 22, третий 23 и цетвертый 24 одновибраторы, формирователь 25 считывания, элементы ИЛИ 26, И 27, второй счетчик 28, е)торОЙ О,Ок 29 срявцсци 5), вторОй коммутатор 30, вход 31 Зе)ИРсь-с)РЕТЕвыцие блока 32 оперативкойаяяти, информационный вход 33, ылс)есцыс входы 34, хол 35 выборки Олокы 32 оперативной памяти, первый 36 и второй 37 источники напряжения, третий коммутатор 38, ицформыццоцць)й выход 39 смока 32 опсрытивцой ц;Мяти.Формирователь 25 считывация может быть выцолцец цы элемецтс И, если блок 32 оцеративцой цам 5 гги управляется нулевым логицсским сигналз по входу 35 выборки, и на элементе ИЛИ, с.ели - единичцым.Блок оперативно памяти должен иметь быстродействие при обры)пении в два раза вып)с, 1 сы коцтрОлцрмсмыи О;1 Ок 1 пост 051 ИОЙ памяти.В кысс 1)с с)Ормроватсл 51 4 кочтрольных чисел можно использовать сумматор, сумматор с различными обратными связями, параллелыый сигнатурцый анализатор и т. ц.Устройство работает следующим образом.Подготовительный режим. В цодоготовительном режиме во вес ячейки блока 32 оперативно й памяти з анисьи) а ются едиципы признак отсутствия обращения к данной яцейке.,елля этого коммутатор 38 иереключают цы прием адресов от первого счетчика 17, коммутатор 18 переводят в режим приема импульсов обращеция от генератора 16. Второй коммутатор 30 переводят в верхс.с по фиг.2) цо,1 ожсцие, что обеспечивает Олячу ея входы гецер 210 ра 16 и 5 1 О 15 20 25 30 35 40 45 50 55 элемент ИЛИ 26 разрсцык)щего потенциала от первого источника 36 напряжения и запирающего гОтецциалс) на вход элемецта И 27 от второго источника 37 цыпряжеция. Б результате этих псреключеций иа вход 33 011 еративного блока 32 оперативной памяти поступает логическая едиципа ца запись, а на вход 31 -- логический ноль, озцачык)- щий режим записи. Гееератор 16 вырабатывает импульсы с определеццой частотой, которь)е через коммутатор Е 8, олновибратор 21, формирователь 25 считывания цос-упают на вход 35 разрепеция выборки оперативного блока 32 оперативной памяти. Кроме того, оци поступают и на вход счетчика 17, вследствие чего он последовательно мецяет свое состояние, пробегая тем самым всю возможнук, цоследовательцост адресов, поступающих через коих)угепс)р 38 цы ылрссы: входы 34 олокы 32 оцеративой пымят Укызанцые лействия приводят к тому, цто по всем ад 1)есым блока,2 ОсразивОЙ ымят 1 будут записаны ели 1 щы. Формирс)веггсль 4 контрольных чисел обцуляетс я.По окоцчации подготовительного режимы второй коммутатор 30 перев)л 51 г н ццжцсс (на фиг.2) положение. в результате цсго работа генератора 6 блокируется, а вход элемента ИЛИ 26 пос гуцыс логицсс кци цоль, а на вход элемета И 27 - лоицеские елиципы. Коммутатор 38 псревол 5 п ны режим приема адресов из ццсн;це 10 устрс)йства цо дополнительной груп )с 11 входов. Кс)х)хсута. тор 18 переключы)от 112 режим:риемы цмпульсов обращения ьборки ог входы 6). Ны вход блока 19 сравнения О группе 14 входов подают колы ыдрссов; гарнИх;)азрялов, которые определяк)т 51;1)сс молу,)я блокапамяти, для которс)го бу,.сг;Олс)цть:вы)ься контрольное число. Ны цхол б;Окы 29 со)вения по группе 15 вхолов цс)ла 01 кол, озцычаюпЕий количество чиселхрыяц,цхс) в контролируемом модул., ц гоесхо;Ихс) для Опрелелеция кс)цпы раб)с)ты 110) кс)з 00.1 ю выбранного модуля 21151;иРежим контроля. Ь процессе рабс)ты к блоку 1 памяти по ру)ше 12 входов е)остхпают адреса запрашиваемых чисел, а;о холу 6 - сига)ал обра)лсцця. Выбираемые ч:1 сла поступают цы вьхол блока , ымят;. Коды адресов поступают гакже блок управления суммировацис. Импульсы выборки по входу 6 постуакт также блок 2.Если колы старших адресов, .Остуах)- спих по грмпцам 14 и 11 входов, совылают, цто означает оорыИсце к коц; ролируслому модуло памяги, тс б,Ок 9 .рыв 110- ция вырабатывает разрспы юИи й 1 с)тс 1 сиыл, поступаю)ций на 1)-вход тр. геры 20. Импульс разрешения выооркц по вход, 6 ностуцает церез коммутатор 18 Еа вход оловибратора 21, кото)ый формируе; импульс нужной е.телыОс) и л.)я обрыИе;1 я к блоку 32 Опс.ративОЙ 1.2 МИЕИ, 10 сту цые 01 пи Й рез формирователь 25 ы в:ол 35 Колыадресов младших разрядов в это время через коммутатор 38 поступают на вход 34. г 1 о входу 31 установлен режим считывания из блока 32 памяти. В результате этого по здпрашиваемому адресу выбирается информация (единица или ноль). Возможны двд про. должения работы блока 2:1. Если считывается единица - признак первого обращения по данному адресу, она поступает на С-вход триггера 20 и по разрешающему потенциалу на его входе (1 э) переводит его в единичное состояние. На выходе триггера 20 (инверснохг) появится логический ноль, который через элемент И 27 установит режим записи по вхолу 31 и запись логического ноля по входу 33 через элемент И.51 И 26. Олновибратор 24 вы 1 абатывает по перелс у фронту переключения триггера 20 и 1 П 1 ь( 1(О-О;)ь й постпсСт пд счетный Вхо,.г сче 1 "ик-: 28 и ч.рез олновибратор 22 и формирс)ватель 25 на вхол 35 блока 32. Это приводит к повторному обрдщснию по данному адресу, но уже в режиме записи ноля. Че)е:5 оловибратор 23 им, л ь по заднему фронт и пульса с одновиоратора 22 поступит нд вь 1 хол 8 блока 2 и далее н(1 разрепение ком мутдт 01 эд 3. С-и д 1- ный з Олокд , памяти кол постмпит через коммутатор,5 в формирователь 4, гле и сложится с сп) содержимым.2. 1 сли считьНег(я ноль -- п 1)издк повторного обрд;с 1 я по Данному адресу, то триггер 20 е срдбат:Наст, ед.;шица г счетчик 28 пс доба)ляется, считываемое число через коммуатор 3 не поступает в фор;ирователь 4 ки)трольых чисел.Устроиство ПО)ВО,яст таким Оордзом обеспечить однокрап ое суммирование всех чисел даже пи много.ратном и непостоянном по частоте количестве обрагцений к отдельным словам э)ля Определения коца проверки данного мо,гуля необходимо испо,)ьзовать блок 29 сравнения. В результате контроля в счет Ике 28 подсчитывается количество обрацсии, которое сравнивается с числом, постуа)оп(им по группе 15 входов, и в момент сравнения вырабатывается признак сравнения, который по выходу 9 поступает нд вход блока 5 срдвнени 51, и тдм 1)оизвогитси сравнение полученного контрольного чи,а с эталонным, постуаОп(им по группе 13 входов. Приздк сравнения или несравнеиия выраоатывастся на выходе 7 устройтвд.Ф(ээ.,цэа изобретен 1 яУс(э(эйст 5 О л,я Обнар) жения Оп 1)(эок в блокахахя(ирогрдхгм, содер)кащее блок памяти программ, група адресных вхолов кот 01)ОГО ЯВ ЯсСЯ ПВРВОЙ РппЙ ВОДОВ устройства, управляюНий вхол соединен с мпрдВ 51 яОНим вхо;Ом Олокд хпр(Бдения ("ммирОВднием и яг)ляе ся упрдвляю 11 им ВхОдОм устройства, формирователь контрольны.( чи 10 15 20 25 30 35 40 45 50 55 сел, группа информационных выходов которого соединена с первой группой информационных входов блока сравнения, управляющий вход которого соединен с управляк)- ;цим выходом блока управления суммированием, а вторая группа информационных входов и выход блока сравнения являются соответственно второй группой входов устройства и выходом устройства, отляающееся тем, что, с целью повышения точности контроля, оно содержит коммутатор, группа информационных входов которого соединена с группой информационных выходов блока памяти программ, управляюций вход - с дополнительным управляющим выходом блока управления суммированием, а группа информационных выходов коммутатора соединена с группой ин(Ьорма(ионных входов формироВателя контрольных чисел, при этом группа адресных входов блока памяти программ соединена с первой дополнительной гр ппой входов блока управления суммированием, вторая и третья дополнительные группы вхолов которого являются соответственно третьей и четвертой группами входов устройства.2. Устройство по п. 1, отличающееся тем, что блок управления суммированием содержит коммутаторы, элементы И и ИЛИ, )э-триггер, блоки сравнения, одновибраторы, блок оперативной памяти, счетчики, источник напряжения и ге 1 ердтор, вылхо;г которого соединен со вхолом первого чстчикд и псрВым входом первого коммутдторд, второй вход которого является управляющим Входом блока управления суммированим, и вых(эд соединен через первый одновисрдтор с первым входом формирователя обрдщсчИя, выход которого соединен со вхолом разрен)ения вь)борки блока оперативной памяти, д второй вход -- с выходом второго одновибратора и входом третьего одновибратора, причс 1 гыход третьего одновибраторд является дополнитеьным управляюцгим вы.(одом блока управления суммированием и соединен с 1 х-входох 1 э-триггера, Р-вход которого соединен с выходом первого блока сравнения. С)ход - с ипфо 1 эмдционным Вь)ходом блок, оперативной памяти, а инверсный выхл с первыми входами элемента ИЛИ и элементд И, а через четвертый одновибратор - о входом второго олновибратора и входом Второго счетчика, группа информационных выходов которого подключена к первой грхппе входов второго блока сравнения, вторая пэуппа входов которого являетея второй Дополнительной группой входов блока урдвлеиия суммированием, а выход )торого блока сравнения является управляк)щим выходом блока управления суммированием, при этом первый и второй источники напряжения сов линены соответственно с группой первы, и вторых входов второго коммутатора, первый и второй выходы которого соединены О- ответственно с вторыми вхолдми элемента (1/1Р= Сосзаагель Г.Тсхрсд И. ВерссТ с рг нс 543Государственого ко1 елам изобретений иоскаа, Ж - 35, РаунсПатент, г. Ук ород и осла скин Корректор Подписное СССРий, угсна ии гета откры д. 4/5 оектнан, я наб ул. Г и элемента ИЛИ, выходы которых соединены соответственно со входами Запись-считывание и Запись кода числа блока оперативной памяти, группа адресных входов которого соединена с выходом третьего коммутатора, первая группа входов которого соединена с ьыходами третьего коммутатора, первая группа входов которого соединена с группой информационных выходов первого Редактор В. ианко"аказ (84754ВЕР 1 РПРпо113035, МОилсал ПгП счетчика, и вторая группа входов является первой дополните.ьно 4 группой входов блока управления суммированием и соединена с первой группой входов первого блока сравнения, вторая группа входов которого является третьей дополнительной группой входов блока управления суммированием, при этом вход генератора соединен со вторым входом элемента ИЛИ.

СмотретьЗаявка

3474308, 23.07.1982

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ, ЕГОРОВА НИНА ИВАНОВНА

МПК / Метки

МПК: G11C 29/00

Метки: блоках, обнаружения, ошибок, памяти, программ

Опубликовано: 23.12.1986

Код ссылки

<a href="https://patents.su/4-1278982-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-blokakh-pamyati-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в блоках памяти программ</a>

Предыдущий патент: Буферное запоминающее устройство

Следующий патент: Постоянное запоминающее устройство с коррекцией информации

Случайный патент: Устройство для соединения деталей