Устройство для вычисления контрольного элемента и обнаружения ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1325483

Автор: Паронян

Текст

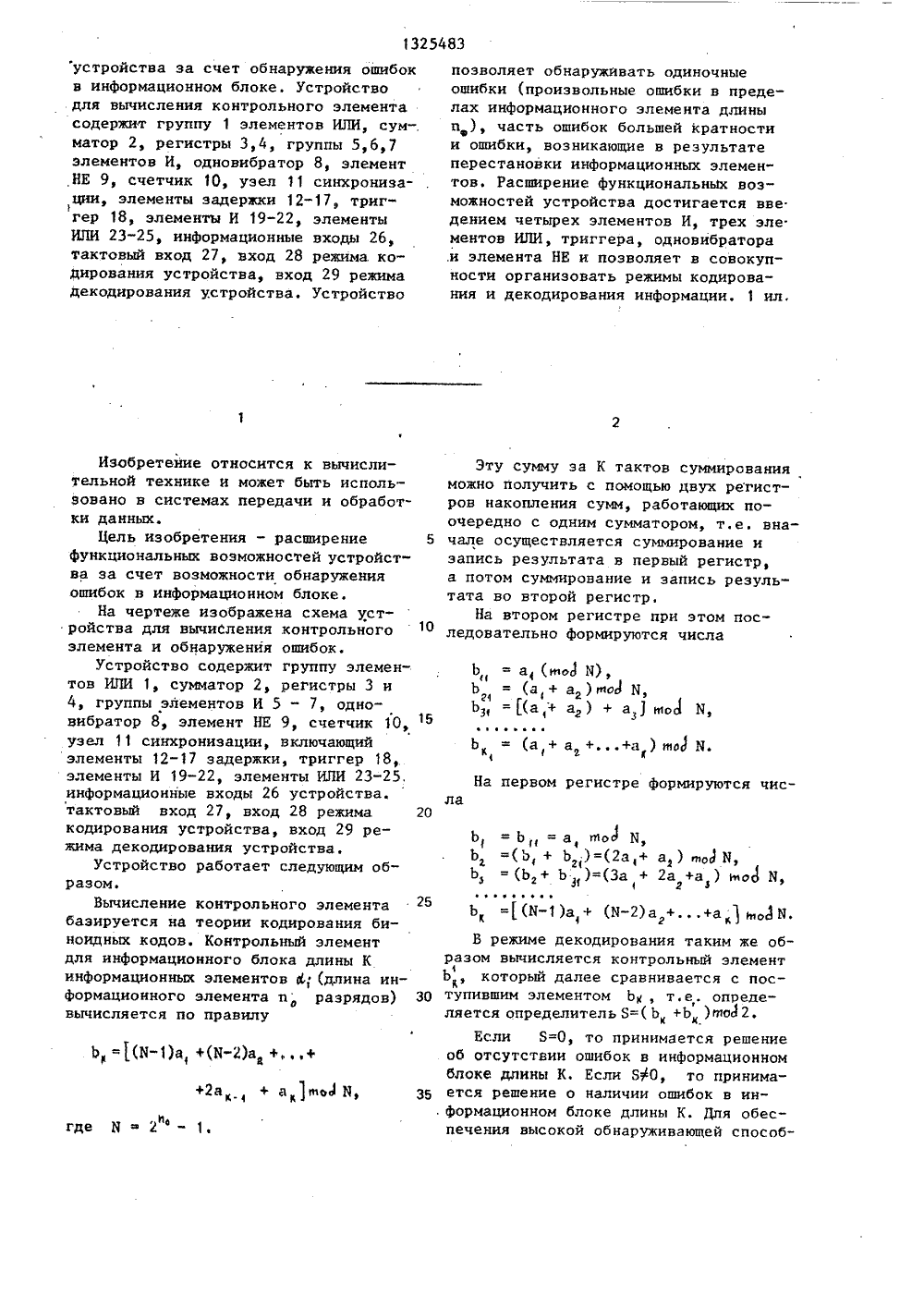

(19) (11) 6 Р 110 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 21) 4045084/2422) 03.03.8646) 23.0,87,75) Л.М. Парон53) 631,3(088.56) Авторское1101826, кл.Авторское св1198524, кл.(54) УСТРОЙСТВО ДЛЯРОЛЬНОГО ЭЛЕМЕНТАБОК ЫЧИСЛЕНИЯ КОНТ БНАРУЖЕНИЯ ОШИ 2 У 27 57) Изобретение ительной техник относится к вычиси может быть исполь передачи и обработзобретения - расшиных воэможностей о СССР 1983 СССР 1984видетельст 06 Р 11/Оидетельство 06 Р 11/О овано в системаи данных. Цельение функционал ОПИСАНИЕ ИЗОБРЕТЕНК А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ+2 а- + ав 1"1 где Я щ 2 ф Не устройства за счет обнаружения ошибокв информационном блоке. Устройстводля вычисления контрольного элементасодержит группу 1 элементов ИЛИ, сумматор 2, регистры 3,4, группы 5,6,7элементов И, одновибратор 8, элементНЕ 9, счетчик 10, узел 11 синхронизации, элементы задержки 12-17, триггер 18, элементы И 19-22, элементыИЛИ 23-25, информационные входы 26,тактовый вход 27, вход 28 режима кодирования устройства, вход 29 режимадекодирования устройства. Устройство Изобретейие относится к вычислительной технике и может быть испольЗовано в системах передачи и обработки данных.Цель изобретения - расширение 5 функциональных воэможностей устройства за счет возможности обнаружения ошибок в информационном блоке.На чертеже изображена схема устройства для вычисления контрольного элемента и обнаружения ошибок.Устройство содержит группу элементов ИЛИ 1, сумматор 2, регистры 3 и 4, группы элементов И 5 - 7, одно- вибратор 8, элемент НЕ 9, счетчик 10, 15 узел 11 синхронизации, включающий элементы 12-17 задержки, триггер 18, элементы И 19-22, элементы ИЛИ 23-25, информационные входы 26 устройства. тактовый вход 27, вход 28 режима 20 кодирования устройства, вход 29 режима декодирования устройства.Устройство работает следующим об" разом.Вычисление контрольного элемента базируется на теории кодирования биноидных кодов. Контрольный элемент для информационного блока длины К информационных элементов К;(длина информационного элемента и разрядов) ЗО вычисляется по правилу Ь =(0-1)а, +(Ю)а, + позволяет обнаруживать одиночныеошибки (произвольные ошибки в пределах информационного элемента длинып ), часть ошибок большей кратностии ошибки, возникающие в результатеперестановки информационных элементов. Расширение функциональных возможностей устройства достигается введением четырех элементов И, трех эле.ментов ИЛИ, триггера, одновибратора.и элемента НЕ и позволяет в совокупности организовать режимы кодирова"ния и декодирования информации. 1 ил,Эту сумму за К тактов суммирования можно получить с помощью двух регистров накопления сумм, работакнцих поочередно с одним сумматором, т.е, вначале осуществляется суммирование и запись результата в первый регистр, а потом суммирование и запись результата во второй регистрНа втором регистре при этом последовательно формируются числа Ъ= а (ии 4 Я),Ь = (а + а ) 4 И,Ь," = (а,+ а) + авой Я,ювЬ = (а + а а ) еос 1 Я. На первом регистре формируются чисЬ =Ь,=а, п 1 о 1 И,Ь =(Ь, + Ь)=(2 а,+ а,) то 3 В,Ь =(Ь + Ъ )=(За + 2 а +а ) иос 1 И,уЪ=(М)а,+ (И)а а ьДБ. В режиме декодирования таким же образом вычисляется контрольный элемент1Ь, который далее сравнивается с поступившим элементом Ь, т.е. определяется определитель Я=( Ь+Ь) юо 3 2.Если Я=О, то принимается решение об отсутствии ошибок в информационном блоке длины К, Если ЯО, то принимается решение о наличии ошибок в ин, формационном блоке длины К. Для обеспечения высокой обнаруживающей способ 1325483ности желательно, чтобы М = (2";.1) было простым числом. и, -Разрядный регистр 3 предназначен для хранения предыдущих сумм информационных элементов в режиме кодирования и декодирования и выполняет вспомогательную роль, п-разрядный регистр 4 - для хранения предыдущих сумм произведения информационных элементов на соответствующие 1 О последовательные целочисленные коэффициенты, для выдачи контрольного элемента Ь в канал через группу 7 элементов И после завершения кодирования, для хранения и выдачи результата сравнения контрольных сумм (определителя Я) в режиме декодирования в элемент ИЛИ 23 с целью анализа определителя 8 и принятия решения о достоверности информационного блока длины К. 20Сумматор 2 состоит из одноразрядных сумматоров на три входа в количестве п, которые по переносу в старший разряд через элемент И на два входа соединены последовательно, 25 а перенос одноразрядного сумматора . позиции по через элемент И на два входа соединен с входом первой позиции одноразрядного сумматора, образуя сумматор на 2 п, входа по вой(2" -1) 30 при нулевом состоянии первого выхода счетчика 10, соединенного с элементом НЕ 9.Если первый выход счетчика 10 находится в состоянии ", то на вторые входы элементов И сумматора 2 с выхода элемента НЕ 9 поступает блокирующий переносы одноразрядных сумматоров сигнал, тем самым превращая сумматор 2 в одноразрядные сумматоры на 40 два входа по 1 иос 2 в количестве и,.Сумматор 2 предназначен для суммирования предыдущей суммы информационных элементов, хранившихся в регистре 3, с очередным информационным эле ментом а; по воо(2- 1) с последукщим суммированием результата этой суммы, переведенной в регистр 3, с предыдущей суммой произведения информационных элементов на последовательные целочисленные коэффициенты, хранившихся в регистре 4 по юос (2"ф -1), а также для поразрядного суммирования (сравнения) вычисленного конт 1рольыого элемента Ь с поступившим контрольным элементомЬ по о 4 2,Узел 11 синхронизации на линиях 12-17 задержки предназначен для фор мирования из тактового сигнала, пос-,тупающего с входа 27 устройства, разрешающих сигналов для элементов И 5н 6 первой и второй групп, сигналасчета для счетчика 10 и управляющихсигналов записи для регистров 3 и 4.По сигналу счета счетчик О считает количество поступивших информационных элементов. Причем счетчик 10имеет два выхода, Первый выход соответствует счету К, который в режимекодирования используется узлом 11 вкачестве завершающего сигнала послевыдачи контрольного элемента, приводящего устройство в исходное состояние. Второй выход счетчика 10 используется только в режиме декодирования.При счете К + 1 по сигналу второговыхода счетчика 10 осуществляетсяанализ определителя 8 и формирование узлом 11 завершающего сигнала,приводящего устройство в исходноесостояние врежиме декодирования.Триггер 18 режима задает режим работы предлагаемого устройства и имеет два выхода (нулевой и единичный)и два входа, соединенные соответственно с входами 28 и 29 устройства,При поступлении сигнала на вход 28триггер устанавливается в нулевоесостояние, т.е, устройство переходитв режим кодирования, а при поступлении сигнала на вход 29 триггер устанавливается в единичное состояние,т,е. устройство переходит в режим обнарушения ошибок (декодирования).В режиме обнаружения ошибок на первые входы элементов И 19 и 21 поступает разрешающий потенциал, а на первый вход элемента И 20 - блокирующийсигнал, В режиме кодирования, наоборот, входы элементов И 19 и 21 блокированы триггером 18, а на первый входэлемента 20 поступает разрешающийсигнал. Одновибратор 8 в режиме коди"рования не действует, он действуеттолько в режиме декодирования и формирует одиночный сигнал только по сигналу первого выхода счетчика 10, соответствующего счету К,Один такт кодирования одного информационного элемента а; делится на два полутакта, За первый полутакт кодирования осуществляется суммирование поступившего информационного элемента с предыдущей суммой информационных элементов по воо (2 ф - 1) изапись результата в регистр 3. Завторой полутакт осуществляется суммирование результатов сумм регистров 3и 4 по мод(2- 1) и запись результата этой суммы в регистр 4. 5Независимо от режима перед началомработы устройство устанавливается висходное состояние - счетчик 10 и регистры 3 и 4 находятся в нулевом состоянии,10Допустим, устройство находится врежиме кодирования, т.е. триггер 18режима находится в нулевом состоянии.В этом режиме первые входы элементовИ 19 и 21 блокированы, а первый входэлемента 20 разблокирован. Информационные элементы поступают поочереднона, информационные входы 2 б.устройства. По поступлении сигнала на тактовый вход 27 устройства сигналы с выходов элементов задержки узла 11 сийхронизации разрешают прохождение информации через элементы И 5 первойгруппы и элементы ИЛИ 1 на входы первого слагаемого сумматора 2 и записывают результат сложения (по сигналувыхода ликии 13 задержки) информациис содержимым первого регистра 3 в регистр 3.Затем по сигналам узла 11 синхро. низации (по сигналам выходов линий14 и 15 задержки) на входы первогослагаемого сумматора 2 поступает через элементы И б второй группы содержимое второго регистра 4 и сумма поИо9во 3 (2 ф " 1) содержимого первого ивторого регистров 3 и 4 записываетсяво второй регистр 4. После этого ксодержимому счетчика 10 добавляетсяединица,По окончании суммирования всех элементов информационного блока длины Кво втором регистре 4 образуется контрольный элемент Ь и сигнал с перМвого выхода счетчика 10, соответствующий счету К, проходя через элементИ 20, пропускает конгрольный элементчерез элементы И 7 третьей группына информационные выходы устройства.Этот же сигнал переполнения, проходячерез элемент ИЛИ 24 и элемент 17 задержки, устанавливает в нулевое состояние счетчик 10, регистр 4 и, проходя через элемент ИЛИ 25, регистр 3,55Устройство готово к вычислению нового контрольного элемента или, еслирежим изменился,к работе в режиме декодирования. Допустим, на вход 29 устройства поступает сигнал, который устанавливает триггер 18 в единичное состояние. Рассмотрим работу устройства в режиме декодирования. В этом режиме входы элементов И 19 и 21 разблокированы, а вход элемента И 20 блокирован, Работа устройства начинается с исходного состояния и продолжается так до суммирования последнего К-го элемента.По окончании суммирования всех К элементов информационного блока на втором регистре 4 образуется сумма Ь и сигнал с первого выхода счетчика 10, соответствующий счету К, проходя через элемент И 19, создает на выходе одновибратора одиночный импульс, который, проходя через элемент ИЛИ 25, устанавливает в нулевое состояние регистр 3. Этот же сигнал с первого выхода счетчика 10, проходя через элемент НЕ 9, блокирует прохождение переноса с младших разрядов в старшие в сумматоре 2, тем самым преобразуя сумматор 2 по що 3 (2 ф - 1) в одноразрядные сумматоры на два входа по шой 2. Устройство в таком состоянии остается до прихода последнего (К+1)-го элемента, т.е. контрольного элемента Ь .По поступлению элемента Ь на вход 26 устройства и сигнала на тактовый вход 27 устройства сигналы с выходов элементов задержки узла 11 синхронизации разрешают прохождение элемента Ь через элементы И 5 первой группы и элементы ИЛИ 1 на входы первого слагаемого сумматора 2 и записывают результат сложения Ь с нулевым содержимым регистра 3 в регистр 3. Затем по сигналам узла 11 синхронизации во втором полутакте на входы первого слагаемого сумматора 2 через элементы И б второй группы поступает содержимое второго регистра 4 и сумма по во 3 2 содержимого первого и второго регистров 3 и 4 записывается во второй регистр 4. После этого к содержимому счетчика 10 добавляется единица и на втором выходе счетчика 10 появляется сигнал, соответствующий счету (К+1).По окончании приема и суммирования всех (К+1) элементов кодового вектора во втором регистре 4 формируется определитель Б, т.е. ( Ь +ф В + Ь ) юод 2, и сигнал с второго вы 1325483,с выходом первого элемента И, выход,элемента НЕ соединен с входом блокировки распространения переносов сум матора вход переноса которого соеУдинен с выходом переноса сумматора,выход второго элемента ИЛИ соединенс входом установки в начальное состо"якие второго регистра, разрядные выходы первого регистра соединены с соответствующими входами третьего элемента ИЛИ, выход которого соединен Фс вторью входом четвертого элемента И. хода счетчика 10, соответствующий счету (К+1), проходя через элемент И 2 1, пропускает результат анализа определителя Я с выхода анализируемого элемента ИЛИ 23 через элемент И 22 на выход ошибки устройства. Этот же сигнал, проходя через элемент ИЛИ 24 и линию 17 задержки, устанавливает в нулевое состояние счетчик 10, регистр 4 и, проходя через элемент ИЛИ 25, регистр 3Устройство готово к декодированию очередного кодового вектора или, при изменении режима, к кодированию.Наличие сигнала на выходе элемента И 22, являющегося решающим выходом устройства, в режиме декодирования означает наличие ошибки в принятом кодовом блоке. Формула изобретения Устройство для вычисления контрольного элемента и обнаружения ошибок, содержащее сумматор, два регистра, три группы элементов И, группу элементов ИЛИ, счетчик и узел синхронизации, причем информационные входы устройства соединеныс первыми входами элементов И первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И второй группы, первые входы которых соединены с первыми входами соответствующих элементов И третьей группы и с соответствующими разрядными выходами первого регистра, информационные входы которого объединены с соответствующими информационными входами второго регистра и подключены к соответствующим разрядным выходам суммы сумматора, входы первого слагаемого которого соединены с разрядными выходами второго регистра, входы второго слагаемого сумматора соединены с выходами соответствующих элементов ИЛИ группы, выходы элементов И третьей группы являются информационными выходами устройства, тактовый вход которого соединен с первым входом узла синхронизации, первый выход которого соединен с вторыми входами элементов И первой группы, второй выход узла синхронизации соединен с входом записи второго регистра, тре. тий выход узла синхронизации соеди-нен с вторыми входами элементов И второй группы, четвертый выход узласинхронизации соединен с входом записи первого регистра, пятый выход узласинхронизации соединен со счетнымвходом счетчика, вход установки в начальное состояние которого соединенс шестым выходом узла синхронизациии с входом установки в начальное сос" тояние первого регистра, о т л и - ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет возможности обнаруженияошибок в информационном блоке в устройство введены триггер, четыре элемента И, три элемента ИЛИ, элементНЕ и одновибратор, причем вход задания режима кодирования устройства соединен с входом установки в "0" триггера, прямой выход которого соединенс первыми входами первого и второгоэлементов И, второй вход первого элемента И соединен с входом элементаНЕ, с первым входом третьего элемента И и с первым разрядным выходомсчетчика, второй разрядный выход которого соединен с вторым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ и с первым входом четвертогоэлемента И, выход которого являетсявыходом ошибки устройства, вход задания режима декодирования устройства соединен с входом установки в триггера, инверсный выход которогосоединен с вторым входом третьегоэлемента И, выход которого соединенс вторыми входами элементов И группы и с вторым входом первого элемента ИЛИ, выход которого соединен свторым входом узла синхронизации, пятый выход которого соединен с первым входом второго элемента ИЛИ, второйвход которого соединен с выходом од.новибратора, вход которого соединен

СмотретьЗаявка

4045084, 03.03.1986

Л. М. Паронян

ПАРОНЯН ЛЕВОН МИКИЧЕВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: вычисления, контрольного, обнаружения, ошибок, элемента

Опубликовано: 23.07.1987

Код ссылки

<a href="https://patents.su/5-1325483-ustrojjstvo-dlya-vychisleniya-kontrolnogo-ehlementa-i-obnaruzheniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления контрольного элемента и обнаружения ошибок</a>

Предыдущий патент: Устройство для обнаружения ошибок в параллельном п разрядном коде

Следующий патент: Устройство для свертки по модулю g=2 -1

Случайный патент: Устройство для подгонки величины сопротивления пленочных резисторов из вентильных металлов