Декодер линейного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

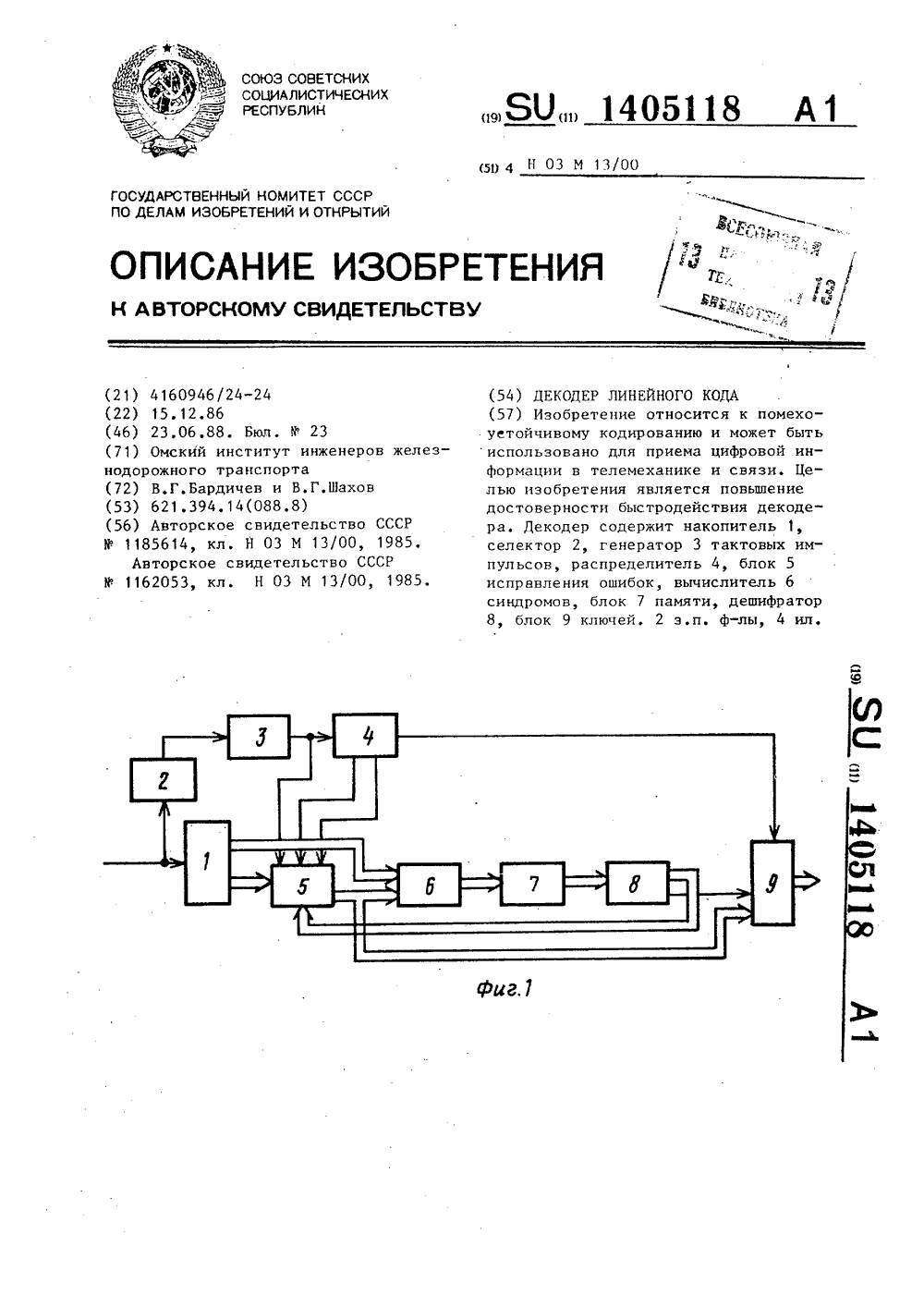

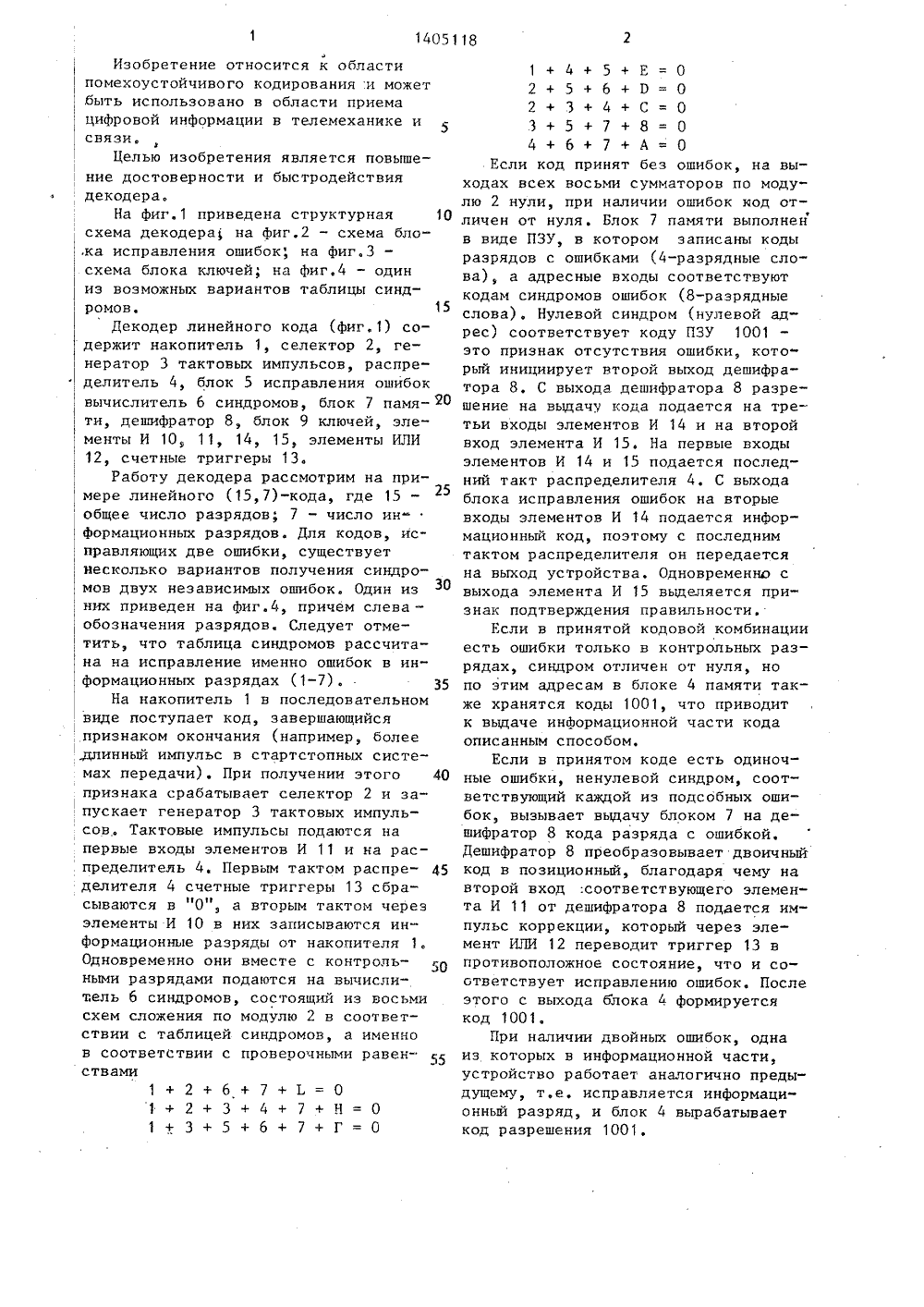

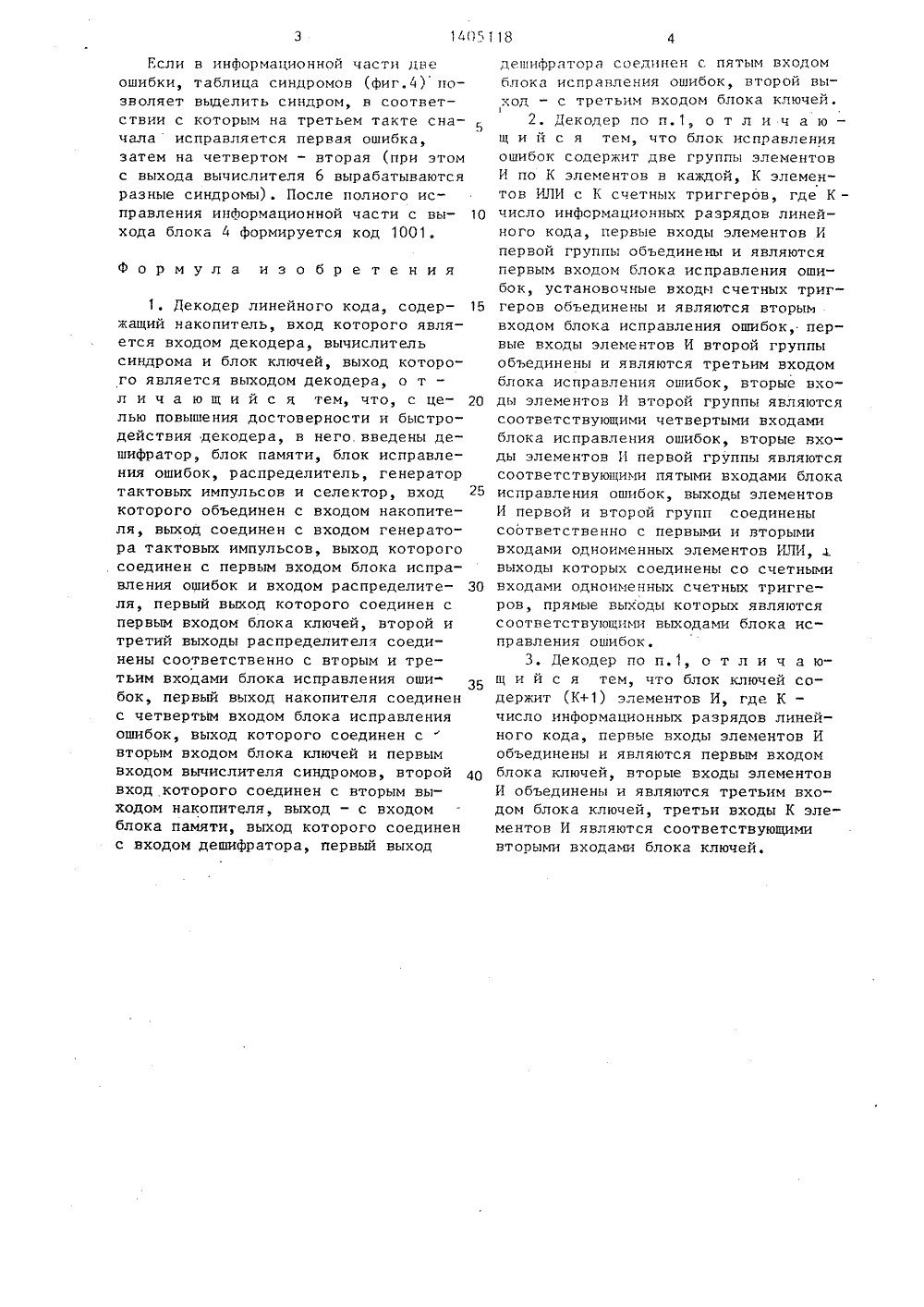

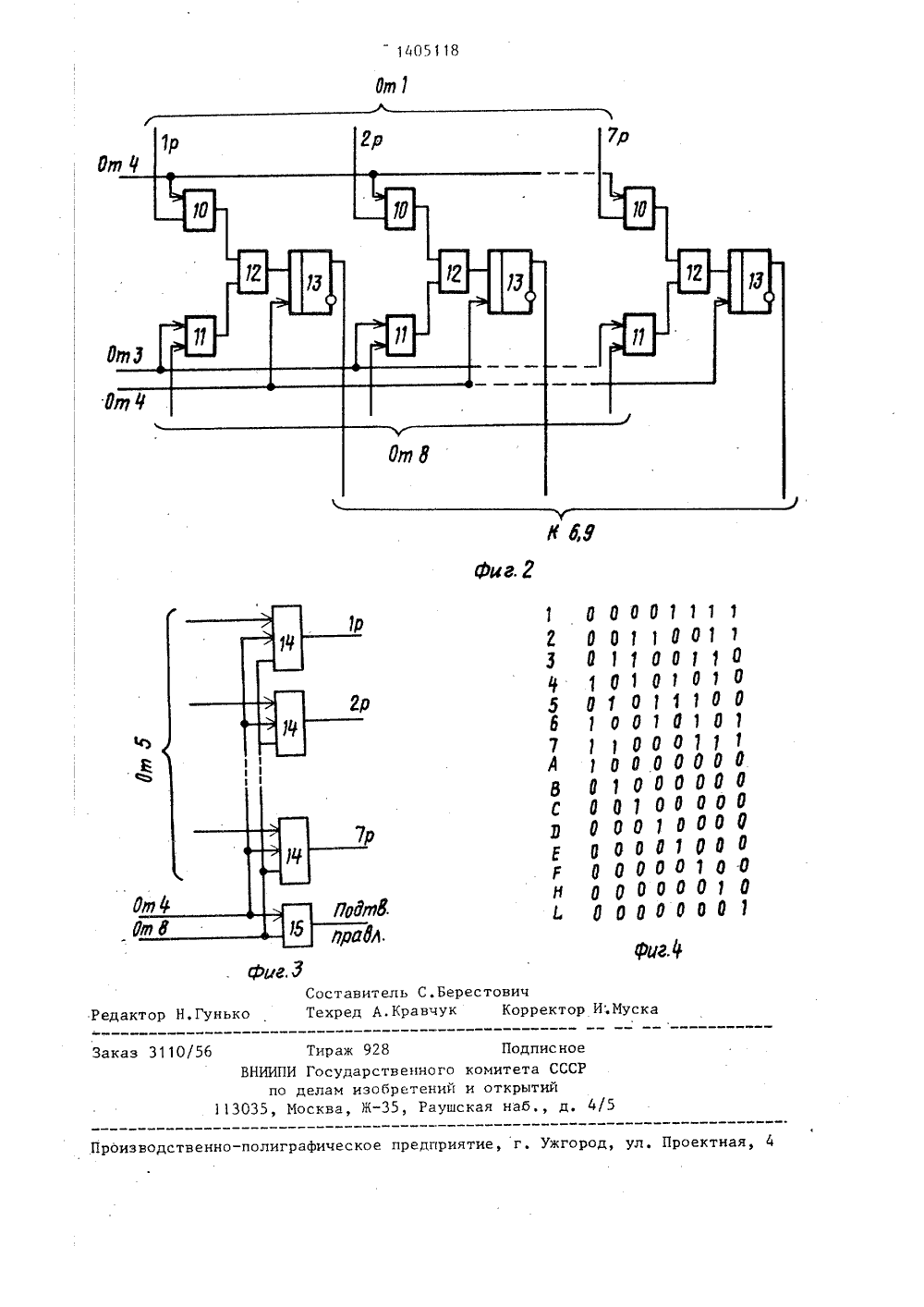

(51) 4 Н 03 М 13/00 СУДАРСТВЕННЫЙ НО ДЕЛАМ ИЗОбРЕТЕНИ ТЕТ СССРИ ОТКРЫТИЙ ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКО СВИДЕТ ТВ(54) ДЕ (57) Из ЕР ЛИНЕЙНОГО ретение относи му кодированию ано для приема в телемеханике ся к помехои может быть цифровой ини связи. ЦеБюл. Ф 23титут инженернспортаев и В.Г.Шахо(088.8) уетойчив использо формации желе повышение твия декодеопитель 1,СС 98 свидетельство Н 03 М 13/00,идетельство СС Н 03 М 13/00,тактовых им 4, блок 5слитель 6дешифраторф-лы, 4 ил,(21) 4160946/24(71) Омский инснодорожного тра(56) АвторскоеВ 1185614, кл.Авторское св11 1162053, кл. лью изобретения является достоверности быстродейс ра. Декодер содержит нак селектор 2, генератор 3 пульсов, распределитель исправления ошибок, вычи синдромов, блок 7 памяти 8, блок 9 ключей, 2 з.п.Изобретение относится к области помехоустойчивого кодирования:и может .быть использовано в области приема цифровой информации в телемеханике и связи,Целью изобретения является повышение достоверности и быстродействия декодера.На фиг,1 приведена структурная 10 , схема декодера на фиг,2 - схема бло- ,ка исправления ошибок, на фиг.3 схема блока ключей, на фиг.4 - один из возможных вариантов таблицы синдромов. 15Декодер линейного кода (фиг. 1) содержит накопитель 1, селектор 2, генератор 3 тактовых импульсов, распределитель 4, блок 5 исправления ошибок вычислитель 6 синдромов, блок 7 памя ти, дешифратор 8, блок 9 ключей, элементы И 10, 11, 14, 15, элементы ИЛИ 12, счетные триггеры 13.Работу декодера рассмотрим на примере линейного (15,7)-кода, где 15 -общее число разрядов, 7 - число информационных разрядов. Для кодов, исправляющих две ошибки, существует несколько вариантов получения синдромов двух независимых ошибок. Один из них приведен на фиг.4, причем слева - обозначения разрядов. Следует отметить, что таблица синдромов рассчитана на исправление именно ошибок в ин, формационных разрядах (1-7). 35На накопитель 1 в последовательном виде поступает код, завершающийся признаком окончания (например, более цлинный импульс в стартстопных системах передачи). При получении этого 40 признака срабатывает селектор 2 и запускает генератор 3 тактовых импульсов. Тактовые импульсы подаются на первые входы элементов И 11 и на распределитель 4. Первым тактом распре делителя 4 счетные триггеры 13 сбрасываются в "0", а вторым тактом через элементы И 10 в них записываются информационные разряды от накопителя 1. Одновременно они вместе с контрольными разрядами подаются на вычислитель 6 синдромов, состоящий из восьми схем сложения по модулю 2 в соответствии с таблицей синдромов, а именно в соответствии с проверочными равенствами1+2+6+7+1 =О1 + 2 + 3 + 4 + 7 + Н = 01+ 3+5+6+ 7+ Г=О 1+ 4+ 5+ Е = 02+5+6+0=02+ 3+ 4+ С = 03+5+ 7+8 = 04+6+ 7+А=ОЕсли код принят без ошибок, на выходах всех восьми сумматоров по модулю 2 нули, при наличии ошибок иод отличен от нуля. Блок 7 памяти выполнен в виде ПЗУ, в котором записаны коды разрядов с ошибками (4-разрядные слова), а адресные входы соответствуют кодам синдромов ошибок (8-разрядные слова). Нулевой синдром (нулевой адрес) соответствует коду ПЗУ 1001 это признак отсутствия ошибки, который инициирует второй выход дешифратора 8, С выхода дешифратора 8 разрешение на выдачу кода подается на третьи входы элементов И 14 и на второй вход элемента И 15. На первые входы элементов И 14 и 15 подается последний такт распределителя 4. С выхода блока исправления ошибок на вторые входы элементов И 14 подается информационный код, поэтому с последним тактом распределителя он передается на выход устройства. Одновременно с выхода элемента И 15 выделяется признак подтверждения правильности,Если в принятой кодовой комбинации есть ошибки только в контрольных разрядах, синдром отличен от нуля, но по этим адресам в блоке 4 памяти также хранятся коды 1001, что приводит к выдаче информационной части кода описанным способом.Если в принятом коде есть одиночные ошибки, ненулевой синдром, соответствующий каждой из подсобных ошибок, вызывает выдачу блоком 7 на дешифратор 8 кода разряда с ошибкой, Дешифратор 8 преобразовывает двоичный код в позиционный, благодаря чему на второй вход :соответствующего элемента И 11 от дешифратора 8 подается импульс коррекции, который через элемент ИЛИ 12 переводит триггер 13 в противоположное состояние, что и соответствует исправлению ошибок. После этого с выхода блока 4 формируется код 1001При наличии двойных ошибок, одна из которых в информационной части, устройство работает аналогично предыдущему, т.е, исправляется информационный разряд, и блок 4 вырабатывает код разрешения 1001.Если в информационной части две ошибки, таблица синдромов (фиг.ч) позволяет выделить синдром, в соответствии с которым на третьем такте сна) чалаисправляется первая ошибка, затем на четвертом - вторая (при этом с выхода вычислителя 6 вырабатываются разные синдромы). После полного исправления информационной части с вы О хода блока ц формируется код 1001.Формула изобретения1. Декодер линейного кода, содер жащий накопитель, вход которого является входом декодера, вычислитель синдрома и блок ключей, выход которого является выходом декодера, о т л и ч а ю щ и й с я тем, что, с це лью повышения достоверности и быстродействия декодера, в него введены дешифратор, блок памяти, блок исправления ошибок, распределитель, генератор тактовых импульсов и селектор, вход 25 которого объединен с входом накопителя, выход соединен с входом генератора тактовых импульсов, выход которого соединен с первым входом блока исправления ошибок и входом распределите ля, первый выход которого соединен с первым входом блока ключей, второй и третий выходы распределителя соединены соответственно с вторым и третьим входами блока исправления оши бок, первый выход накопителя соединен с четвертым входом блока исправления ошибок, выход которого соединен с вторым входом блока ключей и первым входом вычислителя синдромов, второй вход которого соединен с вторым выходом накопителя, выход - с входом блока памяти, выход которого соединен с входом дешифратора, первый выход дешифратора соединен с. пятым входомблока исправления ошибок, второй выход - с третьим входом блока ключей,12. Декодер по п.1, о т л и ч а ю -щ и й с я тем, что блок исправленияошибок содержит две группы элементовИ по К элементов в каждой, К элементов ИЛИ с К счетных триггеров, где К -число информационных разрядов линейного кода, первые входы элементов Ипервой группы объединены и являютсяпервым входом блока исправления ошибок, установочные входы счетных триггеров объединены и являются вторымвходом блока исправления ошибок, первые входы элементов И второй группыобъединены и являются третьим входомблока исправления ошибок, вторые входы элементов И второй группы являютсясоответствующими четвертыми входамиблока исправления ошибок, вторые входы элементов И первой группы являютсясоответствующими пятыми входами блокаисправления ошибок, выходы элементовИ первой и второй групп соединенысоответственно с первыми и вторымивходами одноименных элементов ИЛИ,выходы которых соединены со счетнымивходами одноименных счетных триггеров, прямые выходы которых являютсясоответствуюшими выходами блока исправления ошибок,3. Декодер по п.1, о т л и ч а ющ и й с я тем, что блок ключей содержит (К+1) элементов И, где К -число информационных разрядов линейного кода, первые входы элементов Иобъединены и являются первым входомблока ключей, вторые входы элементовИ объединены и являются третьим входом блока ключей, третьи входы К элементов И являются соответствующимивторыми входами блока ключей,

СмотретьЗаявка

4160946, 15.12.1986

ОМСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

БАРДИЧЕВ ВИКТОР ГРИГОРЬЕВИЧ, ШАХОВ ВЛАДИМИР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: декодер, кода, линейного

Опубликовано: 23.06.1988

Код ссылки

<a href="https://patents.su/4-1405118-dekoder-linejjnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер линейного кода</a>

Предыдущий патент: Устройство цифроаналогового преобразования

Следующий патент: Устройство адаптивной коррекции частотных искажений сигнала м-кратной фазовой модуляции

Случайный патент: Способ получения термостойких полиаминов