Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1297120

Автор: Урбанович

Текст

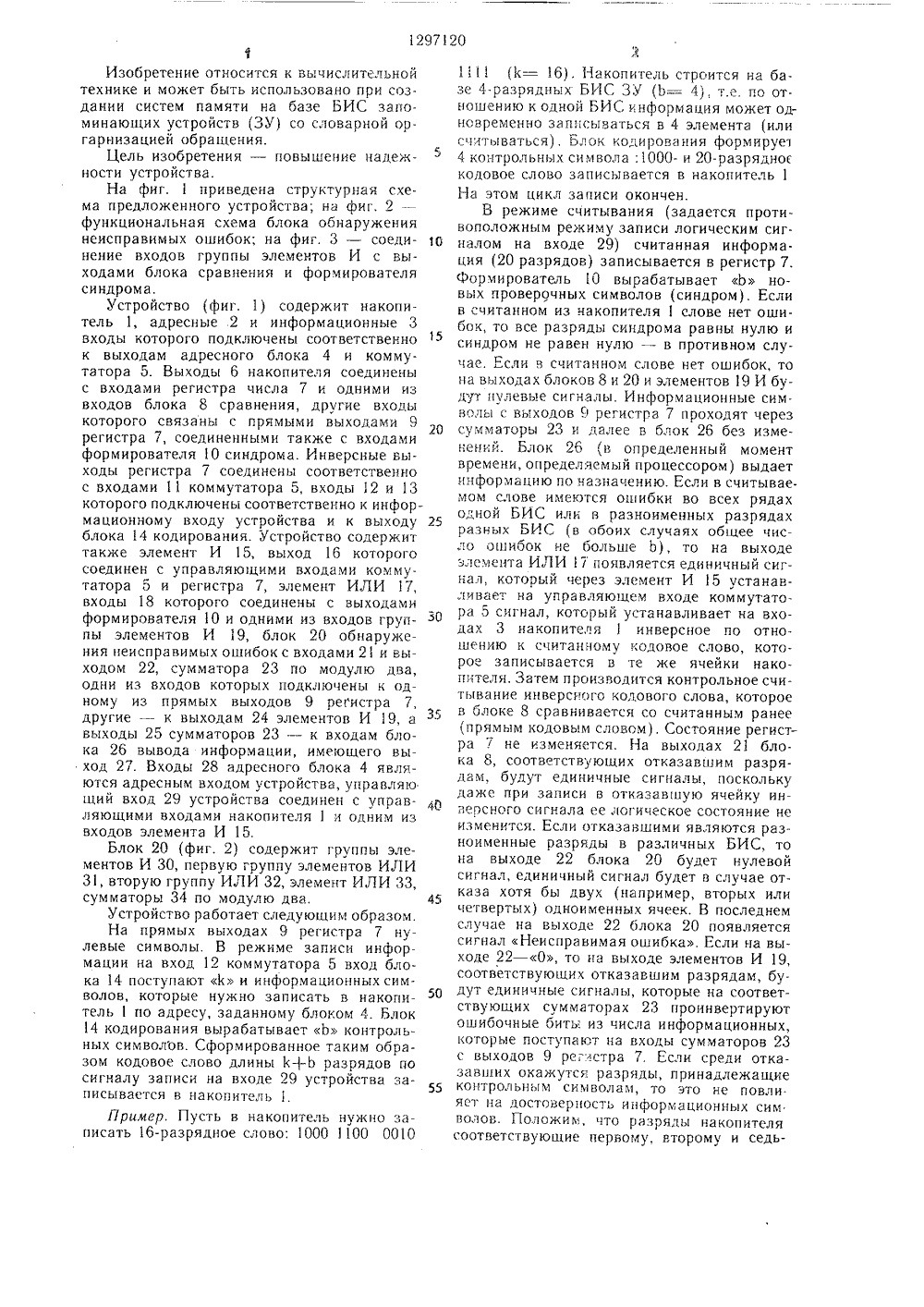

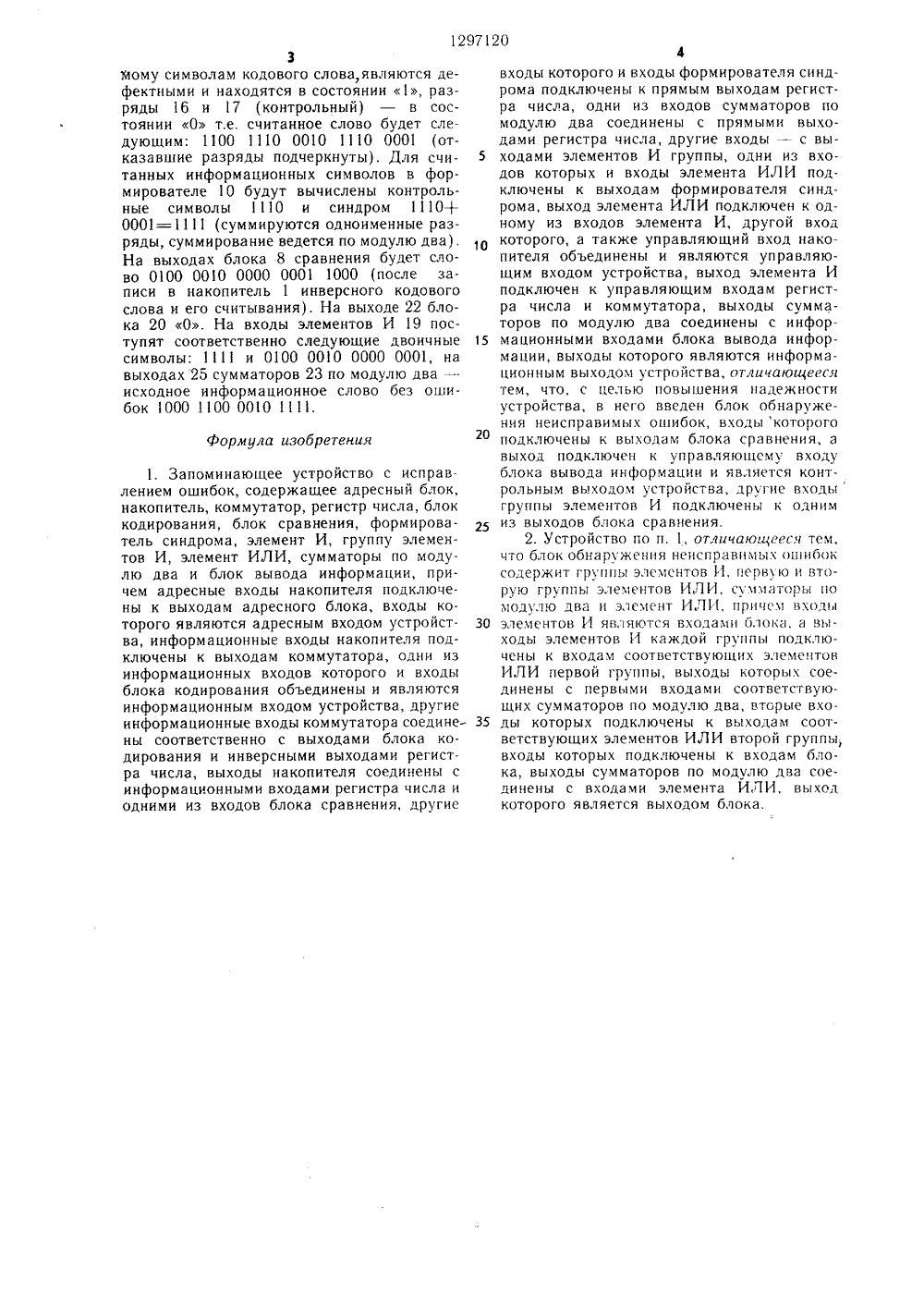

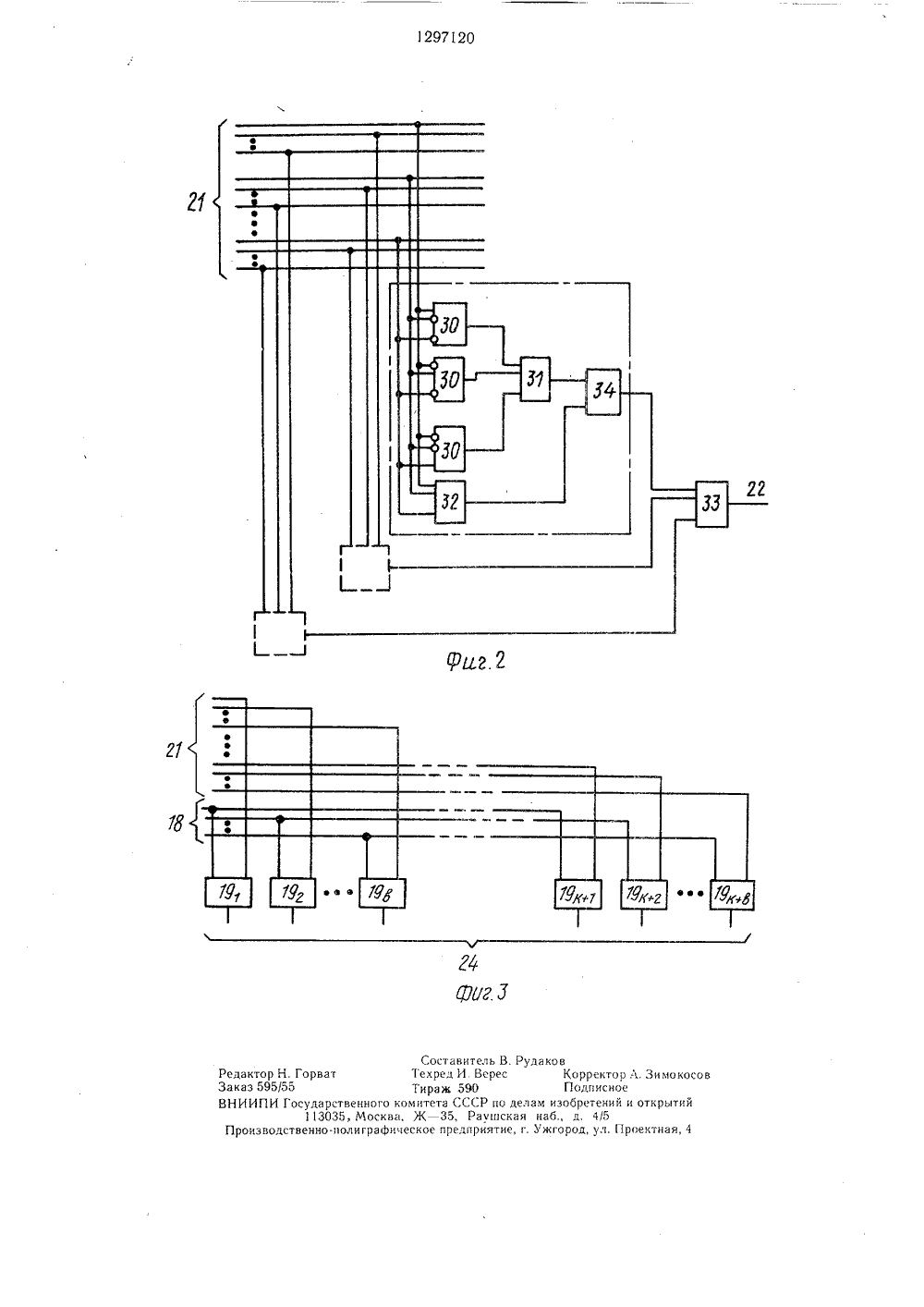

СОЮЗ СОВЕТСНИСОЦИАЛИСТИЧЕСН ЯО 1297120 СПУБЛИН 1 С 29/00 ИСАНИЕ ИЗОБРЕТ А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(57) Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти на базе БИС запоминающих устройств со словарной организацией обращения. Цель изобретения - повышение надежности устройства. Устройство содержит накопитель 1, адресный блок 4, коммутатор 5, регистр 7 числа, блок 8 сравнения, формирователь 10 синдрома, блок 4 коррекции, элемент И 15, элемент ИЛИ 17, группу элементов И 19, блок 20 обнаружения неисправимых ошибок, сумматоры 23 по модулю два, блок 26 вывода информации. Надежность устройства повышается за счет того, что в нем исправляются ошибки в нескольких БИС, входящих в состав накопителя 1, при условии, что ошибки не принадлежат одноименным (по порядку расположения) символам, записанным в различных БИС при хранении одного слова.з.п. ф-лы, 3 ил.1Изобретение относится к вычислительнойтехнике и может быть использовано при создании систем памяти на базе БИС запоминающих устройств (ЗУ) со словарной оргарнизацией обращения.Цель изобретения - повышение надежности устройства.На фиг, 1 приведена структурная схема предложенного устройства; на фиг. 2 -функциональная схема блока обнаружениянеисправимых ошибок; на фиг, 3 - соединение входов группы элементов И с выходами блока сравнения и формирователясиндрома.Устройство (фиг. 1) содержит накопитель 1, адресные 2 и информационные 3входы которого подключены соответственнок выходам адресного блока 4 и коммутатора 5. Выходы 6 накопителя соединеныс входами регистра числа 7 и одними извходов блока 8 сравнения, другие входыкоторого связаны с прямыми выходами 9регистра , соединенными также с входамиформирователя 10 синдрома. Инверсные выходы регистра 7 соединены соответственнос входами 1 коммутатора 5, входы 12 и 13которого подключены соответственно к информационному входу устройства и к выходублока 14 кодирования. Устройство содержиттакже элемент И 15, выход 16 которогосоединен с управляющими входами коммутатора 5 и регистра 7, элемент ИЛИ 17,входы 18 которого соединены с выходамиформирователя 10 и одними из входов группы элементов И 19, блок 20 обнаружения неисправимых ошибок с входами 21 и выходом 22, сумматора 23 по модулю два,Одни из входов которых подключены к Одному из прямых выходов 9 регистра 7,другие - к выходам 24 элементов И 19, авыходы 25 сумматоров 23 - к входам блока 26 вывода информации, имеющего выход 27. Входы 28 адресного блока 4 являются адресным входом устройства, управляющий вход 29 устройства соединен с управляющими входами накопителя 1 и одним извходов элемента И 15,Блок 20 (фиг. 2) содержит группы элементов И 30, первую группу элементов ИЛИ31, вторую группу ИЛИ 32, элемент ИЛИ 33,сумматоры 34 по модулю два.Устройство работает следующим образом.На прямых выходах 9 регистра 7 нулевые символы. В режиме записи информации на вход 12 коммутатора 5 вход блока 14 поступают 1( и информационных символов, которые нужно записать в накопитель 1 по адресу, заданному блоком 4. Блок14 кодирования вырабатывает Ь контрольных символов. Сформированное таким образом кодовое слово длины 1(+Ь разрядов посигналу записи на входе 29 устройства записывается в накопитель 1.Пример. Пусть в накопитель нужно записать 16-разрядное слово: 1000 1100 0010 10 15 20 25 30 ЗГ 4 О 45 50 55 1111 (1(= 16). Накопитель строится на базе 4 разрядных БИС ЗУ (Ь= 4)т.е. по отношению к одной БИС информация может одновременно записываться в 4 элемента (или с итываться) . Блок кодирования формируе 1 4 контрольных символа:1000- и 20-разрядное кодовое слово записывается в накопитель 1 На этом цикл записи окончен.В режиме считывания (задается противоположным режиму записи логическим сигналом на входе 29) считанная информация (20 разрядов) записывается в регистр 7. Формирователь 10 вырабатывает Ь новых проверочных символов (синдром). Если в считанном из накопителя 1 слове нет ошибок, то все разряды синдрома равны нулю и синдром не равен нулю - в противном случае. Если в считанном слове нет ошибок, то на выходах блоков 8 и 20 к элементов 19 И будут нулевые сигналы. Информационные сим. волы с выходов 9 регистра 7 проходят через сумматоры 23 к далее в блок 26 без измененкй. Блок 26 (в определенный момент времени, определяемый процессором) выдает информацию по назначению. Если в считываемом слове имеются ошибки во всех рядах одной БИС или в разноименных разрядах разных БИС (в обоих случаях общее число ошибок не больше Ь), то на выходе элемента ИЛИ 17 появляется единичный сигнал, который через элемент И 15 устанавливает на управляющем входе коммутатора 5 сигнал, который устанавливает на входах 3 накопителя 1 инверсное по отношению к считанному кодовое слово, которое записывается в те же ячейки накопителя. Затем производится контрольное считывание инверсного кодового слова, которое в блоке 8 сравнивается со считанным ранее (прямым кодовым словом). Состояние регистра 7 не кзменяется, На выходах 21 блока 8, соответствующих отказавшим разрядам, будут единичные сигналы, поскольку даже при записи в отказавшую ячейку инверсного сигнала ее логическое состояние не изменится. Если отказавшими являются разноименные разряды в различных БИС, то на выходе 22 блока 20 будет нулевой сигнал, единичный сигнал будет в случае отказа хотя бы двух (например, вторых или четвертых) одноименных ячеек. В последнем случае на выходе 22 блока 20 появляется сигнал Неисправимая ошибка. Если на выходе 22 - О, то на выходе элементов И 19, соответствующих отказавшим разрядам, будут единичные сигналы, которые на соответствующих сумматорах 23 проинвертируют ошибочные биты из числа информационных, которые поступакгг на входы сумматоров 23 с выходов 9 регистра 7. Если среди отказавших окажутся разряды, принадлежащиеконтрольным символам, то это не повли.яет на достоверность информационных сим волов. Положим, что разряды накопителя соответствующие первому, второму и седь 129713Мому символам кодового слова, являются дефектными и находятся в состоянии , разряды 16 и 17 (контрольный) - в состоянии О т.е. считанное слово будет следующим: 1100 1110 0010 1110 0001 (отказавшие разряды подчеркнуты), Для счи таиных информационных символов в формирователе 10 будут вычислены контрольные символы 1110 и синдром 1 10+ 0001=1111 (суммируются одноименные разряды, суммирование ведется по модулю два), На выходах блока 8 сравнения будет слово 0100 0010 0000 0001 1000 (после записи в накопитель 1 инверсного кодового слова и его считывания). На выходе 22 блока 20 О. На входы элементов И 19 поступят соответственно следующие двоичные 15 символы: 111 и 0100 0010 0000 0001, на выходах 25 сумматоров 23 по модулю два - исходное информационное слово без ошибок 000 1100 0010 111.20Формула изобретения1. Запоминающее устройство с исправлением ошибок, содержащее адресный блок, накопитель, коммутатор, регистр числа, блок кодирования, блок сравнения, формирователь синдрома, элемент И, группу элементов И, элемент ИЛИ, сумматоры по модулю два и блок вывода информации, причем адресные входы накопителя подключены к выходам адресного блока, входы которого являются адресным входом устройст- ЗО ва, информационные входы накопителя подключены к выходам коммутатора, одни из информационных входов которого и входы блока кодирования объединены и являются информационным входом устройства, другие информационные входы коммутатора соедине ны соответственно с выходами блока кодирования и инверсными выходами регистра числа, выходы накопителя соединены с информационными входами регистра числа и одними из входов блока сравнения, другие 204входы которого и входы формирователя синдрома подключены к прямым выходам регистра числа, одни из входов сумматоров по модулю два соединены с прямыми выходами регистра числа, другие входы - с выходами элементов И группы, одни из входов которых и входы элемента ИЛИ подключены к выходам формирователя синдрома, выход элемента ИЛИ подключен к одному из входов элемента И, другой вход которого, а также управляющий вход накопителя объединены и являются управляющим входом устройства, выход элемента И подключен к управляющим входам регистра числа и коммутатора, выходы сумматоров по модулю два соединены с информационными входами блока вывода информации, выходы которого являются информационным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введен блок обнаружения неисправимых ошибок, входы которого подключены к выходам блока сравнения, а выход подключен к управляющему входу блока вывода информации и является контрольным выходом устройства, другие входы группы элементов И подключены к одним из выходов блока сравнения.2. Устройство по и. 1, отлицающеег тем, что блок обнаружения неисправимых ошибок содержит группы элементов И, первую и вторую группы элементов ИЛИ, сумматоры по модулю два н элемент ИЛИ, причех входы элементов И являются входами блока, а выходы элементов И каждой группы подключены к входам соответствующих элементов ИЛИ первой группы, выходы которых соединены с первыми входами соответствующих сумматоров по модулю два, вторые входы которых подключены к выходам соответствующих элементов ИЛИ второй группы, входы которых подключены к входам блока, выходы сумматоров по модулю два соединены с входами элемента ИЛИ, выход которого является выходом блока.Редактор Н. ГорватЗаказ 595/55ВНИИПИ Государственного113035, МоскПроизводственно-полиграф Составитель В. РудаковТехред И Верес Корректор Л. Зи мокосоТираж 590 Подписноекомитета СССР по делам изобретений и открытийа, Ж, Раушская наб., д. 4/5веское предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

3965179, 14.10.1985

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

УРБАНОВИЧ ПАВЕЛ ПАВЛОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.03.1987

Код ссылки

<a href="https://patents.su/4-1297120-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Запоминающее устройство с самоконтролем

Следующий патент: Передаточное устройство

Случайный патент: Устройство для защиты всаса землесоса от растительных включений