Устройство для декодирования с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1411981

Автор: Карпухин

Текст

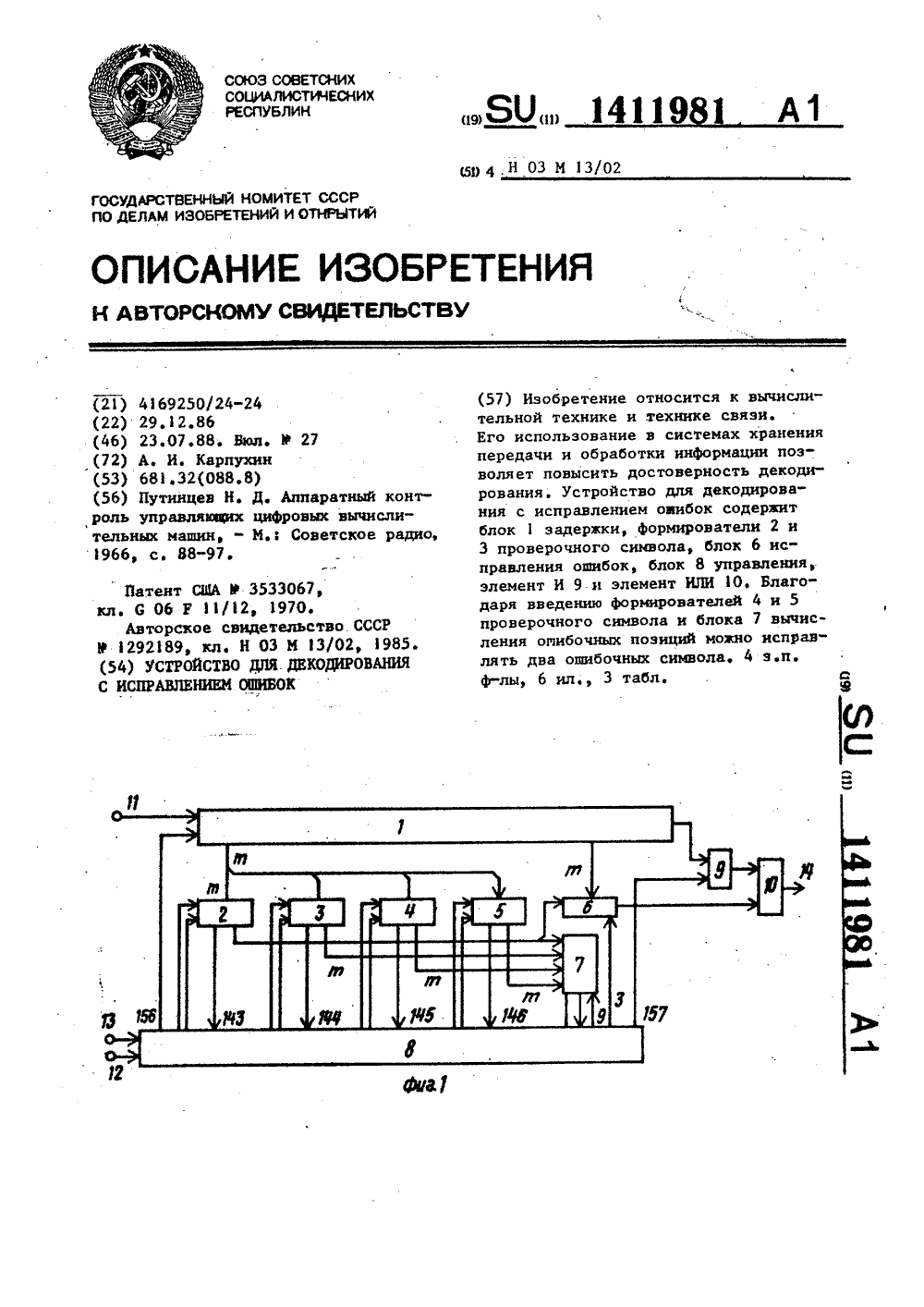

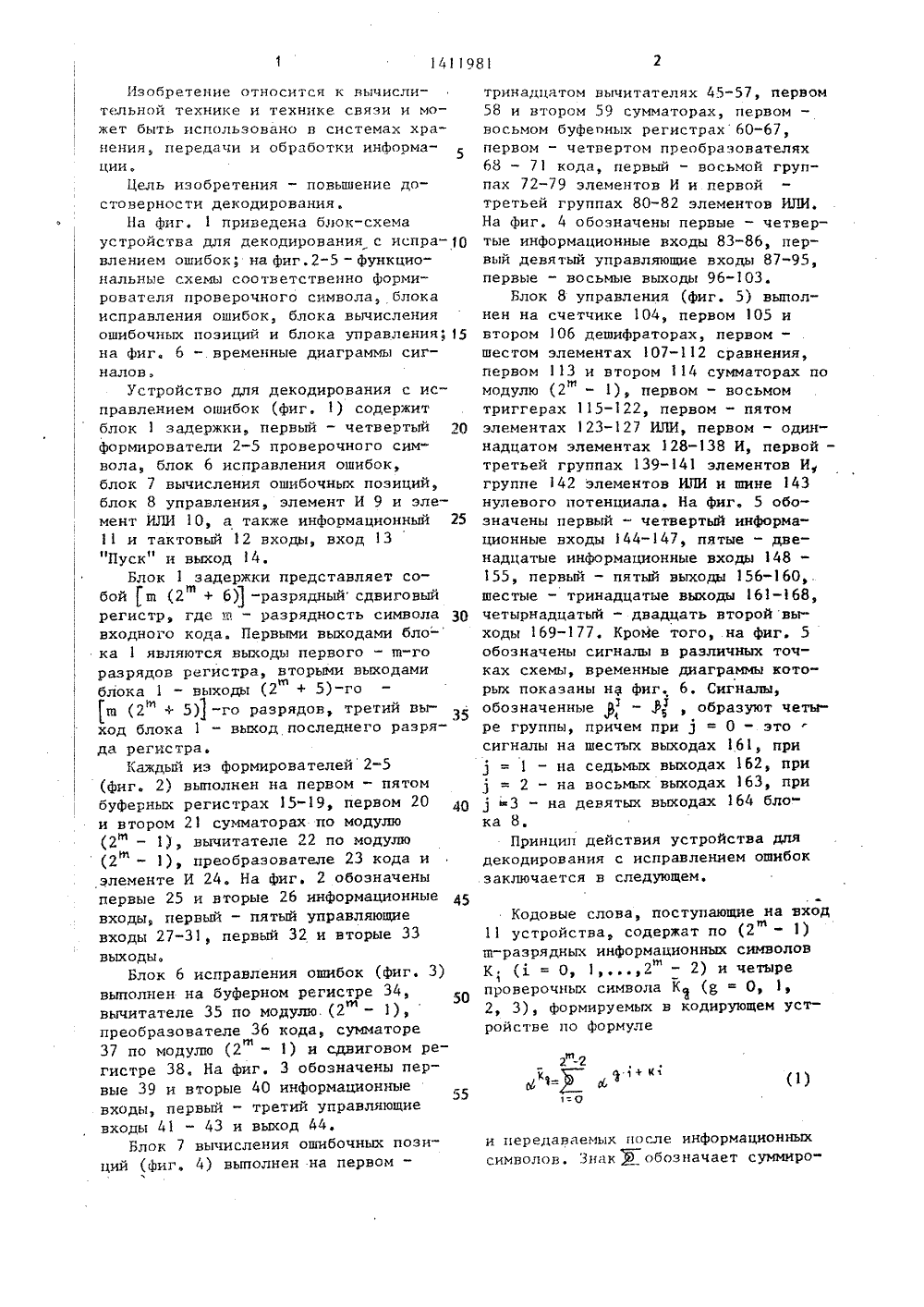

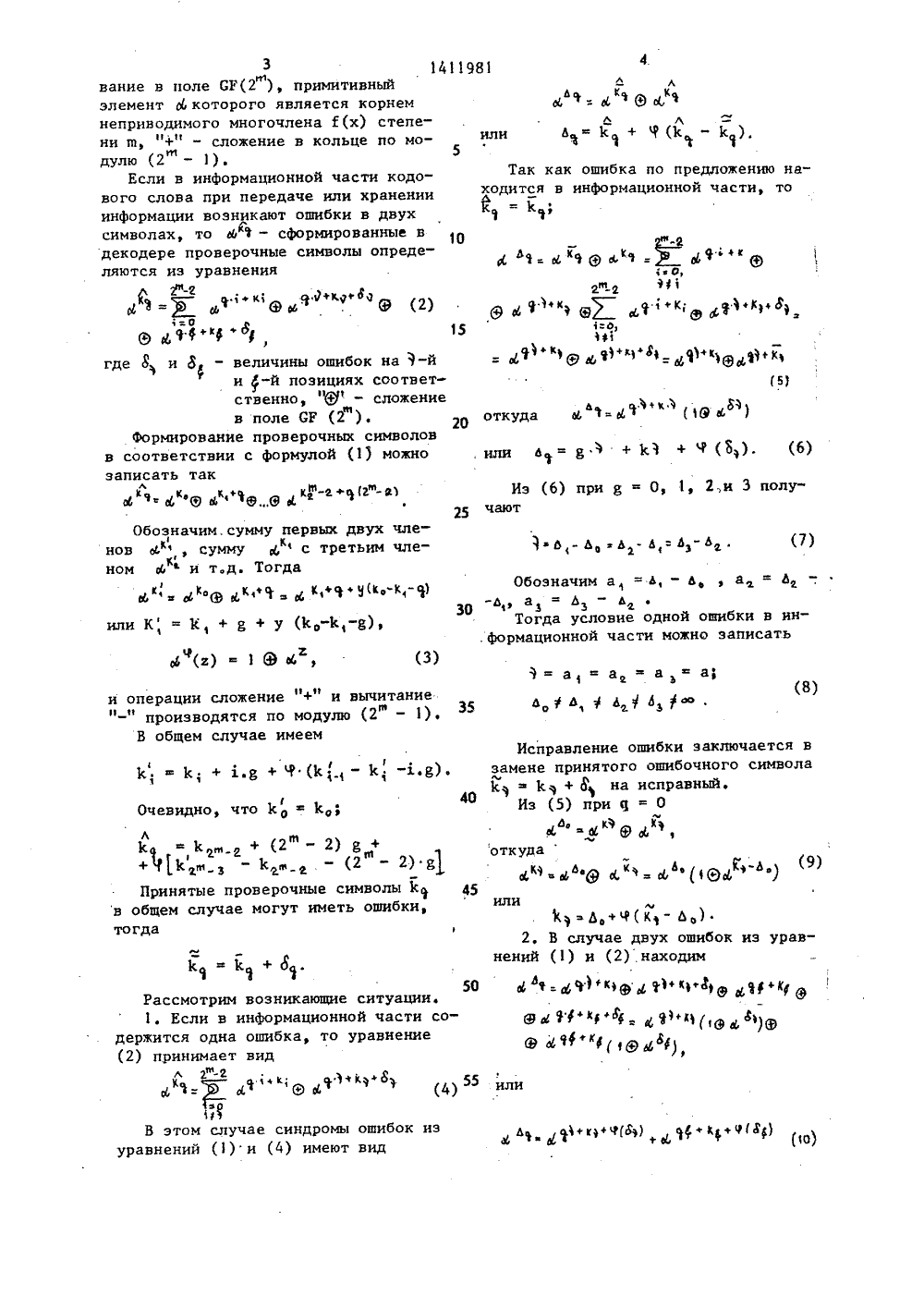

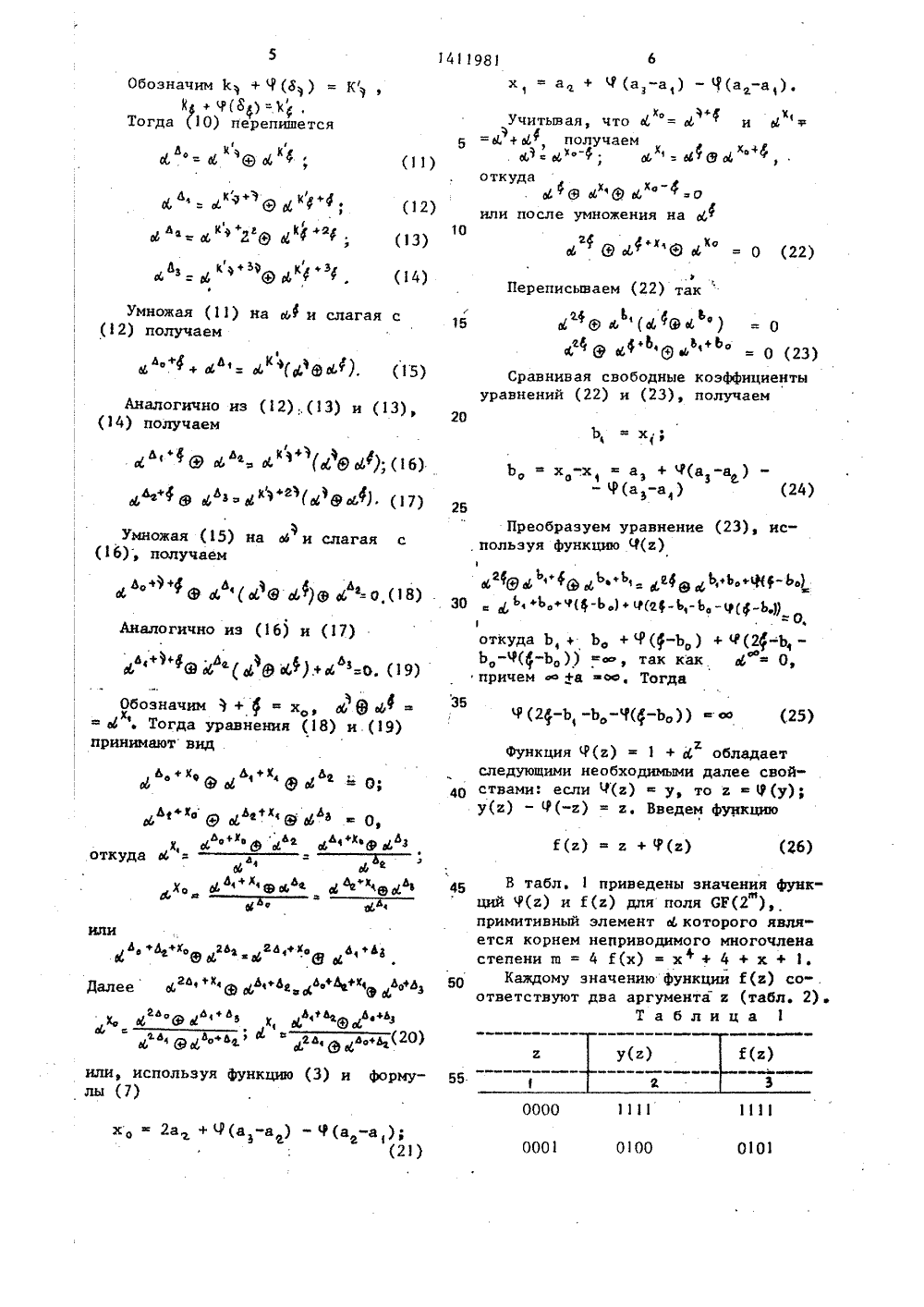

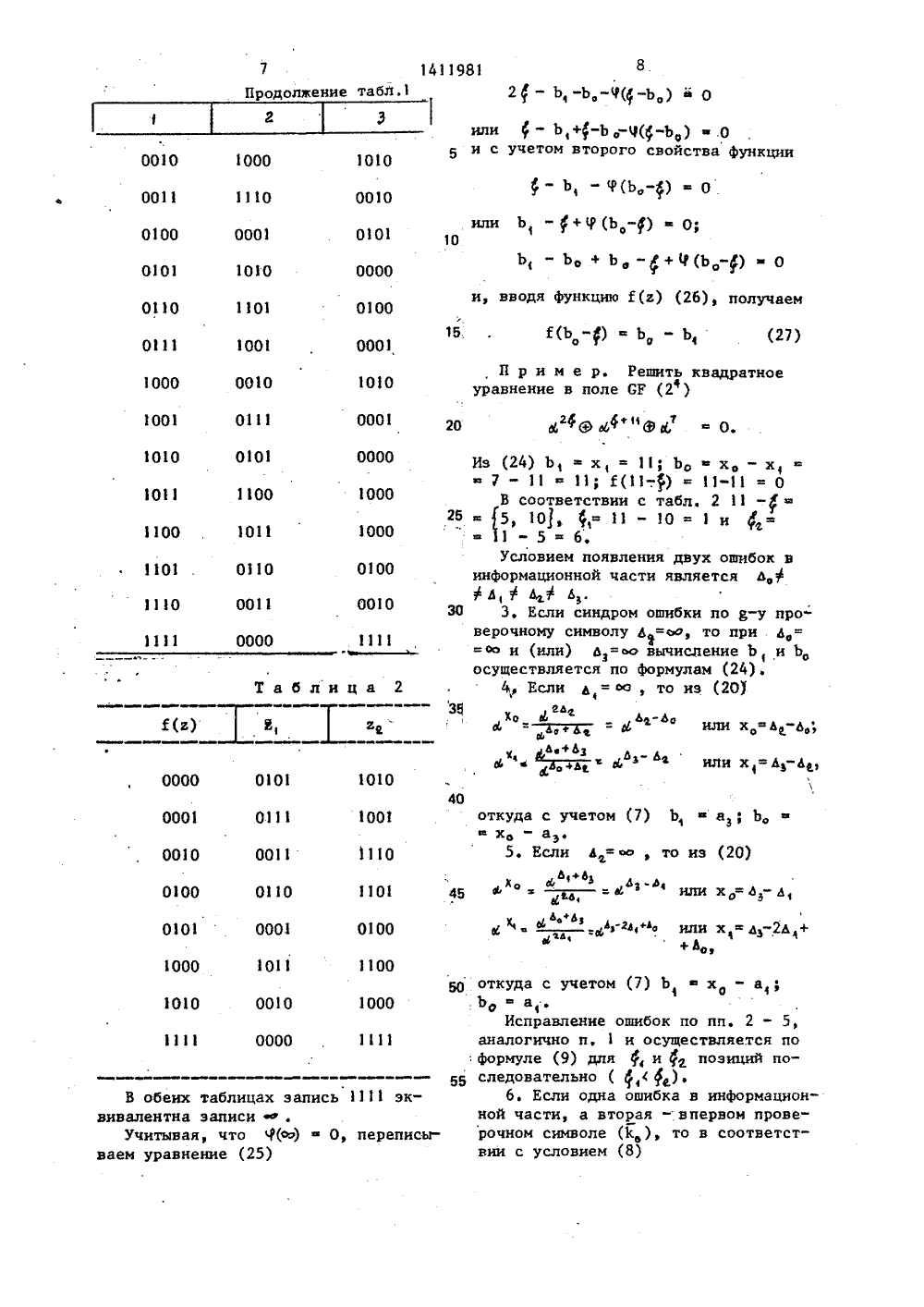

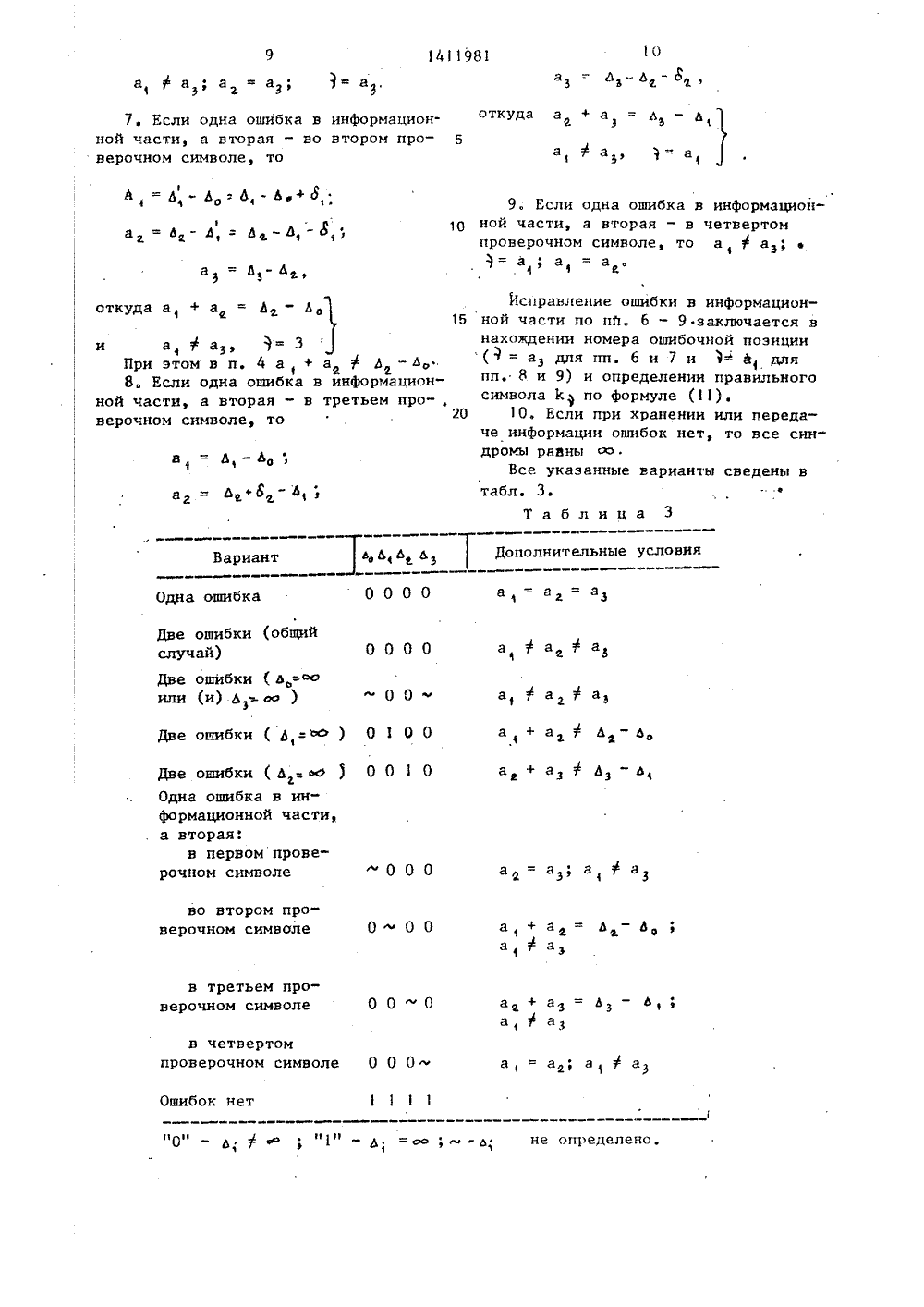

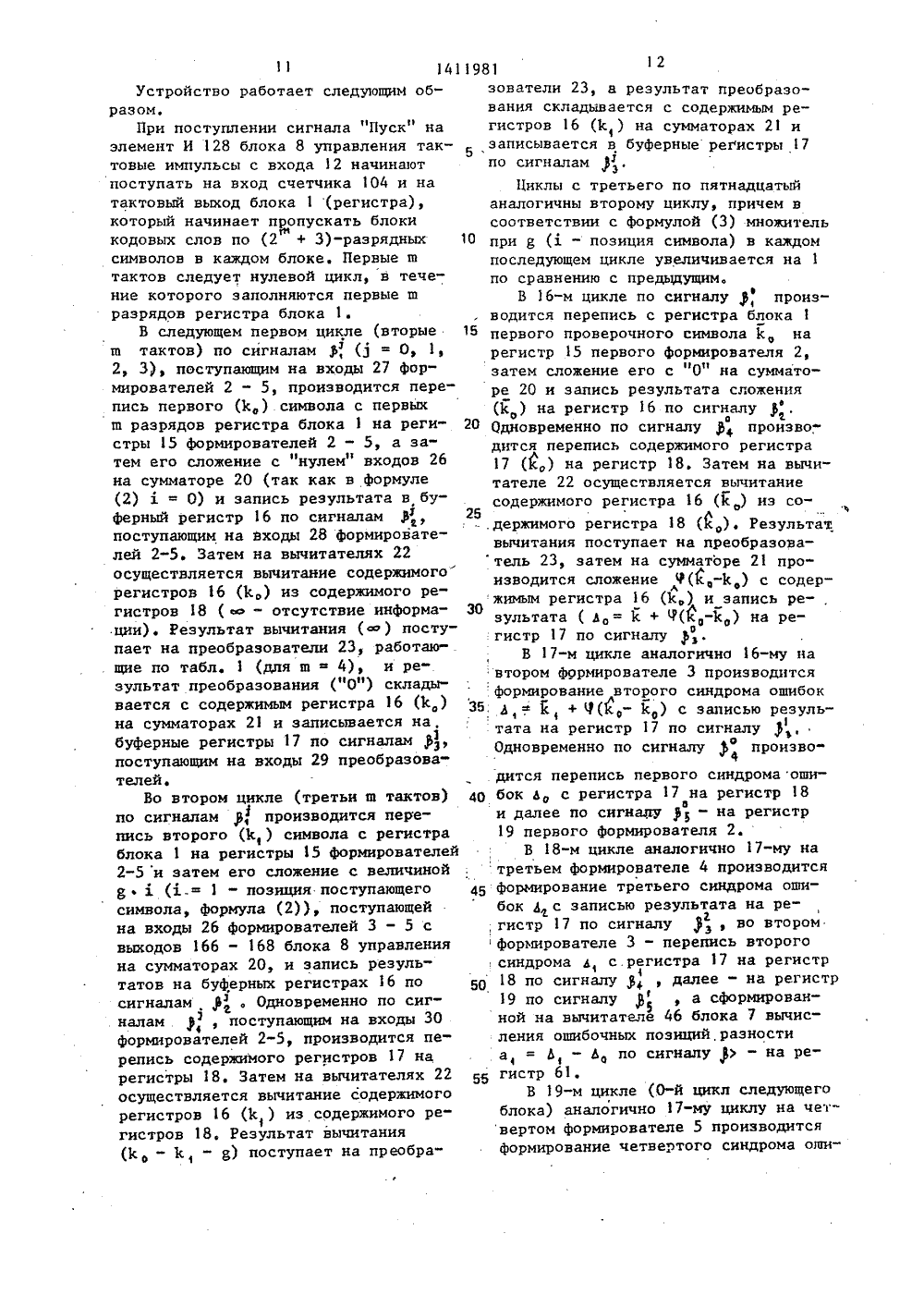

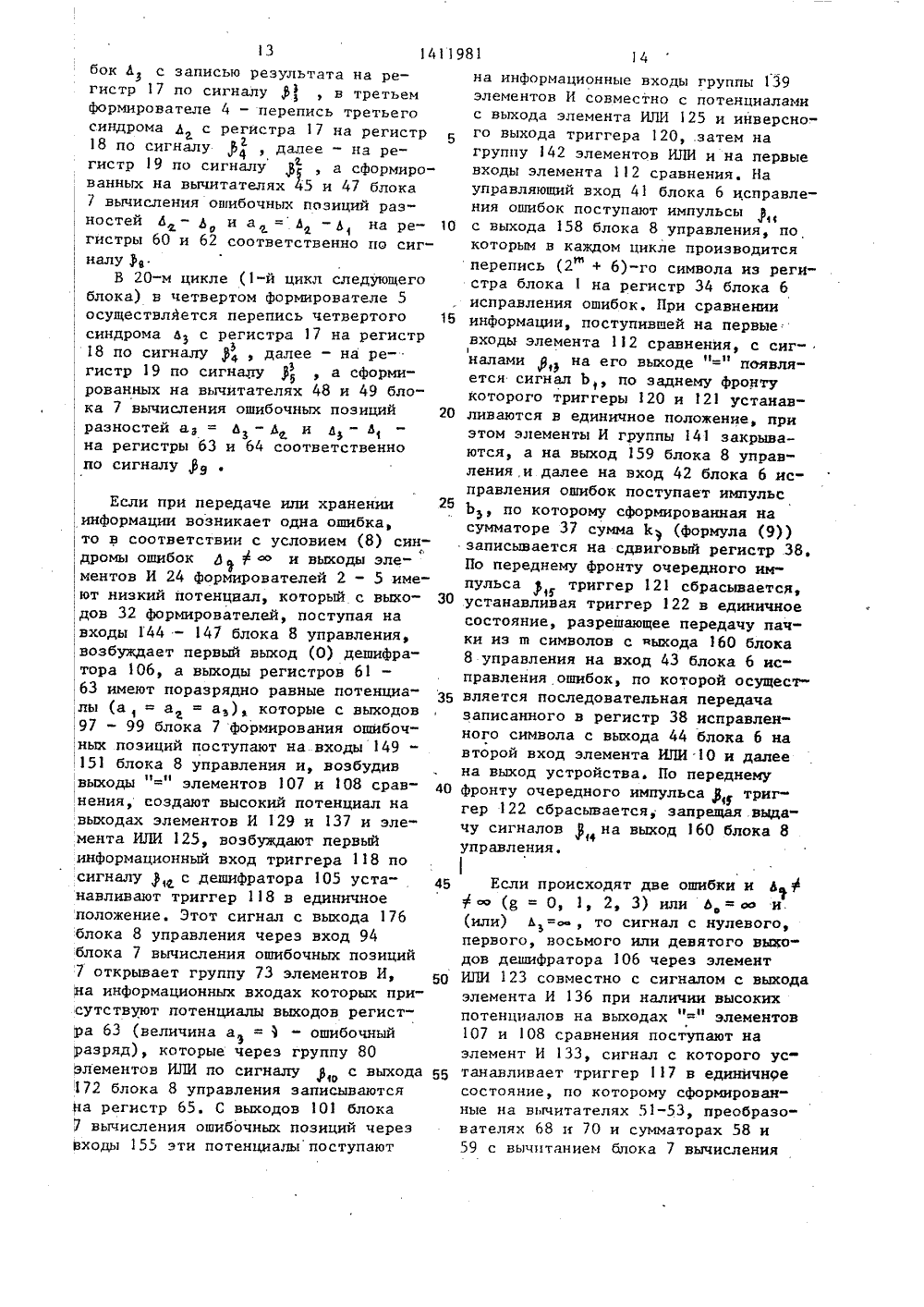

(19) 01) 4, и 03 М 13/02 ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОП ОБРЕТЕН И ОМУ СВИДДТЕЛЬСТ АВТ нтради В 3533067,(56) Путинцев Н. Д. Аппаратныйроль управляющих цифровых вычительных машин, - М.) Советско1966, с. Я 8-97.(57) Изобретение относится к вычислительной технике и технике связи.Его использование в системах храненияпередачи и обработки информации позволяет повысить достоверность декодирования. Устройство для декодирования с исправлением ошибок содерзитблок 1 задеркки, формирователи 2 и3 проверочного символа, блок 6 ис"правления ошибок, блок 8 управления,элемент И 9 и элемент ИЛИ 10. Благодаря введению формирователей 4 и 5проверочного символа и блока 7 вычисления ошибочных позиций мозно исправлять два ошибочных символа, 4 э.п,ф-лы, б ил., 3 табл.или двух ошибочных символов и их исправление.Устройство для декодирования с ис правлением ошибок описано для полного кода, содержащего (2 - 1) информаци,онных ш-рязрядных символа и четыре проверочных, но оно работает н с любым укорочением кода при соответствующем изменении счетчика и дешифратора 10 счетчика.,формула изобретения 1. Устройство для декодирования 15 с исправлением ошибок, содержащее блок задержки первые выходы котороУго подключены к соответствующим первым информационным входам первого и второго формирователей проверочного 20 ,символа, первые выходы которых соединены соответственно с первым и вторым информационными входами блока управления, вторые выходы блока за,держки подключены к соответствующим 25 первым информационным входам блока ,исправления ошибок, третий вьгход блока задержки соединен с первым входом .элемента И, выход которого подключен к первому входу элемента ИЛИ, выход . 30 ,которого является выходом устройства, первый и второй выходы блока управления подключены соответственно к ,тактовому входу блока задержки и второму входу элемента И, третий - пятый выходы блока. управления соедииены соответственно с первым - тре,тьим управляющими входами блока исправления ошибок, шестые и седьмые выходы блока управления подключены 40 к управляющим входам соответственно первого и второго формирователей проверочного символа, информационный вход блока задержки и тактовый вход блока управления являются одноимен ными входами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности декодирования, в устройство введены блок вычисления ошибочных позиций, третий 50 и четвертый формирователи проверочного символа, первые информационные входы которых подключены к соответствующим первым выходам блока задержки, первые выходы третьего и четвертого формирователей проверочного символа соединены соответственно с третьим и четвертым информационными входами блока управления, вторые выходы первого формирователя проверочного символа подключены к соответствующим первым информационным входам блока вычисления ошибочных позиций и вторым информационным входам блока исправления ошибок, выход которого соединен с вторым входом элемента ИЛИ. вторые выходы второго - четвертого формирователей проверочного символа соединены соответственно с вторыми - четвертыми информационными входами блока вычисления ошибочных позиций, первые - восьмые выходы которого соединены соответственно с пятым - двенадцатыми информационными входами блока управления, восьмые и девятые выходы которого подключены к управляющим входам соответственно третьего и четвертого формирователей проверочного символа, десятые - тринадцатые выходы блока управления соединены с вторыми информационными входами соответственно первого - четвертого формирователей проверочного символа, четырнадцатый - двадцать второй выходы блока управления соединены соответственно с первым - девятым управляющими входами блока вычисления ошибочных позиций, вход "Пуск" блока управления является одноименным входом устройства.2,.Устройство по п. 1, о т л и - ч а ю щ е е с я ,тем, что формирователь проверочного символа выполнен на буферных регистрах, сумматорах по модулю (2 - 1), (ш - разрядность информационного символа входного кода), вычитателя по модулю (2 - 1), преобразователя кода и элемента И, выход которого является первым выходом формирователя, информационные входы первого буферного регистра являются первыми информационными входами формирователя, выходы первого буферного регистра соединены с первыми входами первого сумматора по модулю (2 - 1), вторые входы которого являются вторыми информационными входами формирователя выходы первоф е го сумматора по модулю (2 . - 1) соединены с информационными входами второго буферного регистра, выходы которого подключены к первым входам второго сумматора по модулю (2 - 1) и вычитающим входам вычитателя по модулю (2 - 1), выходы которого через преобразователь кода подключены к вторым входам второго сумматора11981 20 5 10 15 20 25 130 19 14по модулю (2 - 1), выходы которогосоединены с информационными входамитретьего буферного регистра, выходыкоторого соединены с информационнымивходами четвертого буферного регистра, выходы которого подключены к суммирующим входам вычитателя.по модулю(2 - 1) и информационным входам пятого буферного регистра, выходы которого соединены с соответствующими:входами элемента И и являются вторыми выходами формирователя, управляющие входы первого - пятого буферныхрегистров являются соответственнопервым - пятым управляющими входамиформирователя,3. Устройство по п. 1, о т л и -ч а ю щ е е с я тем, что блок исправления ошибок выполнен на сдвиговом регистре, сумматоре по модулю(2 - 1), вычитателе по модулю (Р -1)преобразователе кода и буферномрегистре, информационные входы кото-рого являются первыми информационными входами блока,. выходы буферногорегистра соединены с вычитающими ввходами вычитателя по модулю (2 - 1)суммирующие входы которого объединены с соответствующими первыми входами сумматора по модулю (2 - 1) иявляются вторыми информационнымивходами блока, выходы вычитателя помодулю (2 - 1) через преобразователькода подключены к вторым входам сумматора по модулю (2 - 1), выходыкоторого соединены с информационнымивходами сдвигового регистра, выходкоторого является выходом блока, управляющие входы буферного и сдвигового регистров и тактовыйвход сдвигового регистра являются соответственно первым - третьим управляющимивходами блока,4. Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок вычисления ошибочных позиций выполнен на первом - тринадцатом вычитателях, первом и втором сумматорах, первом - восьмом буферных регистрах, первом - четвертом преобразователях кода, первой - восьмой группах элементов И и первой - третьей группах элементов ИЛИ, вычитающие входы первого и второго вычитателей соответственно объединены и являются первыми информационными входами блока, суммирующие входы второго и вычитающие входы третьего и пятого вычитателей соответственно объединены и являются вторыми информационными входами блока,суммирующие входы первого и третьегои вычитающие входы четвертого вычитателей соответственно объединены иявляются третьими информационнымивходами блока, суммирующие входы четвертого и пятого вычитателей соответственно объединены и являются четвертыми информационными входами блока, выходы первого - пятого вычитателей соединены с информационнымивходами одноименных буферных регистров, выходы первого буферного регистра соединены с суммирующими входами шестого вычитателя и являютсяпервыми выходами блока, выходы второго буферного регистра подключенык вычитающим входам седьмого, вось"мого и десятого вычитателей, информационным входам первой и восьмой .групп элементов И и являются вторымивыходами блока, выходы третьего буферного регистра подключены к суммирующим входам восьмого и вычитающимвходам. девятого вычитателей, первымсуммирующим входам первого и второгосумматоров и являются третьими выходами блока, выходы четвертого буферного регистра подключены к вычита" .ющим входам шестого и суммирующим входам седьмого и девятого вычитателей, информационным входам второй итретьей групп элементов И и являютсячетвертыми выходами блока, выходы:пятого буферного регистра соединеныс суммирующими входами десятого вы читателя и являются пятыми выходамиблока, выходы шестого и десятоговычитателей соединены с информационными входами соответственно шестойи пятой групп элементов И, выходы 45 седьмого вычитателя через первыйпреобразователь кода подключены квторым суммирующим входам первогои второго сумматоров, выходы восьмого и девятого вычитателей через соответственно второй и третий преобразователи кода соединены с вычитающими входами соответственно первого и второго сумматора, выходы которыхсоединены с информационными входамисоответственно четвертой и седьмойгрупп элементов И, выходы йервой и второй групп элементов И подключенысоответственно к первым и вторым входам первой группы элементов ИЛИ, 21141выходы которой соединены с информа, ционными входами шестого буферногорегистра, выходы третьей - пятойгрупп элементов И подключены соответ 5ственно к первым - третьим входамвторой группы элементов ИЛИ, выходыкоторой соединены с вычитаюшими вхо дами одиннадцатого вычитателя, выходы которого соединены с входами чет рвертого преобразователя кода, первыеи вторые выходы которого подключенык вычитающим входам соответственнодвенадцатого.и тринадцатого вычита телей, выходы которых соединены с 15информационными входами соответственно седьмого и восьмого буферных,регистров, выходы шестой - восьмойгрупп элементов И соединены соответ"ственно с первыми - третьими входами 2 ртретьей группы элементов ИЛИ, выходыкоторой подключены к суммирующим входам одиннадцатого - тринадцатого вычитателей, управляющий вход второгобуферного регистра является первым 25управляющим входом блока, управляющиевходы первого и третьего буферных регистров объединены и являются вторымуправляющим входом блока, управляющиевходы четвертого и пятого буферных ЭОрегистров объединены и являются третьим управляющим входом блока, управляющие входы шестого - восьмого буферных .регистров объединены и являютсячетвертым управляющим входом блока,управляющие входы четвертой и седьмой групп элементов И объединены иявляются пятым управляющим входомблока, управляющие входы третьей ишестой групп элементов И объединены 4 ри являются шестым управляющим входомблока управляющие входы пятой и восьмой групп элементов И объединены иявляются седьмым управляющим входомблока, управляющие входы второй ипервой групп элементов И являютсясоответственно восьмым и девятым уп"равляющими входами блока, выходы шестого - восьмого буферных регистровявляются соответственно шестыми -восьмыми выходами блока.5. Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок управления выполнен на дешифраторах, триггерах, сумматорах по модулю 2 - 1), элементах сравнения, элементах И,элементах ИЛИ, группах элементов И, группе элементов ИЛИ, шине логического нуля и счетчике, выходы которого 981 22соединены с входами первого дешифратора, первый и второй входы первого элемента И являются соответственно тактовым входом и входом "Пуск" блока выход первого элемента И соединен с входом счетчика и является первым выходом блока, первый - четвертый входы второго дешифратора являются одноименными информационными входами блока, выход нулевого разряда второго дешифратора подключен к первым входам первого элемента ИЛИ и второго элемента И, выходы первого, второго и четвертого разрядов второго дешифратора соединены соответственно с вторым входом первого элемента ИЛИ и первыми входами третьего и четвертого элементов И, выходы восьмого, девятого и пятнадцатого разрядов второго дешифратора соединены соответственно с третьим и четвертым входами первого элемента ИЛИ и первым входом пятого элемента И, выход которого является вторым выходом блока, первый выход первого дешифратора является третьим выходом блока, второй выход первого дешифра-. тора подключен к тактовым входам первого - пятого триггеров, выход первого элемента ИЛИ соединен с первым входом шестого элемента И, выход которого подключен к информационному входу третьего триггера и первому входу второго элемента ИЛИ, выход которого подключен к первым управляющим входам первой и второй групп элементов И, первый выход первого элемента сравнения подключен к первым входам седьмого - девятого элементов И, первый выход второго элемента сравнения соединен с вторым входом девятого элемента И, выход которого под- ключен к вторым входам третьего, чет вертого и шестого элементов И, второй выход первого элемента сравнения соединен с первым входом десятого элементаИ, выход которого соединен с вторым входом второго элемента И, выход которого соединен с первым информационным входом четвертого триггера и первым входом третьего элемента ИЛИ, выход которого соединен с первым управляющим входом третьей группы элементов И, второй выход второго элемента сравнения подключен к второму входу десятого элемента И и первому входу четвертого элемента ИЛИ, выход которого соединен с вторым2314 входом седьмого элемента И, выход которого подключен к второму информационному входу четвертого триггера и второму входу третьего элемента ИЛИ, выход третьего элемента сравнения соединен с первым входом пятого элемента ИЛИ, выход которого подключен к второму входу восьмого элемента И, выход которого соединен с информационным входом пятого триггера и третьим входом третьего элемента РЛИ, выходы первого сумматора по модулю (2 - .1) соединены с первыми входами четвертого элемента сравнения, первый и второй выходы которого соединены соответственно с вторым входом четвертого элемента ИЛИ и третьим входом третьего элемента И, выход которого подключен к информационному входу первого триггера и второму входу второго элемента ИЛИ, выходы второго сумматора по модулю (2 " 1) соединены с первыми входами пятого элемента сравнения, первый и второй выходы которого соединены соответственно с вторым входом пятого элемента ИЛИ и с третьим входом четвертого элемента И, выход которого подключен к информационному входу второго триггера и третьему входу первого элемента ИЛИ, выходы первой - третьей групп элементов И соединены соответственно с первыми - третьими входами группы элементов ИЛИ, выходы которой соединены с первыми входами шестого элемента сравнения, выход которого подключен к входу шестого и информационному входу седьмого триггеров, прямой и инверсный выходы шестого триггера подключены соответственно к второму управляющему входу второй группы элементов И и к вторым управляющим входам первой и третьей групп элементов И, выход седьмого триггера соединен с информационным входом восьмого триггера и является четвертым выходом блока, выход восьмого11981 24 триггера соединен с первым входомодиннадцатого элемента И, выход которого является пятым выходом блока,третий выход первого дешифратора соединен с тактовыми входами седьмогои восьмого триггеров, четвертый выход первого дешифратора подключен квторым входам пятого и одиннадцатого 10 элементов И, вторые входы четвертогоэлемента сравнения являются пятымиинформационными входами блока, первые входы первого и третьего элементов сравнения и первого сумматора по 15 модулю (2 - 1) соответственно объединены и являются шестыми информационными входами блока, первые входывторого элемента сравнения и второгосумматора по модулю (2 - 1) и вторые 2 О входы третьего элемента сравнения нпервого сумматора по модулю (2 - 1)соответственно объединены и являютсяседьмыми информационными входами блока, вторые входы первого и второго 25 элементов сравнения и второго сумматора по модулю (2 - 1) соответственно объединены и являются восьмыми информационными входами блока, втбрыевходы пятого элемента сравнения.яв- ЗО ляются девятыми информационными входами блока, информационные входы первой в ,третьей групп элементов И являются соответственно десятыми -двенадцатыми информационными входами блока, пятые выходы первого дешифратора 35соединены с вторыми входами шестогоэлемента сравнения, шестые - девятыевыходы первого дешифратора являютсяодноименными выходами блока, шинанулевого потенциала соединена с десятыми выходами блока, десятые -двенадцатые и тринадцатый - шестнадцатый выходы первого дешифратораявляются соответственно одиннадцатыми - семнадцатыми выходами блока,выходы первого - пятого триггеровявляются соответственно восемнадцатым - двадцать вторым выходами блока, 14119811411981 Составитель О. РевинскийТехред М.Дидык Корректор М, Демч едактор И. Шул Заказ 3673/56 8 П наб., д Производственно-полиграфическое предприятие, г, Ужгоро Проектная, 4 Тираж ВНИИПИ Гос по дела 035, МосквИзобретение относится к вычислительной технике и технике связи и может быть использовано в системах хранения, передачи и обработки информации,Цель изобретения - повышение достоверности декодирования,На Фиг. 1 приведена блок-схемаустройства для декодирования с исправлением ошибок; на фиг.2-5 - Функциональные схемы соответственно Формирователя проверочного символа, блокаисправления ошибок, блока вычисленияошибочных позиций и блока управления;на фиг. 6 в . временные диаграммы сигналов.Устройство для декодирования с исправлением ошибок (Фиг. 1) содержитблок 1 задержки, первый - четвертыйформирователи 2-5 проверочного символа, блок 6 исправления ошибок,блок 7 вычисления ошибочных позиций,блок 8 управления, элемент И 9 и элемент ИЛИ 10, а также информационный11 и тактовый 12 входы, вход 13"Пуск" и выход 4.Блок 1 задержки представляет собойа (2 + 6)1 -разрядный сдвиговыйрегистр, где ш - разрядность символавходного кода. Первыми выходами бло-ка 1 являются выходы первого - ш-горазрядов регистра, вторыми выходамиблока 1 - выходы (2 + 5)-гос ш (2 + 5) -го разрядов, третий вьгход блока 1 - выход последнего разряда регистра.Каждый из Формирователей 2-5(Фиг. 2) выполнен на первом - пятомбуферньх регистрах 15-19, первом 20и втором 21 сумматорах по модулю(2 - 1), преобразователе 23 кода иэлементе И 24. На фиг. 2 обозначеныпервые 25 и вторые 26 информационныевходы, первый - пятый управляющиевходы 27-31, первый 32 и вторые 33выходы.Блок 6 исправления ошибок (Фиг. 3)выполнен на буферном регистре 34,вычитателе 35 по модулю.(2 - 1),преобразователе 36 кода, сумматоре37 по модулю (2 - 1) и сдвиговом регистре 38. На Фиг. 3 обозначены первые 39 и вторые 40 информационныевходы, первый - третий управляющиевходы 41 - 43 и выход 44.Блок 7 вычисления ошибочных позиций (фиг. 4) выполнен на первом -5 О 5 20 25 ЗО 35 40 тринадцатом вычитателях 45-57, первом 58 и втором 59 сумматорах, первом восьмом буфепных регистрах 60-67, первом - четвертом преобразователях 68 - 71 кода, первый - восьмой группах 72-79 элементов И и первой третьей группах 80-82 элементов ИЛИ.На Фиг. 4 обозначены первые - четвертые информационные входы 83-86, первый девятый управляющие входы 87-95, первые - восьмые выходы 96-103.Блок 8 управления (фиг. 5) выполнен на счетчике 104, первом 105 и втором 106 дешифраторах, первом - шестом элементах 107-112 сравнения, первом 113 и втором 114 сумматорах по модулю (2 - 1), первом - восьмом триггерах 115-122, первом - пятом элементах 123-127 ИЛИ, первом - одиннадцатом элементах 128-138 И, первой - третьей группах 139-141 элементов И группе 142 элементов ИЛИ и шине 143 нулевого потенциала. На фиг. 5 обозначены первый - четвертый информационные входы 144-147, пятые - двенадцатые информационные входы 148 - 155, первый - пятый выходы 156-160,. шестые - тринадцатые выходы 61-168, четырнадцатый - двадцать второй выходы 169-177. Кроме того, .на фиг. 5 обозначены сигналы в различных точках схемы, временные диаграммы которых показаны на фиг, 6. Сигналы, обозначенные Я - 3 , образуют четыре группы, причем при 1 = 0 - это сигналы на шестых выходах 161, при1 - на седьмых выходах 162, при 2 - на восьмых выходах 163, при 1 3 - на девятых выходах 164 блока 8.Принцип действия устройства для декодирования с исправлением ошибок заключается в следующем.Кодовые слова, поступающие на вход 11 устройства, содержат по (2 - 1) ш-разрядных информационных символов К; (1. = О, 12 - 2) и четыре проверочных символа К (8 = О,2, 3), формируемых в кодирующем устройстве по формуле2Ф1=ои передаваемых после информационныхсимволов. Знак,Ж обозначает суммиро3ванне в поле СР(2 ), примитивный элемент скоторого является корнем неприводимого многочлена Е(х) степени ш, "+" - сложение в кольце по модулю (2 - 1).Если в информационной части кодового слова при передаче или хранении информации возникают ошибки в двух символах, то й"Ъ - сформированные в 10 декодере проверочные символы определяются иэ уравнения9: ,9 Е .В (2)ааО( 91 Ч5 где 8 и 8 - величины ошибок на 9-йи -й позициях соответственно, "(+ - сложениев поле СР (2 ).Формирование проверочных символов в соответствии с формулой (1) можно записать таклВ . м ,с "зкф,к,+96 кк-гс 1 г -м 1411981 или Иэ (6) при я = О, 1, 2,и Э полу 25 чают 1-Д-Ь Ь Ь-Ь-Ь Обозначим а 1 = ь, - а, , а : д 30 1 з з аТогда условие одной ошибки в ин, формационной части можно записать+Ъы - и - г"- г) 1Приня ые провероч е символы 1 9 45в общем случае могут иметь ошибки,тогда 50 Рассмотрим возникающие ситуации.1. Если в информационной части содержится одна ошибка, то уравнение (2) принимает видЪ 9 1 (Р9 3 (4) 557 ФВ этом случае синдромы ошибок иэ уравнений (1)и (4) имеют вид или Обозначим. сумму первых двух членов ы,к 1, сумму " с третьим членом й а и т.д. Тогда1кеЕк+фк,+Я+ Ц(ке-к 1-1 илиК, 1 с, +И+у (1 со 1 с К)е Ф (в) 1 9 ф и операции сложение "+" и вычитание "-" производятся по модулю (2 - 1).В общем случае имеем а =г 0+4 лТак как ошибка по предложению находится в информационной части, то Ф,=к; к 9 м я 9 ь Фкили ь = е Ъ + 1 сЗ + 9(3, (6) 1=а =а а а; 1 й Исправление ошибки заключается в замене принятого ошибочного символа 1 с 91 с + 8 на исправный. Из (5) при и = ОилиМ) ,+М(кф а)2. В случае двух ошибок из уравнений (1) и (2)находим7 1411981Продолжение табл.1э2- Ь,-Ь,-Ч(-Ь,)или 1- Ь,+-Ь;Ч(-Ь,) . Ои с учетом второго свойства Функции ОО 3 О 1 ООО 3 О 1 О ОО 11 13 О ОО 3 О 1 - Ф(.-Р - О10 О 1 ОО О 03 ООО 1 Ь, - Ь, + Ь, -+ М(Ь,-ф) - Ои, вводя функцию й(г) (26), получаем Е(Ъ -ф) Ь - Ь (27) 0101 1010 0000 0100 1301 О 10 0311 100 0001 П р и м е р. Решить квадратноеуравнение в поле СР (2 ) 1030 0010 1000 0001 0113 1001 20 0101 1010 0000 Из (24) Ьх, = 11; Ьрх - х,7 - 11 11; Е(11-.) 11-11 = ОВ соответствии с табл. 2 1125 5, 10, , 11-10= 1 и Д=31-56.условием появления двух ошибок винформационной части является д,3ф(ф 4 ф30 3Если синдром ошибки по я-у проверочному символу д =во, то при Ь,==ф и (или) д =о вычисление Ь, и Ьосуществляется по формулам (24).4, Если д = фо, то из (20)Й- у - - к Ш ф ф ИЛИ Х щЬ -Ьд +Ьз+ Ьов 1001 011 1 0001 3110 0011 0010 0100 3101 0110 0101 0100 0003 1011 1100 1000 50 откуда с учетом (7) Ь щ хр " а 3Ьр а,.Исправление ошибок по пп. 2 - 5,аналогично п. 1 и осуществляется поФормуле (9) для , ипозиций последовательно ( , е).6. Если одна ошибка в информационной части, а вторая - впервом проверочном символе (1 с ), то в соответствии с условием (8) 0010 1000 3010 0000 К(г) И, ге В обеих таблицах запись 1111 эквивалентна записиУчитывая, что 9(фд)О, переписываем уравнение (25)- ь, - е(ь.-) - о . Ю фО+ Ыф Эк, = О.10 411981 дЗ Ь Ьг 8 г а)= Ь Ьу,и в,= Ь,-Ь 0; аг = Ьг+г, Ь 1 ю Ьр Ь(Ь Ь Вариант О О О О д дг аЗ Одна ошибка Две ошибки (общийслучай) 0000 Две ошибки ( аро или (и) Ь о )"000 во втором проверочном символе 00 0 а,+ аг= Ь - Ь, Ф в третьем проверочном символе О О"0+ аз Ь Ь ф з а,=а; а Фд 1111 Ошибок нет не определено. фа: а аЗ " З 1, Если одна ошибка в информационной части, а вторая - во втором проверочном символе, то 1а= Ь,- Д, = Ь-Ь,-8,; откуда а + а = Ьг - Ь,аФ азюПри этом в п. 4 а+ аг Ф Ьг8, Если одна ошибка в информационной части, а вторая - в третьем про-,верочном символе, то Две ошибки ( Ь,=ю ) 0 1 О 0 Две ошибки ( Ь : фо ) 0 0 1 0 Одна ошибка в информационной части,а вторая:в первом проверочном символе в четвертомпроверочном символе 0 0 О откуда а + а = Л - ЬЙ Э З5а, Фа, =а 9. Если одна ошибка в информационной части, а вторая - в четвертом проверочном символе, то а Ф аз, е)=а; а =а Исправление ошибки в информацион ной части по пп, б - 9 заключается внахождении номера ошибочной поэиции"( = аз для пп. 6 и 7 и )-" д дляпп. 8 и 9) и определении правильногосимвола с по Формуле (11).20 10, Если при хранении или передаче информации ошибок нет, то все синдромы равны оэВсе укаэанные варианты сведены втабл. 3.ФТаблица 3 а а ФаЬ а та Фа а,+ аг 1 Ьг - 6, а + а Ф Ьз - ь11 14Устройство работает следующим образом,При поступлении сигнала "Пуск" наэлемент И 128 блока 8 управления тактовые импульсы с входа 12 начинаютпоступать на вход счетчика 104 и натактовый выход блока 1 (регистра),который начинает пропускать блокикодовых слов по (2 + 3)-раэрядныхсимволов в каждом блоке. Первые штактов следует нулевой цикл, в течение которого заполняются первые шразрядов регистра блока 1,В следующем первом цикле (вторыеш тактов) по сигналам 3 (1 = О 12, 3), поступающим на входы 27 формирователей 2 - 5, производится перепись первого ф,) символа с первыхш разрядов регистра блока 1 на регистры 15 формирователей 2 - 5, а затем его сложение с "нулем" входов 26на сумматоре 20 (так как в формуле(2) г = О) и запись результата в буферный регистр 16 по сигналам Я,поступающим на входы 28 формирователей 2-5. Затем на вычитателях 22осуществляется вычитание содержимогорегистров 16 (К,) из содержимого ре"гистров 18 ( ю - отсутствие информации), Результат вычитания () поступает на преобразователи 23, работаю- .. щие по табл. 1 (для ш4), и ре-.зультат преобразования ("О") складывается с содержимым регистра 16 (Е,)на сумматорах 21 и записывается на,буферные регистры 17 по сигналам Я,поступающим на входы 29 преобразователей.Во втором цикле (третьи ш тактов)по сигналам ф производится перепись второго (1 с,) символа с регистраблока 1 на регистры 15 формирователей2-5 и затем его сложение с величинойД щ 1 - позиция поступающегосимвола, формула (2, поступающейна входы 26 формирователей 3 - 5 свыходов 166 - 168 блока 8 управленияна сумматорах 20, и запись результатов на буферных регистрах 16 посигналам, Я, Одновременно по сигналам , поступающим на входы 30формироваелей 2-5, производится перепись содержимого регистров 17 нарегистры 18, Затем на вычитателях 22осуществляется вычитание содержимогорегистров 16 (М ) из содержимого регистров 18. Результат вычитания(1- 1 с, - ц) поступает на преобра 12 11981формирователе 3 - перепись второго синдрома ь, с.регистра 17 на регистр18 по сигналу, далее - на регистр19 по сигналу, а сформированной на вычитателе 46 блока 7 вычисления ошибочных позиций разностиа, = Ь, - Ь по сигналу 1 - на ре 50 гистр 61. В 19-м цикле (О-й цикл следующего блока) аналогично 17-му циклу на четвертом формирователе 5 производится формирование четвертого синдрома ошизователи 23, а результат преобразования складывается с содержимым регистров 16 ф ) на сумматорах 21 изаписывается в буферные регистры 17по сигналам ф .ЭЦиклы с третьего по пятнадцатыйаналогичны второму циклу, причем всоответствии с формулой (3) множитель 10 при а (г - позиция символа) в каждомпоследующем цикле увеличивается на 1по сравнению с предыдущим.В 16-м цикле по сигналу Я, производится перепись с регистра блока 1первого проверочного символа 1 наРрегистр 15 первого формирователя 2,затем сложение его с 0 на сумматоре 20 и запись результата сложения(1 ) на регистр 16 по сигналуО йОдновременно по сигналу Я производится перепись содержимого регистра17 (ко) на регистр 18. Затем на вычитателе 22 осуществляется вычитание 25содержимого регистра 16 (Е ) нэ соо Ъ.,держимого регистра 18 (к ), Результатвычитания поступает на преобразова тель 23, затем на сумматоре 21 производится сложение Ф(1,-К ) с содержимым регистра 16 (1 с,) и запись ре-,зультата ( Ь = 1 с + Ч(1 -1 с ) на регистр 17 по сигналу 3В 1-м цикле аналогично 16-му навтором формирователе 3 производитсяформирование второго синдрома ошибок Зб Ь,Е, + Чфр ) с записью результата на регистр 17 по сигналуоВОдновременно по сигналупроизво"4дится перепись первого синдрома оши бок Ь с регистра 17 на регистр 18ви далее по сигналу у - на регистр19 первого формирователя 2.В 18-м цикле аналогично 17"му натретьем формирователе 4 производится 45 формирование третьего синдрома ошибокс записью результата на рег3 4 бок А с записью результата на ре 33гистр 17 по сигналу фв , в третьем формирователе 4 - перепись третьего синдрома Ь с регистра 17 на регистр18 по сигналу, далее - на регистр 9 по сигналу, а сформированных на вычитателях 45 и 47 блока 7 вычисления ошибочных позиций раз-костей Ь -Ь, и а= Ь -Ь, на регистры 60 и 62 соответственно по сигналу 1 в.В 20-м цикле (1-й цикл следующего блока) в четвертом формирователе 5 осуществляется перепись четвертого синдрома а с регистра 17 на регистр 18 по сигналу в, далее - на регистр 19 по сигналу, а сформи 3рованных на вычитателях 48 и 49 блока 7 вычисления ошибочных позицийразностей ав = Ь - Ь и Ьв - Ьна регистры 63 и 64 соответственно по сигналу ф 9 Если при передаче или хранении информации возникает одна ошибка, то в соответствии с условием (8) синдромы ошибок Дф и выходы элеФментов И 24 формирователей 2 - 5 имеют низкий потенциал, который с выходов 32 формирователей, поступая на входы 144 - 147 блока 8 управления, ,возбуждает первый выход (О) дешифра:тора 06, а выходы регистров 61 ,63 имеют поразрядно равные потенциалы (а = а = а,), которые с выходов 197 - 99 блока 7 формирования ошибочных позиций поступают на входы 149 - 151 блока 8 управления и, возбудив выходы "=" элементов 107 и 108 сравнения, создают высокий потенциал на выходах элементов И 129 и 137 и элемента ИЛИ 125, возбуждают первый информационный вход триггера 118 по сигналу , с дешифратора 105 устанавливают триггер 118 в единичное положениеЭтот сигнал с выхода 176 блока 8 управления через вход 94 блока 7 вычисления ошибочных позиций 7 открывает группу 73 элементов И, на информационных входах которых присутствуют потенциалы выходов регистра 63 (величина аз = ) - ошибочный разряд), которые через группу 80 элементов ИЛИ по сигналу ую с выхода 172 блока 8 управления записываются На регистр 65. С выходов 101 блока 7 вычисления ошибочных позиций через 6 ходы 155 эти потенциалыпоступают 11981 14на информационные входы группы 139элементов И совместно с потенциаламис выхода элемента ИЛИ 125 и инверсно"го выхода триггера 120, затем нагруппу 142 элементов ИЛИ и на первыевходы элемента 112 сравнения, Науправляющий вход 41 блока 6 исправления ошибок поступают импульсы 10 с выхода 158 блока 8 управления, покоторым в каждом цикле производитсяперепись (2 + 6)-го символа из регистра блокана регистр 34 блока 6исправления ошибок. При сравнении 5 информации, поступившей на первые:входы элемента 112 сравнения с сигФналами а на его выходе = ноявлям 3ется сигнал Ъ , по заднему ФРонтУкоторого триггеры 120 и 121 устанав ливаются в единичное положение, приэтом элементы И группы 141 закрываются, а на выход 159 блока 8 управления,и далее на вход 42 блока 6 исправления ошибок поступает импульсЪ, по которому сформированная насумматоре 37 сумма 1 с (Формула (9записывается на сдвиговый регистр 38.По переднему фронту очередного импульса у триггер 121 сбрасывается,ЮЗ 0 устанавливая триггер 122 в единичноесостояние, разрешающее передачу пачки из в символов с выхода 160 блока8 управления на вход 43 блока 6 исправления ошибок, по которой осущест вляется последовательная передачазаписанного в регистр 38 исправленного символа с выхода 44 блока 6 иавторой вход элемента ИЛИ 1 О и далеена выход устройства. По переднему 40 фронту очередного импульса Я, триггер 122 сбрасывается, запрещая выдачу сигналовна выход 160 блока 8Нуправления.145 Если происходят две ошибки и Ь ФФ о (д = О, 1, 2, 3) или Ь, = оо и.(или) Ь =о , то сигнал с нулевого,впервого, восьмого или девятого выходов дешифратора 106 через элемент 50 ИЛИ 23 совместно с сигналом с выходаэлемента И 136 при наличии высоких1 11потенциалов на выходах = элементов107 и 108 сравнения поступают наэлемент И 133, сигнал с которого устанавливает триггер 117 в единичндесостояние, по которому сформированные на вычитателях 51-53, преобразователях 68 и 70 и сумматорах 58 и59 с вычитанием блока 7 вычисления15 14ошибочных позиций коэффициенты Ъх, и Ъ (по формулам (21) и (24)соответственно) уравнения (23) поступают через элементы И групп 75 и 78 ии элементы ИЛИ групп 81 и 82 на вычитатель 55, где формируется Г(Ь-)= Ь - Ь (формула 27), затем на преобразователе 71, реализующем табл. 2(при ш = 4), по разности Ъ - Ь определяются два значения Ь -=ях , а по последним на вычитателях56 и 57 - два корня , = Ьр - я и= Ь - г, уравнения (23), которыепо сигналу , , поступающему с выхода 172 блока 8 управления на вход 90блока 7 вычисления ошибочных позиций,записываются на регистры 66 и 67 соответственно и затем с выходов 102и 103 поступают на входы 153 и 154блока 8 управления и информационныевходы групп 139 и 140 совместно ссигналом с выхода элемента ИЛИ 124,на один вход которого поступил высокий потенциал с выхода элементаИ 133, причем элементы И группы 139открыты нулевым плечом триггера 120;Поэтому информация о номере первойошибочной позиции , через группу42 поступает на первые входы элемента 112 сравнения, и при сравнении еес потенциалами Яц., поступившимина вторые входы элемента 112 сравнения на его выходе = появляетсясигнал Ь по заднему фронту которого триггеры 120 и 121 устанавливаютсяв единичное состояние, при этом элементы И группы 139 закрываются, аэлементы И группы 140 открываются,пропуская второй номер ошибочной позиции. Далее прохождение сигналов и исправление ошибки на ,-йпозиции аналогично для одной ошибки.При сравнении ошибочной позициина первых входах элемента 112 сравнения с очередными потенциалами 1,на его выходе = появляется сигналЬ по переднему фронту котороготриггер 120 возвращается в исходноеположение, а по заднему фронту триггер 121 устанавливается в единичноесостояние. Далее прохождение сигналов и исправление ошибки аналогичнодпя одной ошибки,Если происходят две ошибки и ь, ==ад или Ь =оо, то потенциалы с второгоили четвертого выходов дешифратора106 совместно с сигналами с выходаэлемента И,136 и с выходов "=" эле 11981 16ментов 110 или 111 сравнения через элементы И 130 и 131 устанавливают триггер 115 или 116 в единичное состояние, по которому с выходов 174 или175 блока 8 управления и входы 92 и93 блока 7 вычисления ошибочных позиций группы 74 и 77 или 76 и 79 пропускают сигналы Ь = а с выходов10 регистра 63 и Ьь - ь "а с вьюо 3ходов вычитателя 50 или ЪЬ - ьЬа, с выходов вычитателя 54, и Ь = ас выходов регистра 61 на группы 81и 82. Далее происхождение сигналов и15 исправление ошибок аналогично общемуслучаю для двух ошибок.Если происходит одна ошибка в информационной части, а вторая - в первом или во втором проверочном симво 20 ле, то при выполнении равенстваа = а на элементе 108 сравненияили равенства а + а = ь - ь наг. т оэлементе 110 сравнения и при наличиинеравенства а 1аз на элементе 10725 сравнения триггер 118 устанавливаетсяв единичное состояние по второму информационному входу. Дальнейшее прохождение сигналов и исправление ошиб. ки в информационной части аналогично30 для одной ошибки,Если происходит одна ошибка в информационной части, а вторая - в третьем или четвертом проверочном символе, то при выполнении равенстваа, = а на элементе 109 сравненияили равенства а + а = ь в ь на2. Зэлементе 111 сравнения и при наличиинеравенства а, Ф а на элементе 107сравнения триггер 119 устанавливается40 в единичное состояние, по которому свыхода 177 блока 8 управления и вход95 блока 7 вычисления ошибочных позиций группа 72 пропускает сигналыа через группу 80 на регистр 65.45 Дальнейшее прохождение сигналов и ис"правление ошибки в информационнойчасти аналогично для одной ошибки.При отсутствии ошибок на выходе15 дешифратора 106 высокий потенциал,разрешающий передачу сигналовчерез элемент И 132 и выход 157 блока8 управления на второй вход элемента И 9, по которым осуществляетсяпередача неиспорченных символов с65 третьего выхода блока 1 через элемент ИЛИ 10 на выход 14 устройства.Таким образом, в устройстве длядекодирования производится определение одной или двух позиций одного

СмотретьЗаявка

4169250, 29.12.1986

ОРГАНИЗАЦИЯ ПЯ В-8466

КАРПУХИН АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: декодирования, исправлением, ошибок

Опубликовано: 23.07.1988

Код ссылки

<a href="https://patents.su/17-1411981-ustrojjstvo-dlya-dekodirovaniya-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для декодирования с исправлением ошибок</a>

Предыдущий патент: Устройство для декодирования модулярного кода

Следующий патент: Система высокочастотной связи

Случайный патент: Способ очистки цис-диамминдихлорплатины (ii)