Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 964736

Автор: Конопелько

Текст

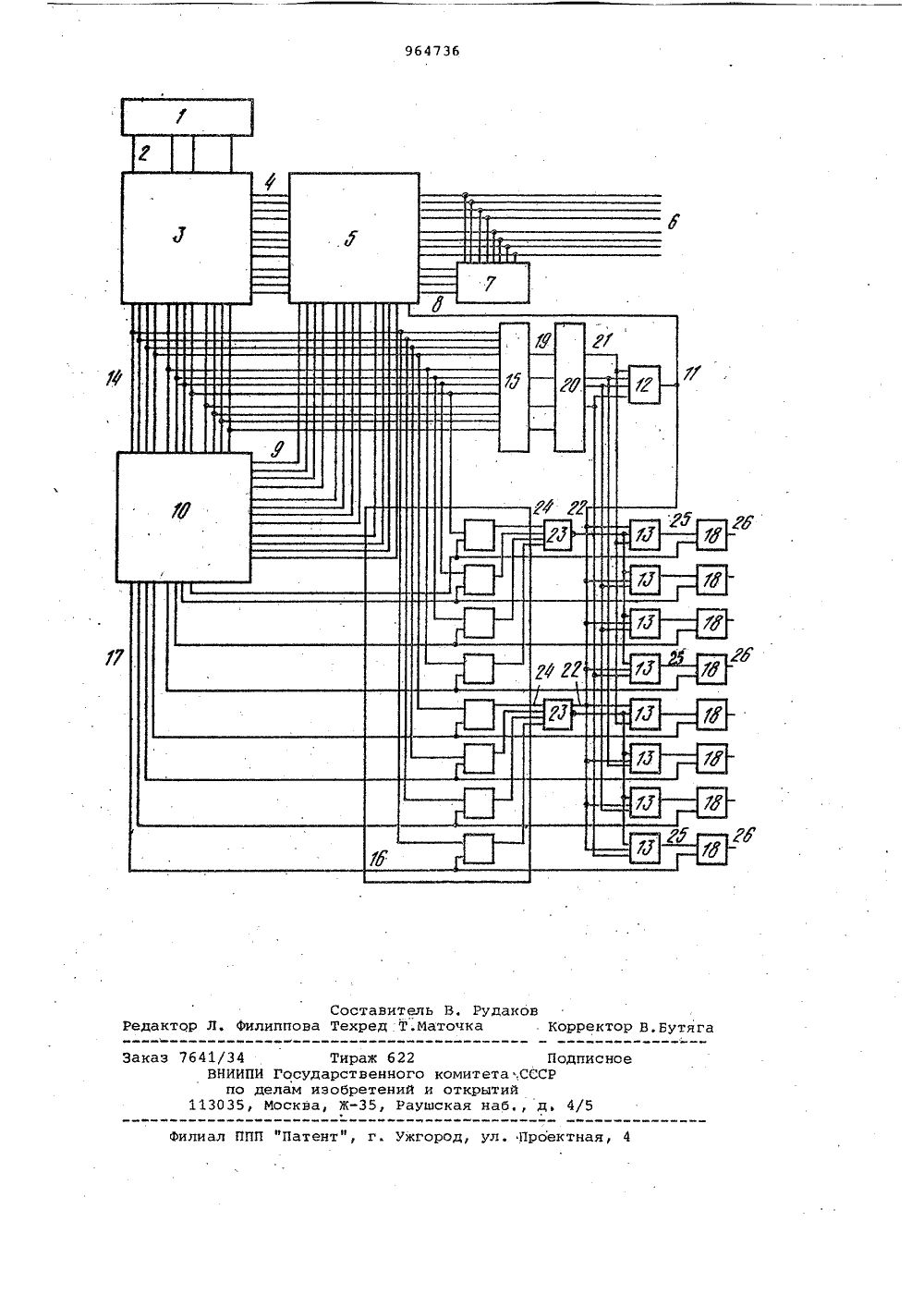

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическихРеспублик 11964736 РСКОМУ СВИДЕТЕЛЬСТВУ.81 ( 51 М. Кп 22) Заявлено Об 6760/18-2 1 С 29/О с присоединени аявки Мо дарственныи комитетСССРдедам изобретенийи открытийубликован та опублик кзллетень Мо 37 сания 07. 10. 82 вания опи 72) Авторизобретения ВЕСФВЗНИПАТЕИИО.ТЕХНИЧЕСКАРИЛИ К. Конопелько Минский радиотехнический институт(54) ВАПОМИНА О стройстве ч необходимы в слове, в кодирующих 2 Изобретение относится к запоминающим устройствам и может быть использовано при создании систем памяти набазе интегральных микросхем памяти(ИМП) со словарной организацией.Известно запоминающее устройствос исправлениемошибок, в котором дляавтоматического исправления ошибок,возникающих из-за отказов ИМП, подлежащие хранению данные кодируются спомощью кодов, исправляющих ошибки.Устройство содержит избыточные разряды кодируюирте и декодирующие блоки,Г 12Однако в этом у исло избыточных разрядов, х дляисправления ошибок еликои высока сложность и декодирующих блоков,Наиболее близким по техническойсущности к предлагаемому изобретениюявляется запоминающее устройство, содержащее накопитель, первые входы которого соединены с выходами адресногоблока, вторые входы накопителя соединены с выходами блока записи, первые,вторые, третьи и четвертый входы блока записи соединены соответственнос шинами записи информации и входамиблока кодирования, с выходами блока. кодирования, .с инверсными выходамипервого регистра и с выходами элемен"та ИЛИ, входы первого регистра соединены с выходами накопителя, входамиблока вычисления синдрома и первымивходами блока сравнения., вторые входы блока сравнения соединены с прямы"ми выходами первого регистра и с пер"и входами корректирующих сумматоров по модулю два, выходы блока вычисления синдрома соединены с входами регистра, выходами соединенногос входами элемента ИЛИ. Устройствопозволяет производить коррекцию отка.завших разрядов при использовании помехоустойчивого кода (2).Однако известное устройство требует большое число дополнительных разрядов элементов памяти при коррекциичетырех или восьми отказов в слове,а также требует сложных кодирующихи декодирующих схем.Целью изобретения является повышение надежности устройства.5 Поставленная цель достигается темчто в запоминающее устройство с исправлением ошибок, содержащее адресный блок, накопитель, блок записи,первый и второй регистры числа, блок 0 кодирования, схему сравнения, Форми"рователь проверочных сигналон, сумматоры по модулю два и элемент ИЛИ, причем входы накопителя подключены к выходам адресного. блока и блока записи, одни из входов которого и входыблока кодирования объединены и явля"ются одними извходов устройства, адругие входы блока записи соединены соответственно с выходами блока кодирования и элементов ИЛИ и инверснымивыходами первого регистра числа, пря О мые выходы которого подключены к одним из входов схемы сравнения и к пер вым входам сумматоров по модулю два, выходы накопителя соединены с входами первого регистра числа, другимивходами схемы сравнения и входамиформиронателя проверочных сигналов,выходы которого подключены к входам второго регистра числа, выходы которого соединены с входами элементаИЛИ, введены элементы И и элементыИ-НЕ, входы которых подключены к выходам схемы сравнения, а выходы соединены с первыми входами элементовИ, вторые входы которых подключенык выходам второго регисТра числа,третьи входы - к выходу элемента ИЛИ, а выходы элементов И соединены с вторыми входами сумматоров по модулю дна. Ф На чертеже изображена структурная 30 и входами элементов И 13. Входы регистра 10 соединены с выходами накопителя 14, входами формирователя 15 проверочных сигналов и одними из входов схемы 16 сравнения. Другие входы схемы 16 сравнения соединены с прямйюи выходами 17 регистра 10 и с первыми входами корректирующих сумматоров 18 по модулю два. Выходы фор- зО мирователя 15 соединены с входами 19 второго регистра 20 числа, выходами соединнного с входами 21 элемента ИЛИ 12 и одними из входов элементов И 13. Другие входы элементов И 13 55 соединены с выходами 22 элементов И-НЕ 23. Входы элементоН И-НЕ соединены с выходами 24 схемы 16 сравнения. Выходы элементов И 13 соединены с вторыми входами 25 сумматоров 6 р 18 .по модулю два. Выходы 26 сумматоров 18 являются выходами устройства.Блоки 7 кодирования и формирователя 15 состоят из сумматоров по модулю два. 65 схема запоминающего устройства,Запоминающее устройство содержитадресный блок 1, соединенный адресными шинами 2 с первыми входами накопителя 3. Вторые входы накопителя 35соединены с выходами 4 блока 5 записи. Входы блока 5 записи соединенысоответственно с шинами 6 записи ивходами блока 7 кодирования, с выходами 8 блока 7 кодирования, с инверс ными выходами 9 первого регистра 10,числа с выходом 11 элемента ИЛИ 12 Блок 5 записи разрешает запись й 2 формации в накопитель 3 или с шин за,писи б или с инверсных выходов 9 регистра 10 и.может быть реализован наэлементах 2-2 ИИЛИ.. В режиме записи информации устройство работает следующим образом.Двоичное кодовое слово А длиныЫ + Ь, первые 1 = Ьп разрядов которого являются информационными а по)следние Ь разрядов контрольными, помещается.в накопитель 3 по адресу,поступающему из адресного блока 1.В блоке 7 кодирования происходит вычисление контрольных символов путемсуммирования по модулю два блоковпо Ь разрядов в каждом.П ри м е р 1, Пусть 1 с = 16,16Ь = 4, тогда и = 4 = 4, т.е, при построении накопителя с длиной словав 1 б,разрядов используется четыреИМП с четырьмя шинами записи-считывания каждая и пусть в накопитель записывается информация 1 0 0 0 1 1 0 000101111.Тогда н контрольные разряды записывается информация 1 0 0 1, т.е.н накопитель заносится слово 1 О 0 01100.001011111001.В режиме считывания информации выходные данные подаются на формирователь 15 и одновременно записываютсян регистр 10, Формирователем 15 вырабатывается признак (синдром), записываемый во второй регистр 20, которыйравен нулю, .если ошибок нет, и неравен нулю в противном случае.Если в считываемом слове ошибокнет, то на выходе элемента ИЛИ 12 будет нулевой сигнал, который устанавливает на выходах 25 элементов И 13нулевые сигналы. Тогда на выходе 26устройства поступят сигналы с прямыхвыходов 17 перного регистра 10 безизменения,Если же в считываемом слоне. имеются ошибки в разрядах из-за отказа любой одной ИМП, то на выходе элемента ИЛИ 12 появится единичный сигнал, который разрешит повторную запись инвертированной считанной информации с выходов 9 первого регистра 10 в накотитель 3. После этого производится контрольное считывание хранимой инвертированной информации по тому же адресу и сравнение ее н схеме сравнения 16 с хранимой неинвертиронанной информацией в регистре 10. Запись считанной инвертированной информации в регистр 10 и вычисленного формироватепем 15 синдрома в регистр 20 не происходит, т.е. в регистрах 10 и 20 хранится информация, относящаяся к неинвертированному слову. Тогда как минимум на одном из выходов 24 схемы 16 сравнения появится нулевой сигнал,10 15 20 35 если искаженным является один изЬп информационных разрядов, В этом случае на одном из выходов 22 одного из и элементов И-НЕ 23 появится единичный сигнал, который откроет одни из элементов И 13, относящиеся ) к искаженному блоку информации. Поскольку элементы И 13 открыты единич-. ным сигналом с выхода элемента ИЛИ 12, то на выходе одних из элементов И 13 появятся сигналы, отображающие ненулевой синдром неинвертированного слова, При сложении н сумматорах 18 по модулю два этого синдрома с информацией, относящейся к этому блоку, происходит коррекция считываемой ин-. Формации из искаженного блока (отказавшей ИМП).Если же искаженными являются контрольные разряды, то на выходах 24 схемы 16 сравнения будут единичные сигналы, а на выходах 22 элементов И-НЕ 23 - нулевые .сигналы. Тем самым элементы И 13 будут закрыты и информация, считываемая с регистра 10, поступит на выходы 26 устройства без изменения.П р и м е р 2. Пусть в примере 1 информация искажена в первом блоке иэ-за отказа этой ИМП, т.е. в регистр 10 с выхода накопителя 3 записаны число 1 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 0 1. В регистр 20 запишется вычисленный формирователь 15 синдром 0 1 1 1. 1При записи в накопитель 3 инвертированного слова 0 0 0 0 0 0 1 1 1 1 0 1 0 0 0 0 0 1 1 0 с выходов 14 при контрольном считывании на схему 16 сравненйя поступит слово 1 1 1 1 О О 1 1 1 г О 1 О О О О О 1 1 О. Информация в первом блоке совпадает в схеме 16 сравнения с инФормацией, считываемой с регистра 10, так как элементы памяти в данной ИМП находятся постоянно в единичном состоянии. Тем самьвю на выходе одного иэ элементов И-НЕ 23 появится единичный сигнал, который откроет одни из элементов И 13. Тогда на сумматорах 18 произойдет суммирование синдрома из регистра 20 и .информации из искаженного блока, т.е, 0 1 1 1 + + 1 1 1 1 = 1 0 0 О, что соответствует исходной подлежащей хранению информации в этом блоке. Таким образом, предлагаемое устройство выполняет те же функции, что и известное, но более эффективно с точки зрения числа дополнительных вводимых контрольных разрядов и сложности кодирующих и декодирующих схем. Формула изобретения . Запоминающее устройство с исправлением ошибок, содержащее адресный блок, накопитель, блок записи, первый Й второй регистры числа, блок кодирования, схему сравнения, Формирователь проверочных сигналов, сумматоры по модулю два и элемент ИЛИ, причем входы накопителя подключены к выходам адресного блока и блока запи:и, одни,из входов которого и входы блока кодирования объединены и являются одними из входов устройства, а другие входы блока записи соединены соответственно с выходами блока кодированияи элемента ИЛИ и инверсными выходами первого регистра числа, прямые выходыкоторого подключены к одним из входов схемы сравнения и к первым входам сумматоров по.модулю два, выходынакопителя соединены с входами первого регистра числа, другими входамисхемы сравнения и входами Формирователя проверочных сигналов, выходы которого подключены к входам второгорегистра числа, вылоды которого соединены с входами элемента ИЛИ, о тл и ч а ю щ и е с я тем, что, сцелью повышения надежности устройства,оно содержит элементы И и элементыИ-НЕ, входы которых подключены к выходам схемы сравнения, а выходы со"единены с первыми входами элементовИ, вторые входы которых подключенык выходам второго .регистра числа,третьи входы - к выходу элементаИЛИ, а выходы элементов И соединеныс вторыми входами сумматоров по модулю два.Источники информации,принятые во внимание при экспертизе1. Вычислительная техника, Экспресс-информация, 1978, Р 36, с.5-11.2. Самофалов К. Г Корнейчук В.И.,Городний А. В. Структурно-логическиеметоды повышения надежности запоминающих устройств. М "Машиностроение",1976, с. 101-106 (прототип).Тираж 6 осударственн ам изобретен сква, Ж,2 Подпго комитетаСССРй и открытийаушская наб., д 4/

СмотретьЗаявка

3256760, 06.03.1981

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

КОНОПЕЛЬКО ВАЛЕРИЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 07.10.1982

Код ссылки

<a href="https://patents.su/4-964736-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Запоминающее устройство с самоконтролем

Случайный патент: Способ оценки надежности радиоэлектронных устройств