Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

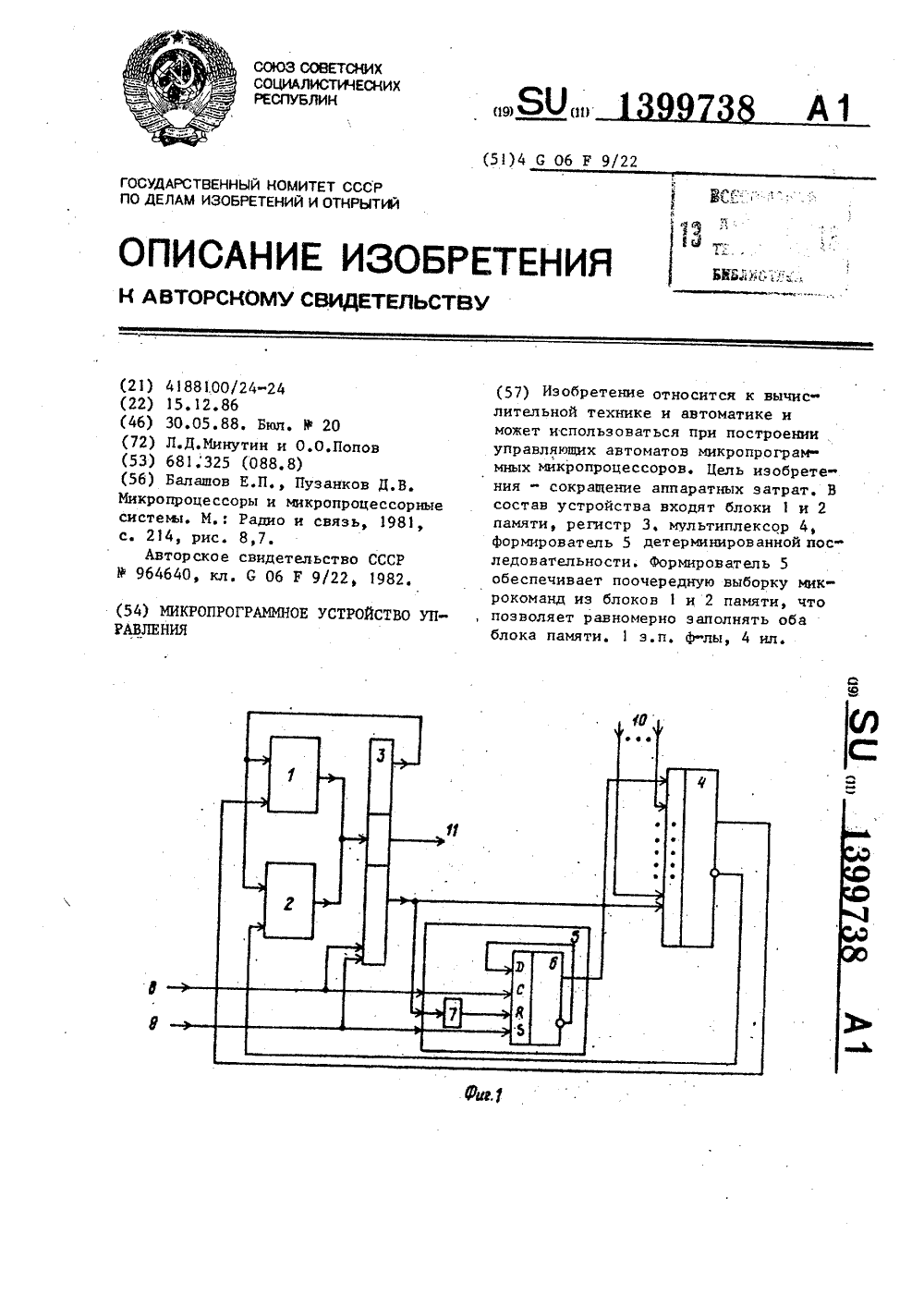

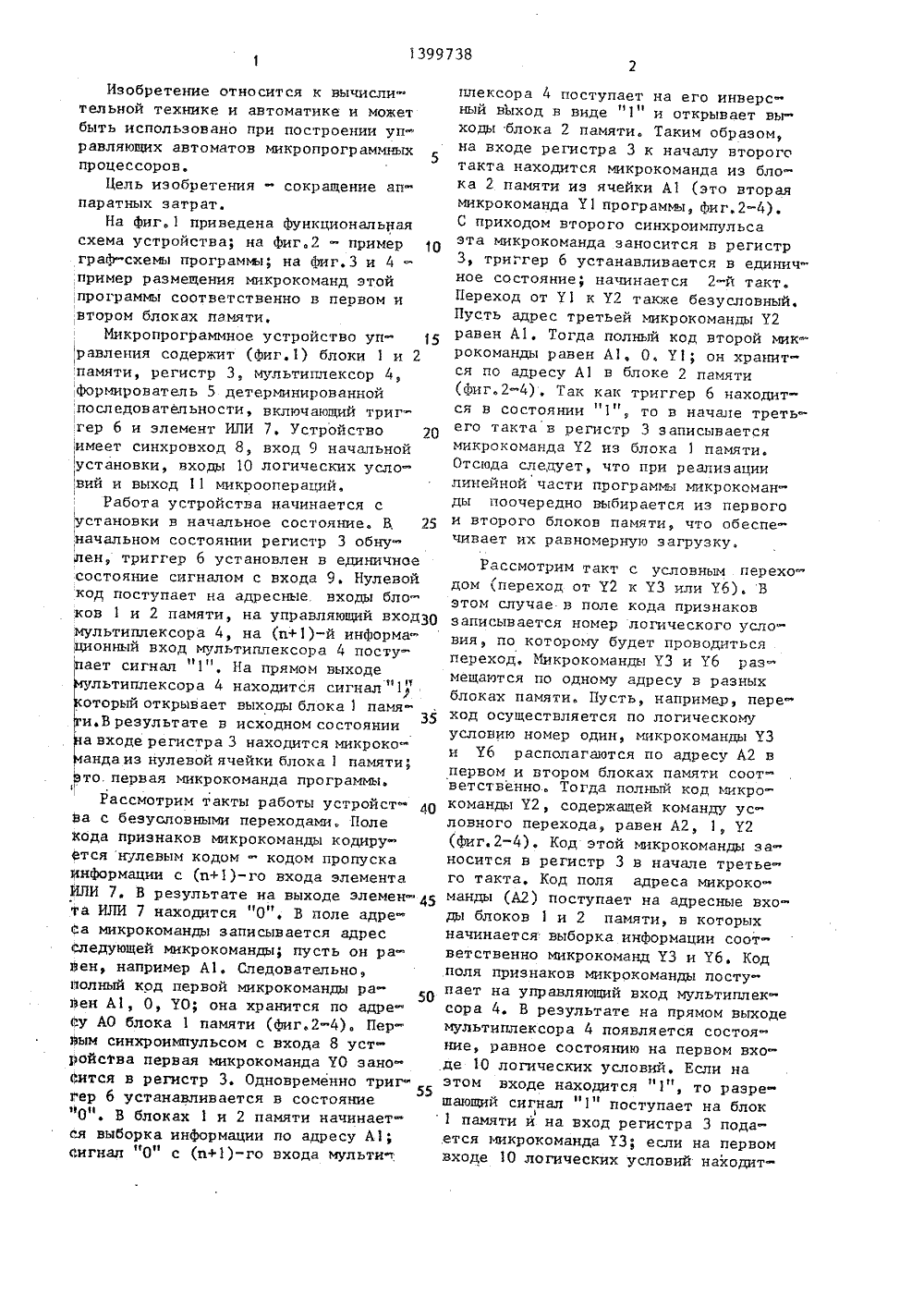

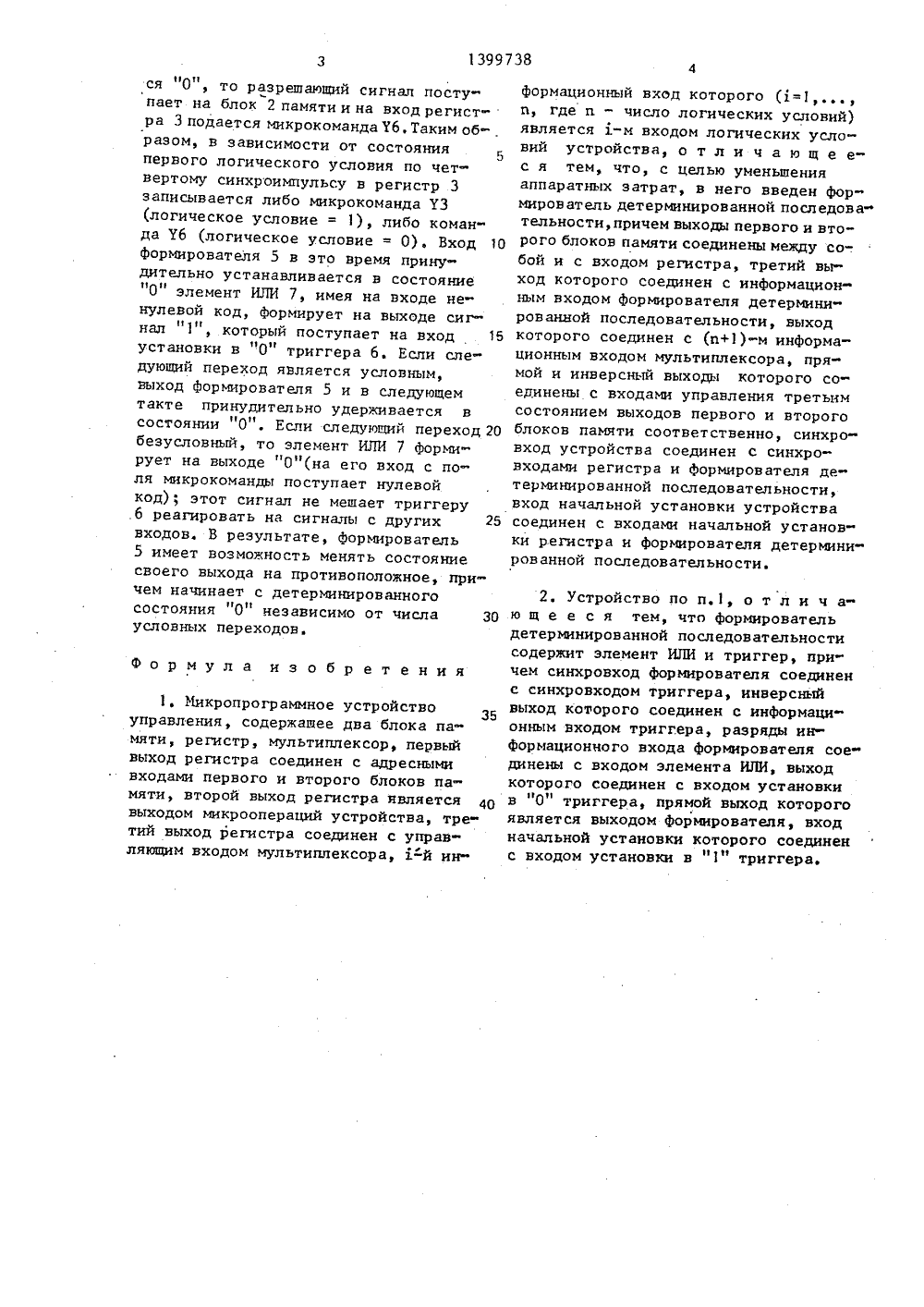

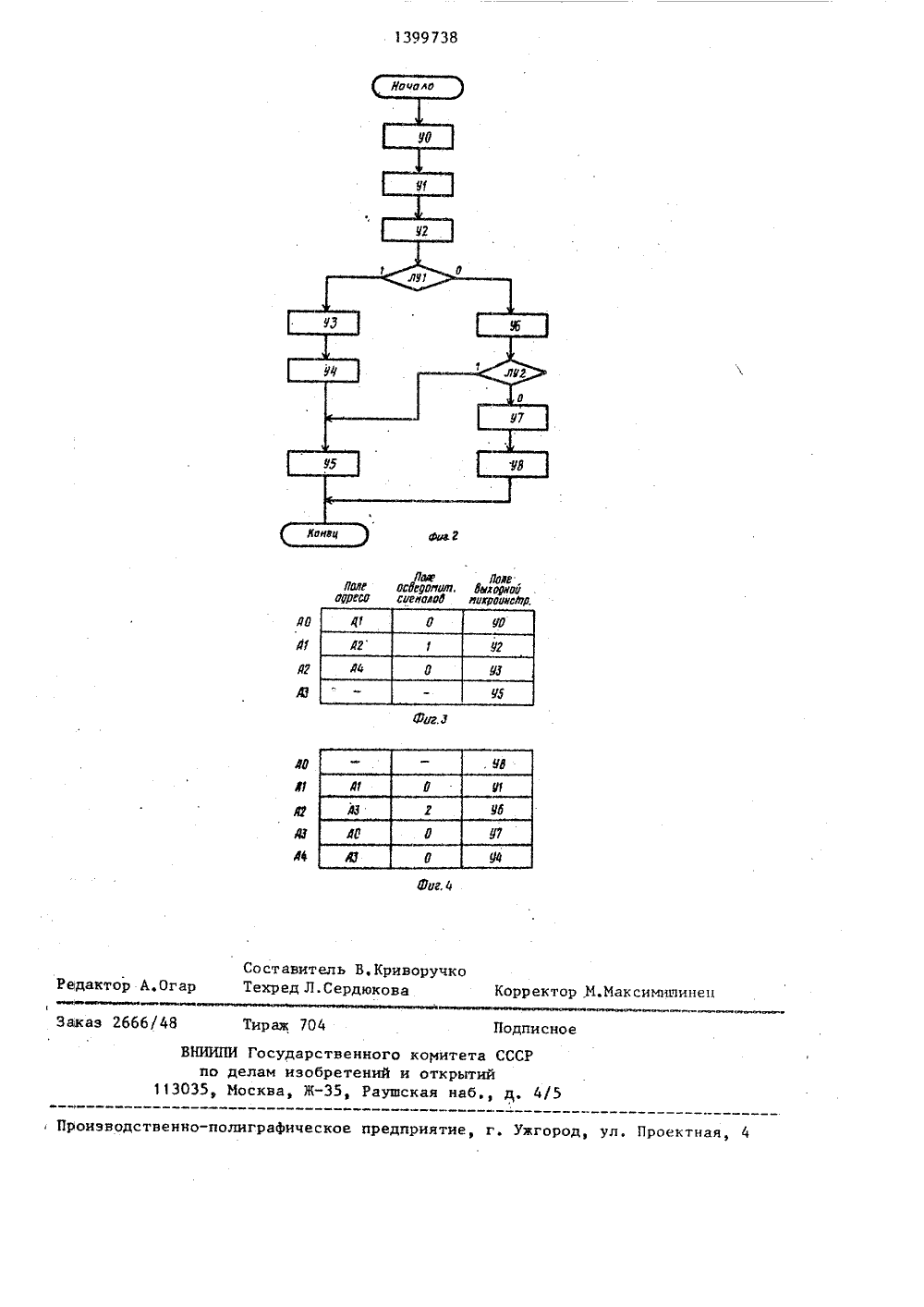

СООЗ СОВЕТСИИХСОЦИА ЛИСТИК ЕСНРЕСПУБЛИН 51)4 С Об Р ОПИСАНИЕ ИЗОБРЕТЕНН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ гаРЗ" с Г ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(57) Изобретение относится к вычислительной технике н автоматике и может использоваться при построении управляющих автоматов микропрограммных микропроцессоров. Цель изобретения - сокращение аппаратных затрат. В состав устройства входят блоки 1 и 2 памяти, регистр 3, мультиплексор 4, формирователь 5 детерминированной последовательности. Формирователь 5 обеспечивает поочередную выборку микрокоманд из блоков 1 н 2 памяти, что позволяет равномерно заполнять оба блока памяти. 1 з,п, ф-лы, 4 ил.Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении управляющих автоматов микропрограммных процессоров.Цель изобретения - сокращение аппаратных затрат.На Фиг.1 приведена функциональная схема устройства; на фиг.2 - пример 1 О граф-схемы программы; на Фиг.З и пример размещения микрокоманд этой программы соответственно в первом и втором блоках памяти.Микропрограммное устройство уп равления содержит (Фиг.1) блоки 1 и 2 памяти, регистр 3, мультиплексор 4, формирователь 5 детерминированной последовательности, включающий триггер 6 и элемечт ИЛИ 7, Устройство имеет синхровход 8, вход 9 начальной,установки входы 10 логических услоУ ,вий и выход 11 микроопераций.Работа устройства начинается с установки в начальное состояние. В. 25 начальном состоянии регистр 3 обнуден, триггер б установлен в единичное состояние сигналом с входа 9. Нулевой код поступает на адресные, входы бло" ков 1 и 2 памяти, на управляющий входЗО мультиплексора 4, на (и+1)-й информационный вход мультиплексора 4 поступает сигнал "1", На прямом выходельтиплексора 4 находится сигнал "1" оторый открывает выходы блока 1 памяи.В результате в исходном состоянии35 а входе регистра 3 находится микрокоандаиз нулевой ячейки блока 1 памяти; это. первая микрокоманда программы.Рассмотрим такты работы устройст 4 О Ьа с безусловными переходами, Поле Кода признаков микрокоманды кодируЕтся нулевым кодом - кодом пропуска йнформации с (и+1)-го входа элемента ЙЛИ 7. В результате на выходе элемен та ИЛИ 7 находится "О". В поле адреСа микрокоманды записывается адрес следующей микрокоманды; пусть он равен, например А 1. Следовательно,полный код первой микрокоманды равен А 1, О, 70; она хранится по адресу АО блока 1 памяти (Фиг.2-4), Первым синхроимпульсом с входа 8 устройства первая микрокоманда УО заноСится в регистр 3. Одновременно триг" гер б устанавливается в состояние "О". В блоках 1 и 2 памяти начинается выборка информации по адресу А 1; сигнал "О" с (и+1)-го входа мульти.т плексора 4 поступает на его инверсный вЫход в виде 1" и открывает выходы блока 2 памяти. Таким образом, на входе регистра 3 к началу второгс такта находится микрокоманда из блока 2 памяти из ячейки А 1 (это вторая микрокоманда 71 программы, Фиг.2-4). С приходом второго синхроимпульса зта микрокоманда заносится в регистр3, триггер 6 устанавливается в единичное состояние; начинается 2-й такт. Переход от 71 к У 2 также безусловный. Пусть адрес третьей мнкрокоманды 72равен А 1. Тогда полный код второй микрокоманды равен А 1, О, У 1; он хранится по адресу А 1 в блоке 2 памяти (Фиг,2-4), Так как триггер б находится в состоянии "1", то в начале третьего такта в регистр 3 записывается микрокоманда 72 из блока 1 памяти.Отсюда слецует, что при реализации линейной части программы микрокоманды поочередно выбирается из первого и второго блоков памяти, что обеспечивает их равномерную загрузку.Рассмотрим такт с условным переходом (переход от 72 к УЗ или Уб). Б этом случае в поле кода признаков записывается номер логического условия, по которому будет проводиться переход, Микрокоманды УЗ и Уб размещаются по одному адресу в разныхблоках памяти. Пусть, например, переход осуществляется по логическому условию номер один, микрокоманды УЗ и 76 располагаются по адресу А 2 в первом и втором блоках памяти соответственно. Тогда полный код микро- команды 72, содержащей команду условного перехода, равен А 2, 1, У 2 (Фиг.2-4), Код этой микрокоманды заносится в регистр 3 в начале третьего такта. Код поля адреса микрокоманды (А 2) поступает на адресные входы блоков 1 и 2 памяти, в которых начинается выборка информации соответственно микрокоманд УЗ и Уб, Код поля признаков микрокоманды поступает на управлянвций вход мультиплексора 4. В результате на прямом выходемультиплексора 4 появляется состояние, равное состоянию на первом входе 10 логических условий. Если на этом входе находится "1", то разрешающий сигнал "1" поступает на блок11 памяти и на вход регистра 3 подается микрокоманда 73; если на первом входе 10 логических условий находит 1399738ися О, то разрешающий сигнал поступает на блок 2 памяти и на входрегистра 3 подается микрокоманда 76. Таким об- . разом, в зависимости от состояния первого логического условия по четвертому синхроимпульсу в регистр 3 записывается либо микрокоманда УЗ (логическое условие = 1), либо команда Уб (логическое условие = 0). Вход 10 формирователя 5 в это время принудительно устанавливается в состояние 11 110 элемент ИЛИ 7 , имея на входе ненулевой код , формирует на выходе си г 11нал 1 , который поступает на вход 1 5 установки в " 0 " триггера бЕсли следующий переход является условным , выход фор мир ов ат ел я 5 и в следующем такте принудительно удерживается в состоянии " 0. Если следующий переход 20 безусловный, то элемент ИЛИ 7 формирует на выходе 0"(на его вход с поля микрокоманды поступает нулевой код); этот сигнал не мешает триггеру .б реагировать на сигналы с других 25 входов. В результате, формирователь 5 имеет возможность менять состояние своего выхода на противоположное, причем начинает с детерминированного состояния "0" независимо от числа 30 условных переходов.формула изобретения1. Микропрограммное устройство управления, содержащее два блока памяти, регистр, мультиплексор, первый выход регистра соединен с адресными входами первого и второго блоков памяти, второй выход регистра является 40 выходом микроопераций устройства, третий выход регистра соединен с управляющим входом мультиплексора, -й ин формационный вход которого (1=1и, где и - число логических условий)является -м входом логических условий устройства, о т л и ч а ю щ е ес я тем, что, с целью уменьшенияаппаратных затрат, в него введен формирователь детерминированной последовательности, причем выходы первого и второго блоков памяти соединены между со-.бой и с входом регистра, третий выход которого соединен с информационным входом формирователя детерминированной последовательности, выходкоторого соединен с (и+1)-м информационным входом мультиплексора, прямой и инверсный выходы которого соединены с входами управления третьимсостоянием выходов первого и второгоблоков памяти соответственно, синхровход устройства соединен с синхровходами регистра и формирователя детерминированной последовательности,вход начальной установки устройствасоединен с входами начальной установки регистра и формирователя детерминированной последовательности. 2Устройство по п.1, о т л и ч аю щ е е с я тем, что формирователь детерминированной последовательности содержит элемент ИЛИ и триггер, причем синхровход формирователя соединен с синхровходом триггера, инверсный выход которого соединен с информационным входом триггера, разряды информационного входа формирователя соединены с входом элемента ИЛИ, выход которого соединен с входом установки в "О" триггера, прямой выход которого является выходом формирователя, вход начальной установки которого соединен с входом установки в "1" триггера.1399 У 38 двг доле,йие осбедояап, оалооноцдреоо соеполоо тлооиаспр,Сост Техр итель В.КриворучкЛ.Сердюкова Редакт г ректор И,Максиминине Заказ 2 ббб/4 аж 704дарственног изобретенийЖ, Рауш Подписное Г комитета СССР открытий по 13035, а оск к наб ц. Проектная, 4 оизводственно-полиграфическое предприятие, г. Ужгоро

СмотретьЗаявка

4188100, 15.12.1986

ОПЫТНО-КОНСТРУКТОРСКОЕ ТЕХНОЛОГИЧЕСКОЕ БЮРО НОВГОРОДСКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

МИНУТИН ЛЕОНИД ДМИТРИЕВИЧ, ПОПОВ ОЛЕГ ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.05.1988

Код ссылки

<a href="https://patents.su/4-1399738-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Времяимпульсный умножитель

Следующий патент: Многоканальное устройство для обслуживания запросов

Случайный патент: 153654