Преобразователь двоичного кода в уплотненный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1365357

Автор: Сорокин

Текст

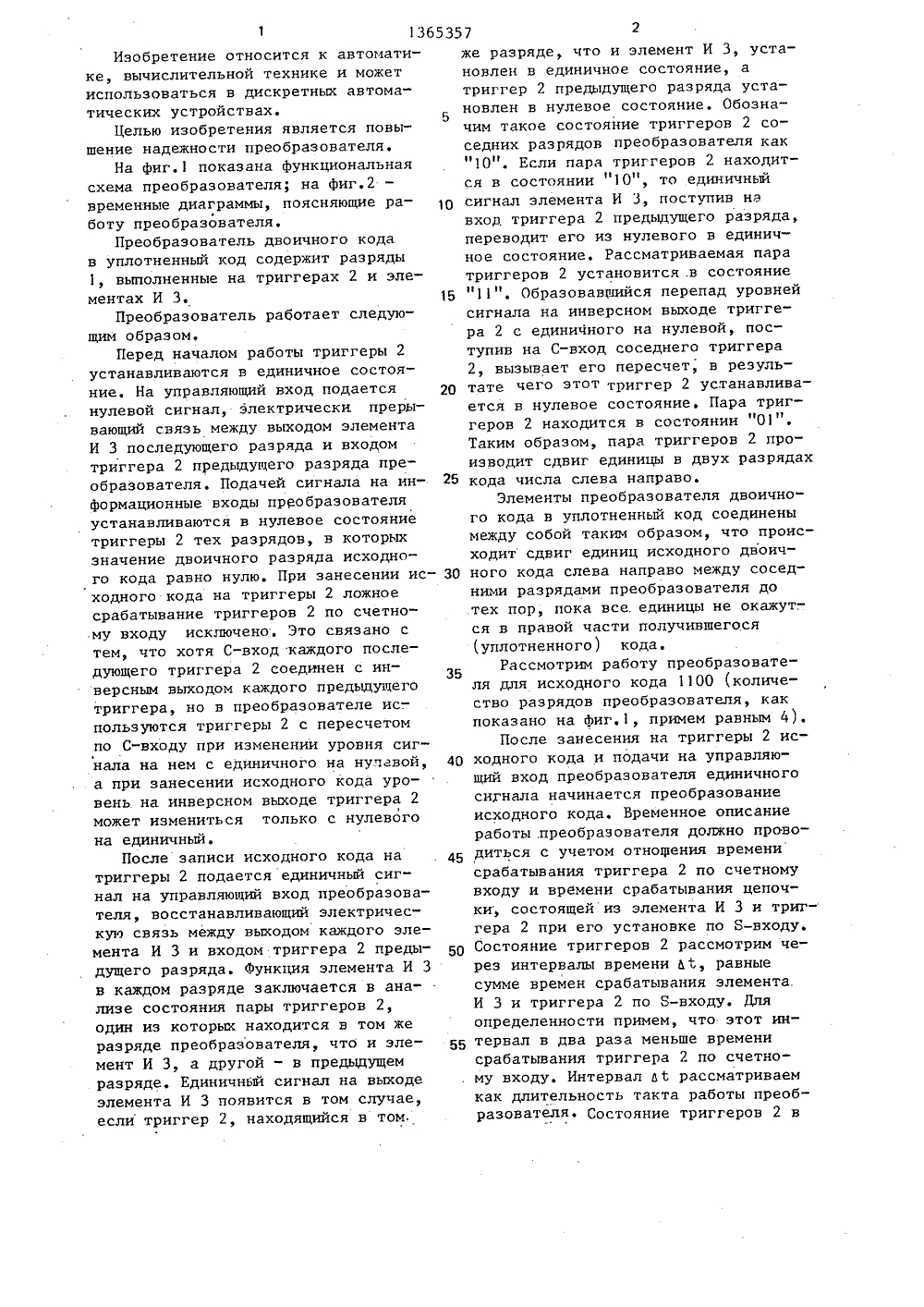

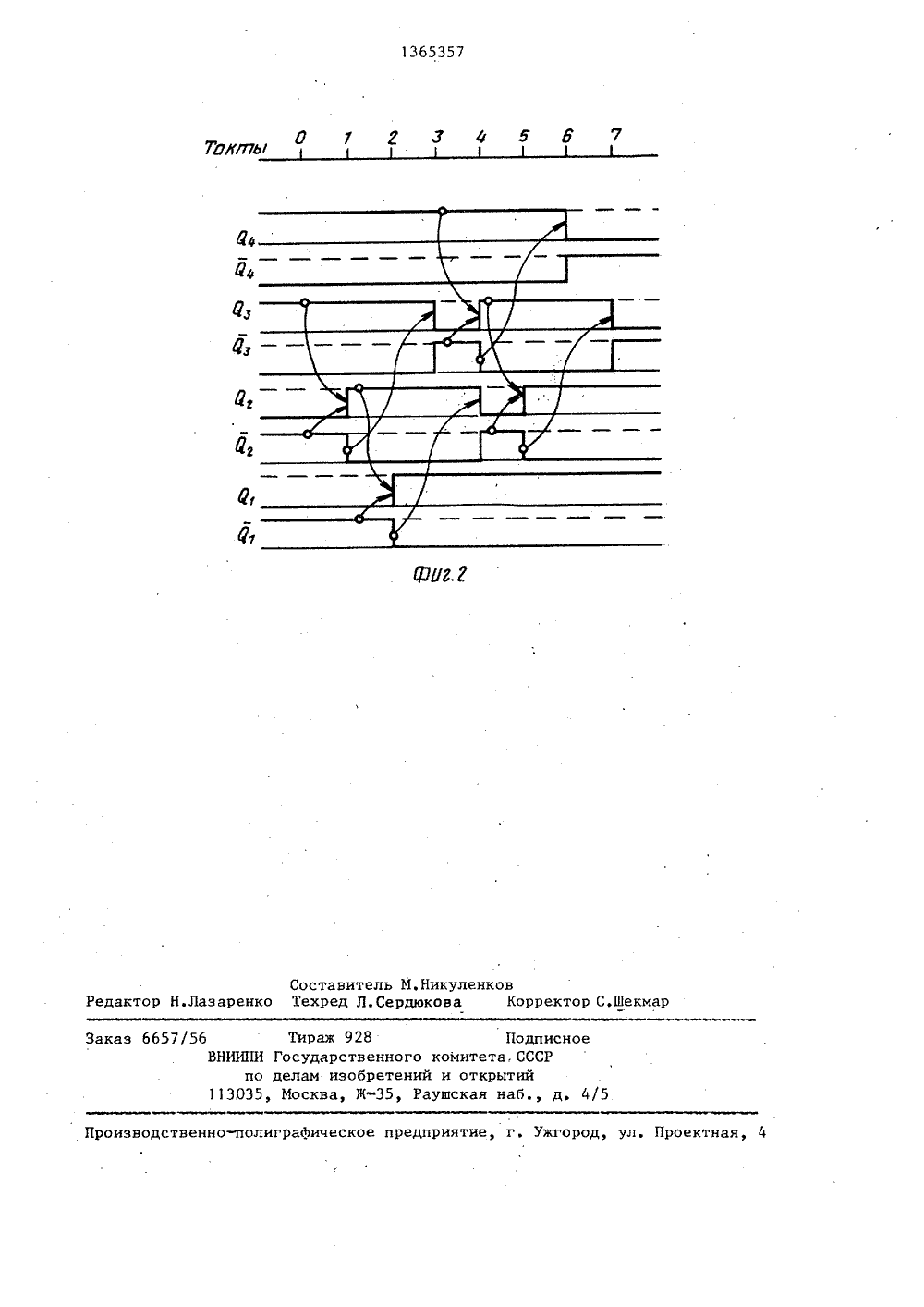

/О ОПИСАНИЕ ИЗОБРЕТЕНИЯ ТЕЛЬСТ АВТ РСНОМУ Бюл н8 8 тельство СССР7/30, 1973.льство СССРР 5/00, 198 сви 06е 0 2. ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДАВУПЛОТНЕННЫЙ КОД(57) Изобретение относится к вычислительной технике и дискретной автоматике. Цель изобретения - повышениенадежности преобразователя, Преобразователь изменяет произвольноерасположение нулей и единиц в исходном двоичном коде таким образом,что в правой части уплотненного двоичного кода находятся единицы, неразделенные нулями. Преобразовательдвоичного кода в уплотненный код содержит разряды 1,.выполненные натриггерах 2 и элементах И 3. 2 ил.65357 2же разряде, что и элемент И 3, установлен в единичное состояние, атриггер 2 предыдущего разряда установлен в нулевое состояние. Обозначим такое состояние триггеров 2 соседних разрядов преобразователя как"10". Если пара триггеров 2 находится в состоянии "10", то единичный10 сигнал элемента И 3, поступив навход триггера 2 предыдущего разряда,переводит его из нулевого в единичное состояние. Рассматриваемая паратриггеров 2 установится .в состояние15 "11". Образовавшийся перепад уровнейсигнала на инверсном выходе триггера 2 с единичного на нулевой, поступив на С-вход соседнего триггера2, вызывает его пересчет, в резуль 20 тате чего этот триггер 2 устанавливается в нулевое состояние. Пара триггеров 2 находится в состоянии "01",Таким образом, пара триггеров 2 производит сдвиг единицы в двух разрядах25 кода числа слева направо.Элементы преобразователя двоичного кода в уплотненный код соединенымежду собой таким образом, что происходит сдвиг единиц исходного двоич - 30 ного кода слева направо между соседними разрядами преобразователя дотех пор, пока все. единицы не окажут-.ся в правой части получившегося(уплотненного) кода.Рассмотрим работу преобразователя для исходного кода 1100 (количество разрядов преобразователя, какпоказано на фиг.1, примем равным 4),После занесения на триггеры 2 ис 40 45 50 55 1 13Изобретение относится к автоматике, вычислительной технике и может использоваться в дискретных автоматических устройствах.Целью изобретения является повышение надежности преобразователя.На фиг.1 показана функциональная схема преобразователя; на фиг.2 - временные диаграммы, поясняющие работу преобразователя.Преобразователь двоичного кода в уплотненный код содержит разряды 1, выполненные на триггерах 2 и элементах И 3.Преобразователь работает следующим образом.Перед началом работы триггеры 2 устанавливаются в единичное состояние, На управляющий вход подается нулевой сигнал, электрически прерывающий связь между выходом элемента И 3 последующего разряда и входом триггера 2 предыдущего разряда преобразователя. Подачей сигнала на информационные входы преобразователя устанавливаются в нулевое состояние триггеры 2 тех разрядов, в которых значение двоичного разряда исходного кода равно нулю. При занесении ис ходного кода на триггеры 2 ложное срабатывание триггеров 2 по счетному входу исключено. Это связано с тем, что хотя С-вход каждого последующего триггера 2 соединен с инверсным выходом каждого предыдущего триггера, но в преобразователе ис-. пользуются триггеры 2 с пересчетом по С-входу при изменении уровня сигнала на нем с единичного на нулевой, а при занесении исходного кода уровень на инверсном выходе триггера 21 может измениться только с нулевого на единичный.После записи исходного кода на триггеры 2 подаетсяединичный сигнал на управляющий вход преобразователя, восстанавливающий электрическую связь между выходом каждого элемента И 3 и входом триггера 2 предыдущего разряда. Функция элемента И 3 в каждом разряде заключается в анализе состояния пары триггеров 2, один из которых находится в том же разряде преобразователя, что и элемент И 3, а другой - в предыдущем разряде, Единичнь 1 й сигнал на выходе элемента И 3 появится в том случае, если триггер 2, находящийся в том,ходного кода и подачи на управляющий вход преобразователя единичногосигнала начинается преобразованиеисходного кода. Временное описаниеработы .преобразователя должно проводиться с учетом отношения временисрабатывания триггера 2 по счетномувходу и времени срабатывания цепочки, состоящей из элемента И 3 и триггера 2 при его установке по Б-входу.Состояние триггеров 2 рассмотрим через интервалы времени й 1, равныесумме времен срабатывания элемента.И 3 и триггера 2 по Б-входу. Дляопределенности примем, что этот интервал в два раза меньше временисрабатывания триггера 2 по счетному входу, Интервал ь 1 рассматриваемкак длительность такта работы преобразователя. Состояние триггеров 2 в65357 5 10 15 2025 30 35 3 130,17 такты, разделенные интервалом времени 1, приведено на временной диаграмме (фиг.2).В нулевом такте на управляющийвход преобразователя поступает единичный сигнал.Через один такт, необходимый длясрабатывания элемента И 3 третьегоразряда и триггера 2 второго разряда по Я-входу, триггер 2 устанавливается в единичное состояние (первый такт работы).Еще через один такт сигнал с единичного выхода триггера 2 второгоразряда и с инверсного выхода триггера 2 первого разряда, пройдя черезэлемент И 3 второго разряда, устанавливает триггер 2 первого разряда вединичное состояние (второй такт).Перепад уровней с инверсного выхода триггера 2 второго разряда,образовавшийся в первом такте, через два такта устанавливает триггер2 третьего разряда по С-входу в нулевое состояние (третий такт)В четвертом такте происходит изменение состояния двух триггеров 2.Сигналы с инверсного выхода триггера 2 третьего разряда и с прямоговыхода триггера 2 четвертого .разряда, пройдя через элемент И 3 четвертого разряда, устанавливают триггер 2 третьего разряда в единичноесостояние. Одновременно перепадуровней с инверсного выхода триггера 2 первого разряда, образовавшийсяво втором такте, вызывает пересчеттриггера 2 второго разряда по С-входу и устанавливает этот триггер 2 внулевое состояние.Установка триггера 2 третьегоразряда в единичное состояние и триггера 2 второго разряда в нулевоесостояние, происшедшая в четвертомтакте, вызывает появление единичного сигнала на выходе элемента И 3третьего разряда и установку триггера 2 второго разряда в единичноесостояние (пятый такт),Через два такта после установкитриггера 2 третьего разряда в единичное состояние (происшедшей в четвертом такте), происходит,по перепаду уровней с инверсного выхода этоготриггера 2, пересчет триггера 2 четвертого разряда по С-входу (шестойтакт). .Триггер 2 четвертого разряда устанавливается в нулевое состояние.Через два такта после установки триггера 2 второго разряда в единичное состояние (происшедшей в пятом такте) происходит по перепаду уровней с инверсного выхода этого триггера 2, пересчет триггера 2 третьего разряда по С-входу (седьмой такт). Триггер 2 третьего разряда устанавливается в нулевое состояние.На этом работа преобразователя заканчивается, так как на выходах элементов И 3 нет единичных сигналов и пересчет триггеров 2 по С-входу окончился. Исходный код 1100 преобразован в уплотненный код 0011. При других исходных кодах преобразователь работает аналогично.Необходимо отметить, что момент съема сигналов с выхода преобразователя кодов должен быть согласован с быстродействием элементов, входящих. в преобразователь, так как в период работы преобразователя на его выходах могут присутствовать различные комбинации нулей и единиц, не равные ни исходному, ни уплотненному коду. Формула изобретения Преобразователь двоичного кода вуплотненный код, содержащий в первомразряде триггер, прямой выход которого является выходом преобразователя, и в каждом разряде, кроме первого, триггер и элемент И, прямой выход триггера соединен с первым вхо 40 дом элемента И и является соответствующим выходом преобразователя, инверсный выход триггера каждого предыдущего разряда, кроме последнего,соединен с вторым входом элемента И45 каждого последующего разряда, о тл и ч а ю щ и й с я тем, что, с целью повышения надежности преобразователя, счетный вход триггера и выходэлемента И каждого последующего раз 50 ряда подключены соответственно к инверсному выходу и входу установки в1 и1 триггера каждого предыдущего разряда, входы установки в "0" триггеров разрядов являются информационны 55 ми входами преобразователя, третьивходы элементов И разрядов объединены и являются управляющим входом преобразователя,едакто ректор С.Шек каз 6657/56ВН 2 омит ии и от Раушска 113 оизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ТиражИИПИ Госудао делам5, Москв рственно изобрете а, Ж,Подписноеа, СССРытийнаб., д, 4

СмотретьЗаявка

4084844, 04.07.1986

ПРЕДПРИЯТИЕ ПЯ Р-6380

СОРОКИН СЕРГЕЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: двоичного, код, кода, уплотненный

Опубликовано: 07.01.1988

Код ссылки

<a href="https://patents.su/4-1365357-preobrazovatel-dvoichnogo-koda-v-uplotnennyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичного кода в уплотненный код</a>

Предыдущий патент: Преобразователь кода в период повторения импульсов

Следующий патент: Устройство для контроля кода ” из

Случайный патент: Приспособление для навивания товара на ткацком станке