Аналоговый фурье-процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

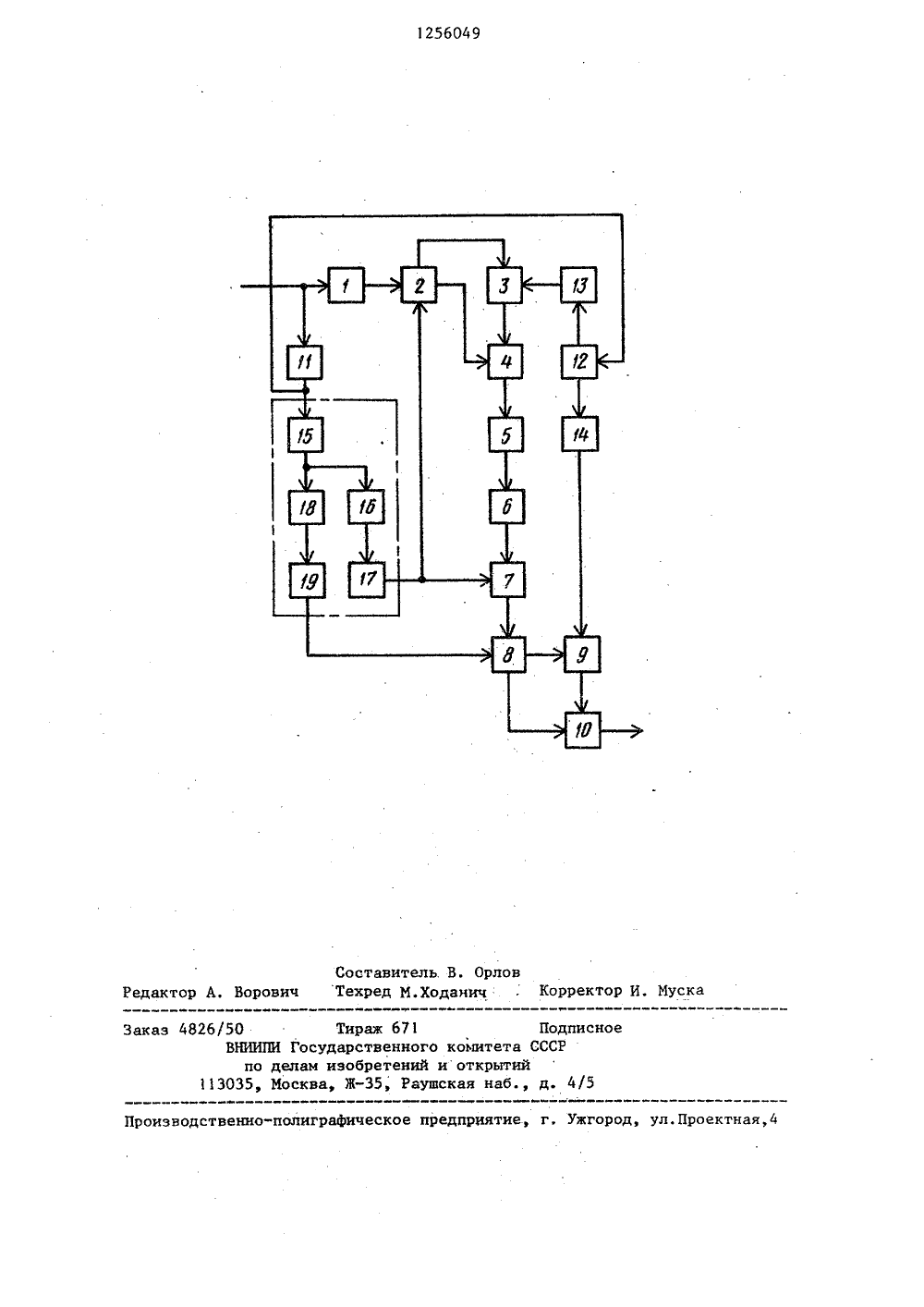

(59 ОПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Харьковский ордена ТрудовогоКрасного Знамени институт радиоэлроники им. акад. М.К, Янгеля(54) АНАЛОГОВЬ 1 И ФУРЬЕ-ПРОЦЕССОР (57) Изобретение относится к радиотехнике и предназначено для использования в радиолокаторах, системах т- связи, системах звуковой локации итд. Целью изобретения является расширение динамического диапазона процессора путем адаптивного изменения структуры процессора и коэффициента усиления. Цель достигается благодаря введению в процессор линии задержки, первого и второго коммутаторов, первого и второго сумматоров, регулируемого усилителя. 1 ил.Изобретение относится к аналоговой вычислительной технике и радиотехнике, в частности к устройствам ца поверхностных акустических волнах, и предназначено для использования в радиолокаторах, системах связи, системах звуковой .покации, системах управления воздушным движением и т.д.Целью изобретения является расширение динамического диапазона процессора за счет адаптивного изменения структуры процессора и коэффициентаусиления.На чертеже представлена структурная схема аналогового Фурье-процессора.Аналоговый Фурье-процессор содержит элемент 1 задержки, первый коммутатор 2, первый перемножитель 3, первый сумматор 4, усилитель 5, Фильтр 6 свертки линейно в частот-модулированного сигнала, регулируемый усилитель 7, второй коммутатор 8, второй перемножитель 9, второй сумматор 10, детектор 11, синхронизатор 12, первый генератор 1 Э линейно- частотно-модулированного сигнала, второй генератор 14 линейно-частотно-модулированного сигнала,. Формирователь 15 импульсов, первый интегратор 16, первый компаратор 17, второй интегратор 18 и второй компаратор 19.Аналоговый Фурье-процессор работает следующим образом.3 исходном состоянии входной импульсный сигнал с полосой М, и переменной длительностью Т,ТТ через элемент 1 задержки и коммутатор 2 поступает ца вход первого перемножителя 3, Далее входной сигнал преобразуется. Одновременно входной радио- импульс поступает на детектор 11, ца выходе которого формируется сигнал, передним Фронтом которого запускается синхронизатор 12.Режим 1 реализуется при длительиосги входного сигнаиа Т, х а Т 1 и Продетектированный входной сигнал с выхода детектора 11 поступает на вход формирователя 15 импульсов, который формирует из входных видеоимпульсов с большим диапазоном изменения амплитуды выходной сигнал в виде прямоугольных импульсов постоянной амплитуды, длительность которых равна длительности входного сигнала, измеренной по заданному уровню,С выхода формирователя 15 импульсов прямоугольные импульсы для принятия решения о их длительности подаются на последовательно соединенные5 первый интегратор 16 и первый компаратор 17 и на последовательно соеди -ненные второй интегратор 18 и второйкомпаратор 19. После интеграторов 16и 18 прямоугольные импульсы преобразуются в линейно растущие напряжения,амплитуды которых пропорциональныдлительностям входных прямоугольныхимпульсов. Б компараторах 17 и 19 1применяются фиксированные опорныенапряжения. Для принятия решения одлительности входного сигнала постоянная времени первого интегратора 16выбирается отличной от постояннойвремени второго интегратора 18 вТ 11 Т рав.В первом режиме на выходе первогокомпаратора 17 вырабатывается управляющий сигнал, который открывает первый и закрывает второй выходы первого компаратора 2, а также переводитрегулируемый усилитель 7 в состояниемаксимального усиления с коэффициентом К , Управляющий сигнал на выходеС 1второго компаратора 19 производит пеЗ 0 реключение выходов второго коммутатора 8.Режим 11. При 1 еТ /1, Т,ГТ,/Мна выходе первого интегратора 16 линейно растущее напряжениеЗ 5 превышает опорное напряжение первогокомпаратора 17, на выходе которогоизменяется управляющий сигнал, чтоприводит к закрытию одного и открытию другого выходов коммутатора 2, а40 также к переводу регулируемого усилителя 7 в состояние с коэффициентомусиления К., Разница коэФфициентовусиления в режимах 1 и 11 составляет20 1 дД ТР да.45, На выходе второго интегратора 18из-за его большой постоянной времениинтегрирования линейно растущее напряжение не достигает уровня опорного напряжения второго компаратора 19,управляющий сигнал на выходе которо -го остается таким же, как и для ре -жима Режим 111. ПРи Т с 11 -ТТ ТР,Т управляющий сигнал ца выходе первого компаратора 17 останется таким же, как и для режима 11, а ца выходе второго компаратора 19 он изменяется, так как линейно растущее напряжениеты его сигнала,формула изобретения15 Аналоговый урье-процессор, содержащий первый и второй перемножители, первый и второй генераторы линейночастотно-модулированного сигнала, усилитель, фильтр свертки линейно- частотно-модулированного сигнала и синхронизатор, причем первый выход синхронизатора через первый генератор линейно-частотно-модулированного сигнала соединен с первым входом первого перемножителя, второй выход синхронизатора через второй генератор линейно-частотно-модулированно 20 го сигнала соединен с первым входомвторого перемножителя, а выход усилителя соединен с входом фильтрасвертки линейно-частотно-модулированного сигнала, о т л и ч а ю щ и йс я тем, что, с целью расширения динамического диапазона путем адаптивного изменения структуры и коэффициента усиления, в него введены элемент задержки, детектор, первый ивторой коммутаторы, первый и второйсумматоры, регулируемый усилитель,40 на выходе второго интегратора 18 превышает опорное напряжение второгокомпаратора 19. Это приводит к тому,что один из выходов второго коммутатора 8 открывается, а другой закрывается, и преобразованный сигнал с выхода ЛЧМ фильтра 6 свертки поступаетна второй сумматор 10, минуя второйперемножитель 9, Аналогично режиму 1исключение второго ЛЧМ генератора 14 1 Овозможно из-за малой девиации часто-. формирователь импульсов, первый ивторой интеграторы, первый и второйкомпараторы, причем вход детекторасоединен с входом элемента задержкии является входом процессора, выходэлемента задержки подключен к информационному входу первого коммутатора,первый выход которого соединен с вторым входом первого перемножителя,второй выход первого коммутаторас первым входом первого сумматора,второй вход которого соединен с выходом первого перемножителя, выходпервого сумматора - с входом усилителя, выход фильтра свертки линейно-частотно-модулированного сиг.нала соединен с информационным входом регулируемого усилителя, входуправления усилением которого соединен с выходом первого компаратора и управляющим входом первого коммутатора, выход второго компараторасоединен с управляющим входом второго коммутатора, информационный входкоторого соединен с выходом регулируемого усилителя, первый вьгхвд второго коммутатора соединен с вторымвходом второго перемножителя, второйвыход второго коммутатора - с первым входом второго сумматора, второйвход которого соединен с выходом второго перемножителя, выход детекторасоединен с входом запуска синхронизатора и входом формирователя импульсов, выход которого соединен с входами первого и второго интеграторов,выходы которых соединены с входамиодноименных компараторов, выход второго сумматора является выходом процессора,1256049 6/50 Тираж 6ВНИИПИ Государственпо делам изобрете 13035 Москвау ж,Заказ 4 71 Подписноного комитета СССРний и открытийРаушская наб. 5 д. 4/ играФическое предприятие, г, Ужг роизводственн ул.Проектная,4 Составитель. В. ОрловРедактор А. Ворович Техред М.Ходанич , Корректор И. Муск

СмотретьЗаявка

3875067, 26.03.1985

ХАРЬКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ РАДИОЭЛЕКТРОНИКИ ИМ. АКАД. М. К. ЯНГЕЛЯ

СОБОЛЬ НИКОЛАЙ ВАЛЕНТИНОВИЧ, ДОЛБНЯ ЕВГЕНИЙ ВЛАДИМИРОВИЧ, ЛИСИН АРКАДИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06G 7/19

Метки: аналоговый, фурье-процессор

Опубликовано: 07.09.1986

Код ссылки

<a href="https://patents.su/4-1256049-analogovyjj-fure-processor.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый фурье-процессор</a>

Предыдущий патент: Аналоговый интегратор

Следующий патент: Устройство для определения квадратурных составляющих гармонического сигнала

Случайный патент: 277179