Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

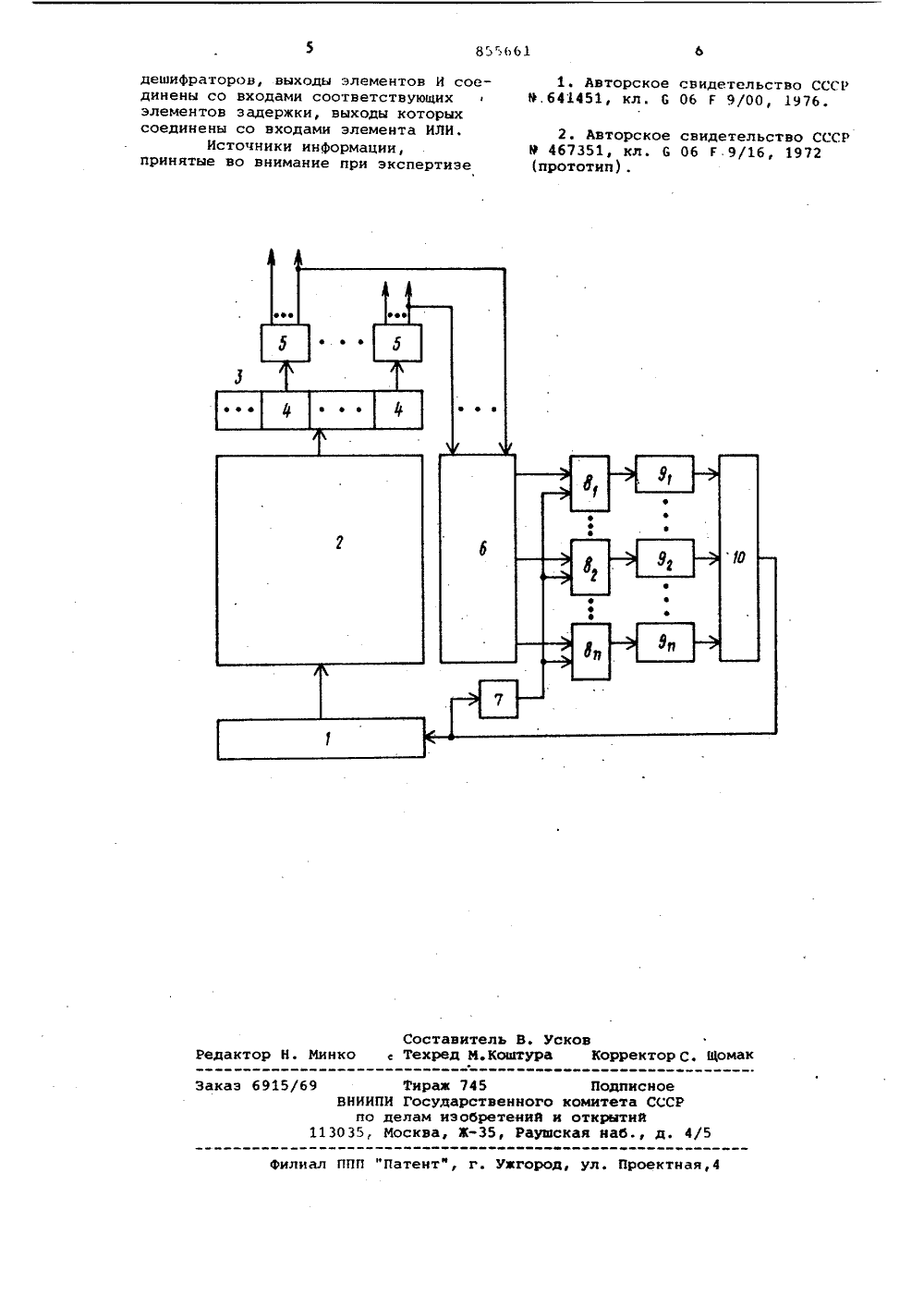

Союз Советских Соцналйстических РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ нц 855661(22) Заявлено 19, 11. 79 (21) 2842132/18-24с присоединением заявки Йо(51)М. К . С 06 Г 9/22 Государственный комитет СССР но делам изобретений и открытий(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике, в частности к устройствам управления цифровых вычислительных машин.Для повышения быстродействия цифровых вычислительных машин, использующих микропрограммный принцип управления, применяются устройства управления с переменной длительностью . такта. При этом длительность К-го такта, си),где с - длительность (-й микрооперации, выполняемой в К-м такте,Известно устройство управления,содержащее блок памяти, блок формирования выходных сигналов, блок формирования сигналов возбуждения памяти,блок формирования кодов временных интервалов, управляемый генератор импульсов 1(.Недостаток устройства - низкоебыстродействие,Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее адресный регистр, блок памяти микропрограмм, регистр микрокоманд, дешифраторы, блок управления длительностью микГ зпрограммного такта, секционная линия задержки задания длительности такта,элемент НЕ 2.Однако данное устройство формирует наборы управляющих сигналовс различной длительностью. При этомблок управления устройства переключается на выполнение следующего тактапосле выполнения самого "длинного"такта, используемого для управлениясамым медленным узлом ЦВМ, причемэто переключение прОизводится в мо мент времени, когда на всех выходахлинии задержки присутствуют одинаковые уровни, например, сигналом с последнего выхода линии задержки. Этозначительно снижает быстродействие 20 устройства.Цель изобретения - повышение быстродействия.Поставленная цель достигается тем,что в устройство, содержащее дешифраторы, регистр микрокоманд, блок памяти микропрограмм, регистр адреса иэлемент НЕ, вход которого соединенсо входом синхронизации регистра адреса, информационный выход которого 30 соединен с адресным входом блока па 85. ЬЬ 140 45 56 55 60 б 5 миги микропрограмм, информационный выход которого соединен с информационным входом регистра микрокоманд, информационные выходы групп разрядов которого соединены со входами соответствующих дешифраторов, выходы которых являются управляющими, выходами устройства, введены блок приоритета, элементы И, элементы задержки и элемент ИЛИ, выход которого соединен со входом элемента НЕ, выход которого соединен с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами блока приоритета, в:оды которого соединены с соответствующими выходами дешифраторов, выходы элементов И соединены со входами соответствующих элементов задержки, выходы которых соединены со входами элемента ИЛИ.На чертеже представлена схема микропрограммного устройства управления.Устройство содержит регистр 1 адреса, блок 2 памяти микропрограмм, регистр 3 микрокоманд с полями 4 управления блоками, время цикла которых больше длительности обычного такта, дешифраторы 5 этих полей, блок б приоритета, элемент 7 НЕ, элементы 8 И, элементы 9 -9 и задержки, время задержки которых соответственно Т, - ГИ элемент 10 ИЛИ. Регистр 1 подключен к блоку 2. С помощью регистра 1 осуществляется модификация адреса микрокоманд в процессе выполнения микропрограммы.Из блока 2 в соответствии с адресом, формируемым регистром 1, информация считывается в регистр 3. Считывание информации из блока 2 в регистр 3 осуществляется задним фронтом синхросигнала с выхода элемента 10 ИЛИ в конце микропрограммноготакта.Поля 4 регистра 3 дешифрируются дешифраторами 5, и сформированные сигналы микроопераций поступают на выход устройства, а та их часть которая управляет работой "медленных" узлов ЦВМ, - на вход блока б, который формирует в результате на одном из своих выходов уровень логической и 1". Возбужденный выход соответствует самой длительной микрооперации, из числа выполняемых в данном такте.Устройство работает следующим образом. В начале каждого такта на выходах дешифраторов 5 подготовлены сигналы микроопераций и сигналы, управляющие работой блока Ь. Блок б осуществляет анализ состояний выходов дешифраторов микроопераций и на выходе, соответствующем самой длительной микро- операции, выполняемой в текущем такте формирует уровень логической "1".Этот уровень открывает соответствующий элемент 8 и разрешает прохождение сигнала логической "1" с выхода эле 5 10 15 20 25 30 35 мента 7 на вход элемента 9 1 Спустя промежуток времени ; этот сигнал через элемент 10 поступает на вход элемента 7 и меняет состояние его выхода на противоположное. Сформированный сигнал логического "0" задерживается элементом 9 и через элемент 10 поступает на синхровход регистра 1, 9 и через элемент 10 поступает на синхровход регистра 1, изменяя его состояние, Тем самым с помощью элемента 9, элемента 10, элемента 7 и элемента 8 формируется очередной микропрограммный такт длительность Т = 2 Г, где Е. - время задержки элемента 9. Переход регистра 1 в новое состояние вызывает считывание очередной микрокоманды на регистр 3 и формирование нового набора сигналов микроопераций, Если при этом не будет возбужден ни один из выходов дешифраторов 5, что соответствует такту с минимальной длительностью Т, то уровень логической "1" установится на первом выходе блока б и с помощью элемента 8, элемента 9 элемента 10 и элемента 7 сформирован такт длительностью То.Таким образом, в отличие.от известного устройства, где переход к новому такту происходит после окончания самого "длительного" так"а и после срабатывания всей линии задержки данное устройство позволяет перейти к выполнению очередного такта сразу после окончания самого "длинного" из предыдущих тактов и таким образом имеет более высокое быстродействие. Формула изобретения Микропрограммное устройство управления, содержащее дешифраторы, регистр микрокоманд, блок памяти микропрограмм, регистр адреса и элемент НЕ, вход которого соединен со входом синхронизации регистра адреса, информационный выход которого соЕдинен с адресным входом блока памяти микропрограмм, информационный выход которого соединен с информационным входом регистра микрокоманд, информационные выходы групп разрядов которого соединены со входами соответствующих дешифраторов, выходы которых являются управляющими выходами устройства, о т л и ч а ю щ ее с я тем, что, с целью увеличения быстродействия, в него введены блок приоритета, элементы И, элементы задержки и элемент ИЛИ, выход которого соединен со входом элемента НЕ, выход которого соединен с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами блока приоритета, входы которого соединены с соответствующими выходами85") 661 дешифраторон, выходы элементов И соединены со входами соответствующих элементов задержки, выходы которых соединены со входами элемента ИЛИ.Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР9.641451, кл. С 06 Г 9/00, 1976. 2. Авторское свидетельство СССР9 467351, кл, 6 06 Г 9/16, 1972(прототип) . оставительехред М.Кош Ускова Корректор С, Щ едакто нко 745арственного кэобретений и Ж, Раущск Заказ 6915 5 иал ППП "Патент", г. Ужгород, ул. Проектная,4 Фир ВНИИПИ Гос по делам 13035, Москв

СмотретьЗаявка

2842132, 19.11.1979

ВОЙСКОВАЯ ЧАСТЬ 44388-РП

ГИНАК ГЕОРГИЙ ИОСИФОВИЧ, ПАНОВ ЮРИЙ МИХАЙЛОВИЧ, ПАСЬКО АЛЕКСАНДР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.08.1981

Код ссылки

<a href="https://patents.su/3-855661-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для управления обменом

Следующий патент: Устройство микропрограммного управления

Случайный патент: Устройство сложения мощностей генераторов электрических колебаний