Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

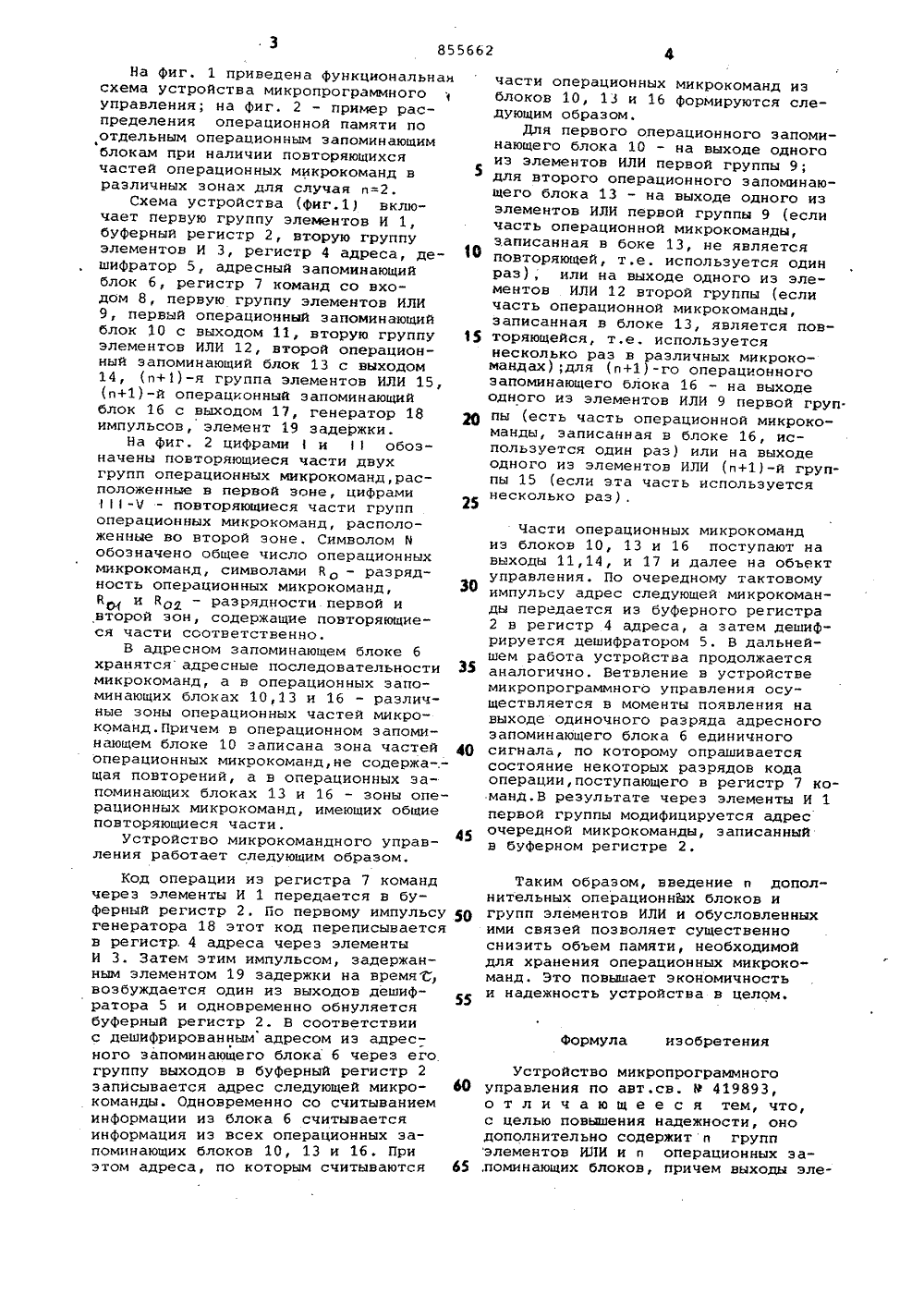

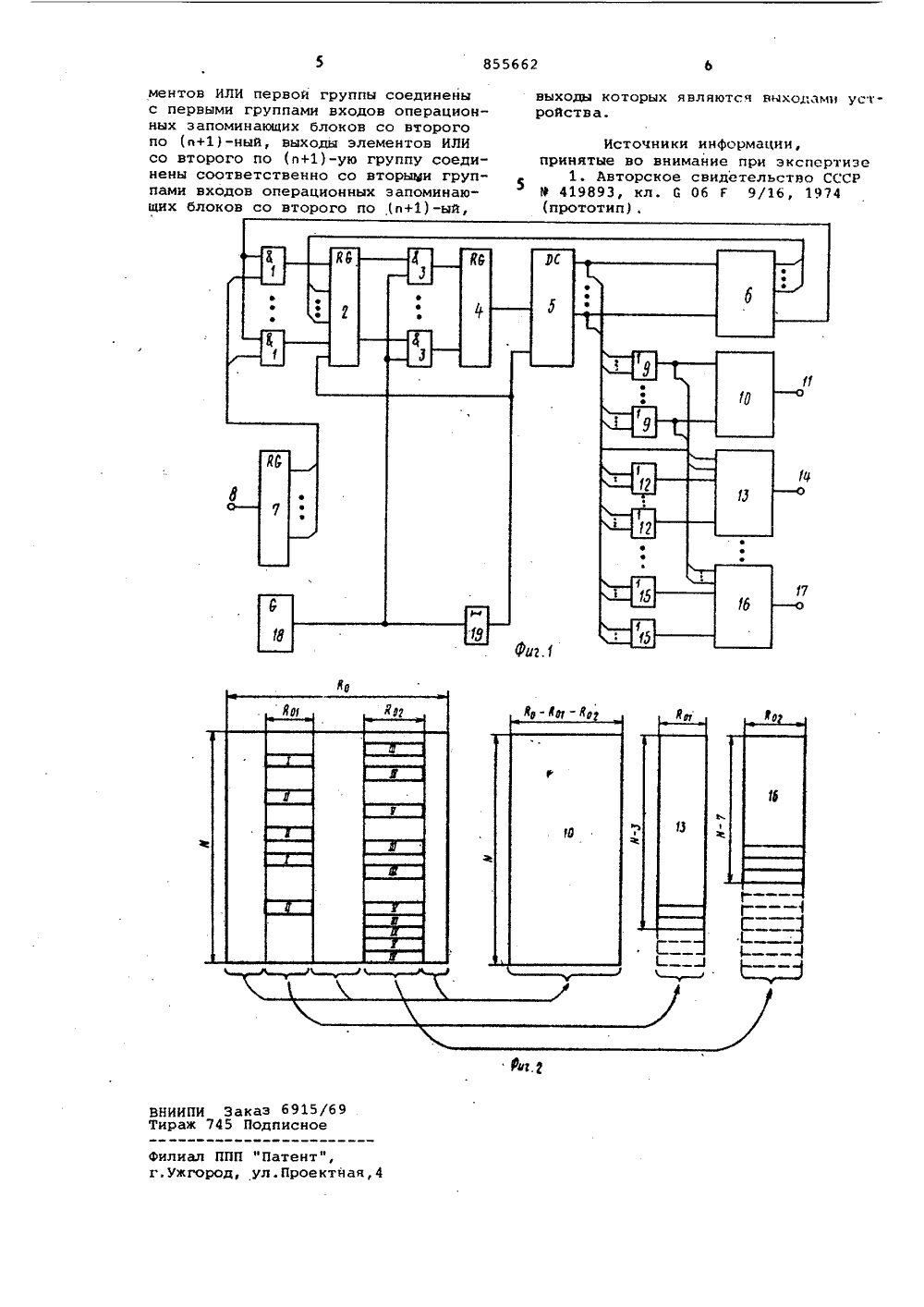

Союз Советских Социалистических РеслубликОПИСАНИЕ ИЗОБРЕТЕНИЯ ВТОРСКОМУ СВИДЕТЕЛЬСТВ(23) Приоритет 1)М. Кл. С 06 Г 9 Государственный комнте СССР по делам изобретений и открытийпубликовано 150881, Бюллетень Й 9 30 681.325 (088.8) та опубликования описания 1508. 81) УСТРОИСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯИзобретение относится к автоматике и вычислительной технике, можетбыть применено при проектированииустройств управления микропрограммных ЭВМ,По основному авт.св, У 419893известно устройство микропрограммного управления, содержащее адресныйзапоминающий блок, операционный запоминающий блок, буферный регистр,регистр адреса, регистр команд, дешифратор, генератор импульсов, двегруппы элементов И, группу элементовИЛИ и элемент задержки 11.т 5 Недостатком данного устройства является низкая экономичность, выз" ванная избыточностью операционного запоминающего блока. Избыточность информации, хранимой в операционном 20 запоминающем блоке, обусловленаследующим. В этом блоке хранятся операционные микрокоманды, которые считываются в соответствии с адресами, поступающими из адресного запоми нающего блока. Операционный запоминающий блок оптимизирован по числу операционных микрокоманд, которые записаны в нем без повторений. Одна" хо при этом не учитывается возмож ность повторения отдельных частей различных операционных микрокоманд.Цель изобретения - повышение надежности, а также повышение экономичности устройства за счет снижения сложности операционного запоминающего блока.Поставленная цель достигается тем, что устройство микропрограммного управления дополнительно содержит н групп элементов ИЛИ и и операционных запоминающих блоков, причем выходы элементов ИЛИ первой группы соединены с первыми группами входов операционных запоминающих блоков со второго по (и+1)-ый и выходы элементов ИЛИ со второго по (и+1)-ую группы соединены соответственно со вторыми группами входов операционных запоминающих блоков со второго по (и+1)-ый, выходы которых являются выходами устройства.Сущность изобретения состоит в снижении объема памяти, необходимого для хранения операционных микрокоманд путем однократной записи их повторяющихся частей, содержащихся в одной зоне. При этом под зоной понимается часть операционного запоминающегоблока шиной ко(но855662 5 36 15 20 25 30 35 40 45 50 55 На фиг. 1 приведена функциональнаясхема устройства микропрограммногоуправления; на фиг. 2 - пример распределения операционной памяти поотдельным операционным запоминающимблокам при наличии повторяющихсячастей операционных микрокоманд вразличных зонах для случая п=2.Схема устройства (фиг.1) включает первую группу элементов И 1,буферный регистр 2, вторую группуэлементов И 3, регистр 4 адреса, дешифратор 5, адресный запоминающийблок 6, регистр 7 команд со входом 8, первую группу элементов ИЛИ9, первый операционный запоминающийблок 10 с выходом 11, вторую группуэлементов ИЛИ 12, второй операционный запоминающий блок 13 с выходом14, (и+-я группа элементов ИЛИ 15,(и+1)-й операционный запоминающийблок 16 с выходом 17, генератор 18импульсов, элемент 19 задержки.На фиг, 2 цифрамииобозначены повторяющиеся части двухгрупп операционных микрокоманд,расположенные в первой зоне, цифрами1)-Ч - повторяющиеся части группоперационных микрокоманд, расположенные во второй зоне, Символом йобозначено общее число операционныхмикрокоманд, символами йо - разрядность операционных микрокоманд,й и йо - разрядности первой ивторой зон, содержащие повторяющиеся части соответственно,В адресном запоминающем блоке 6хранятся адресные последовательностимикрокоманд, а в операционных запоминающих блоках 10,13 и 16 - различные зоны операционных частей микрокоманд. Причем в операционном запоминающем блоке 10 записана зона частейоперационных микрокоманд,не содержа-. -щая повторений, а в операционных запоминающих блоках 13 и 16 - зоны операционных микрокоманд, имеющих общиеповторяющиеся части.Устройство микрокомандного управления работает следующим образом,Код операции из регистра 7 команд через элементы И 1 передается в буферный регистр 2, По первому импульсу генератора 18 этот код переписывается в регистр. 4 адреса через элементы И 3. Затем этим импульсом, задержанным элементом 19 задержки на времяС, возбуждается один из выходов дешифратора 5 и одновременно обнуляется буферный регистр 2. В соответствии с дешифрированным адресом из адресного запоминающего блока 6 через его группу выходов в буферный регистр 2 записывается адрес следующей микро- команды. Одновременно со считыванием информации из блока 6 считывается информация из всех операционных запоминающих блоков 10, 13 и 16. При этом адреса, по которым считываются части операционных микрокоманд изблоков 10, 13 и 16 формируются следующим образом.Для первого операционного запоминающего блока 10 - на выходе одногоиз элементов ИЛИ первой группы 9;для второго операционного запоминающего блока 13 - на выходе одного изэлементов ИЛИ первой группы 9 (есличасть операционной микрокоманды,записанная в боке 13, не являетсяповторяющей, т.е. используется одинраз), или на выходе одного из элементов ИЛИ 12 второй группы (есличасть операционной микрокоманды,записанная в блоке 13, является повторяющейся, т.е. используетсянесколько раз в различных микрокомандах);для (и+1)-го операционногозапоминающего блока 16 - на выходеодного из элементов ИЛИ 9 первой груп.пы (есть часть операционной микроко"манды, записанная в блоке 16, используется один раз) или на выходеодного из элементов ИЛИ (и+1)-й группы 15 (если эта часть используетсянесколько раз),Части операционных микрокоманд из блоков 10, 13 и 16 поступают на выходы 11,14, и 17 и далее на объект управления. По очередному тактовому импульсу адрес следующей микрокоманды передается из буферного регистра 2 в регистр 4 адреса, а затем дешифрируется дешифратором 5. В дальнейшем работа устройства продолжается аналогично, Ветвление в устройстве микропрограммного управления осуществляется в моменты появления на выходе одиночного разряда адресного запоминающего блока 6 единичного сигнала, по которому опрашивается состояние некоторых разрядов кода операции, поступающего в регистр 7 команд .В результате через элементы И 1 первой группы модифицируется адрес очередной микрокоманды, записанный в буферном регистре 2. Таким образом, введение и дополнительных операционнйх блоков и групп элементов ИЛИ и обусловленных ими связей позволяет существенно снизить объем памяти, необходимой для хранения операционных микрокоманд. Это повышает экономичность и надежность устройства в целом. Формула изобретения Устройство микропрограммного управления по авт.св. Р 419893, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, оно дополнительно содержит и групп элементов ИЛИ и п операционных за,поминающих блоков, причем выходы эле855662 НИИПИ Заказ 6915/ ираж 745 Подписное ментов ИЛИ первой группы соединеныс первыми группами входов операционных запоминающих блоков со второгопо (и+1)-ный, выходи элементов ИЛИсо второго по (и+1)-ую группу соединены соответственно со вторыыи группами входов операционных запоминающих блоков со второго по (и+1)-ый,илиал ППП "Патент",.Ужгород, ул.Проектн выходы которых являются выходами устройства. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРФ 419893, кл. С 06 Г 9/16, 1974

СмотретьЗаявка

2855401, 17.12.1979

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМЕНИ МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 15.08.1981

Код ссылки

<a href="https://patents.su/3-855662-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для управления обслуживанием запросов

Случайный патент: Запоминающее устройство