Микропрограммное устройство управ-ления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

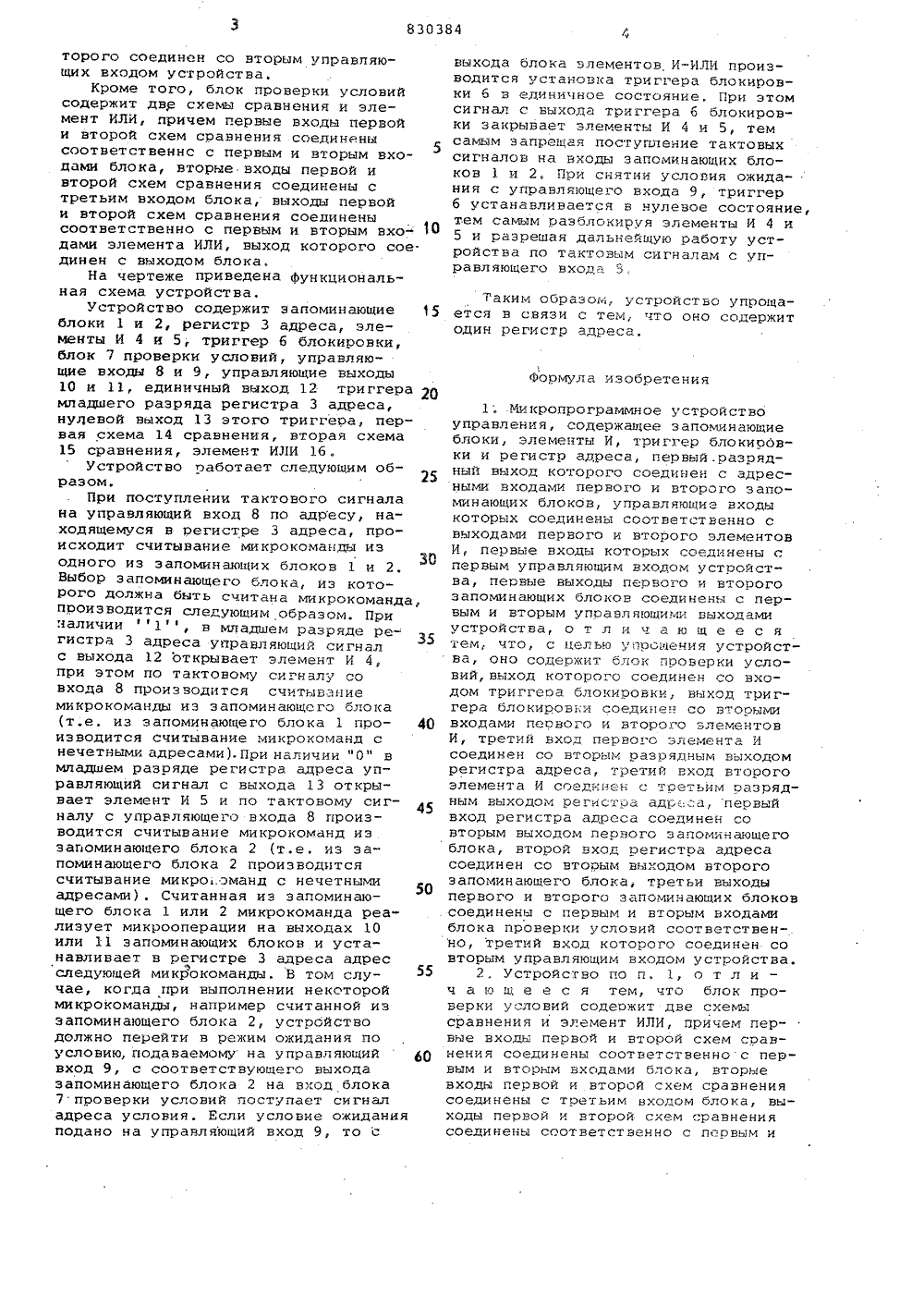

Свез Соввтскив Сщиаанстичесних Респубанк(22) Заявлено 1406.79 (21) 2785262/18-24с присоединением заявки Йо(23) ПриоритетОпубликовано 1505,8 1,бюллетень ЙЯ 18Дата опубликования описания 15 РЬ 81С 06 Р 9/22 Госуяарствеииый комитет СССР яо лелам изобретений н открытий(54) МИКРОПРОГРАММНОЕ УСТРОЯСТВО УПРАВЛЕНИЯ Из обретени е относится к вычислительной технике.Известно микропрограммное устройство управления, содержащее триггеры,коммутаторы, элементы И, регистрыадреса, запоминающие блоки 11),Недостаток устройства - избытокоборудования, так как оно содержитдва коммутатора и два регистра адреса,Наиболее близким по техническойсущности к предлагаемому являетсямикропрограммное устройство управления, содержащее,два запоминающихблока, соединенных с соответствувщими регистрами адреса, два блока про"верки условий, два триггера блокировки и два элемента И 2) .Недостатком данного устройстваявляется избыток оборудования, обусловленный наличием двух блоков проверки, двух триггеров блокировки,двух регистров адреса, работающихпоочередно.Цель изобретения - упрощение устройства. Цель достигается тем, что в устройство, содержащее запоминающие блоки, элементы И, триггер блокировки и регистр адреса, первый разрядныйвыход которого соединен с адреснымивходами первого и второго запоминающих блоков, управляющие входы которых соединены с выходами первого ивторого Элементов И соответственно,первые входы которых соединены спервым управляющим входом устройства,первые выходки первого и второго запоминающих блоков соединены с первыми вторым управляющими выходами устройства, введен блок проверки условий,выход которого соединен со входомтриггера блокировки, выход триггераблокировки соединен со вторыми входами первого и второго элементов И,третий вход первого элемента И соединен со вторым разрядным выходомрегистра адреса, третий вход второго элемента И соединен с третьимразрядным выходом регистра адреса,первый вход регистра адреса соединен со вторым выходом первого запоминающего блока, второй вход регистра адреса соединен со вторым выходом второго запоминающего блока,третьи выходы первого и второго запоминающих блоков соединены с первыми вторым входами блока проверки условий соответственно, третий вход ко 830384торого соединен со вторым управляющих входом устройства.Кроме того, блок проверки условий содержит две схемы сравнения и элемент ИЛИ, причем гервые входы первой и второй схем сравнения соединены соответственнс с первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой и второй схем сравнения соединены соответственно с первым и вторым вхо- О дами элемента ИЛИ, выход которого соединен с выходом блока.На чертеже приведена функциональная схема устройства.Устройство содержит запоминающие 15 блоки 1 и 2, регистр 3 адреса, элементы И 4 и 5, триггер б блокировки, блок 7 проверки условий, управляющие входы 8 и 9, управляющие выходы 10 и 11, единичный выход 12 триггера 2 О младшего разряда регистра 3 адреса, нулевой выход 13 этого триггера, первая схема 14 сравнения, вторая схема 15 сравнения, элемент ИЛИ 1 б.Устройство работает слецуюшчм образом.При поступлении тактового сигнала на управляющий вход 8 по адресу, находящемуся в регистре 3 адреса, происходит считывание микрокоманды из одного из запоминающих блоков 1 и 2.Выбор запоминающего блока, из которого должна быть считана микрокомандап роиэ водится следующим образ ом. ПриУналичии1 , в младшем разряде регистра 3 адреса управляющий сигнал с выхода 12 открывает элемент И 4, при этом по тактовому сигналу со входа 8 производится считывание микрокоманды из запоминающего блока (т.е. из запоминающего блока 1 про изводится считывание микрокоманд с нечетными адресами).При наличии "0" в младшем разряде регистра адреса управляющий сигнал с выхода 13 открывает элемент И 5 и по тактовому сиг налу с управляющего входа 8 производится считывание микрокоманд из запоминающего блока 2 (т,е, из запоминающего блока 2 производится считывание микропоманд с нечетными адресами). Считанная из запоминающего блока 1 или 2 микрокоманда реализует микрооперации на выходах 10 или 11 запоминающих блоков и устанавливает в регистре 3 адреса адрес следующей микрокоманды. В том случае, когда при выполнении некоторой микрокоманды, например считанной из запоминающего блока 2, устройство должно перейти в режим ожидания по условию, подаваемому на управляющий О вход 9, с соответствующего выхода запоминающего блока 2 на вход блока 7 проверки условий поступает сигнал адреса условия, Если условие ожидания подано на управляющий вход 9, то с выхода блока элементов, И-ИЛИ производится установка триггера блокировки б в единичное состояние. При этом сигнал с ьыхоца триггера б блокировки закрывает элементы И 4 и 5, тем самым запрешая поступление тактовых сигналов на входы запоминающих блоков 1 и 2. При снятии условия ожидания с управляющего входа 9, триггер б устанавливается в нулевое состояние, тем самым разблокируя элементы И 4 и 5 и разрешая дальнейшую работу устройства по тактовым сигналам с управляющего входа 5.Таким образом,. Устройство упрощается в связи с тем, что оно содержит один регистр адреса,Формула изобретения1, Микропрограммное устройство управления, содержащее запоминающие блоки, элементы И, триггер блокиоовки и регистр адреса, первый. разрядный выход которого соединен с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены с первым управляющим входом устройства, первые выходы первого и второго запоминающих блоков соединены с первым и вторым упоавляющими выходами устройства, о т л и ч а ю щ е е с я тем,. что, с целью упрощения устройства, оно содержит блок проверки условий выход которого соединен со входом триггера блокировки выход триггера блокировки соединен со вторыми входами первого и второго элементов И, третий вход первого элемента И соединен со вторым разрядным выходом регистра адреса, третий вход второго элемента И соединен с тре:ьим разрядным выходом регистра адр-са, первый вход регистра адреса соединен со вторым выходом первого запоминающего блока, второй вход регистра адреса соединен со вторым выходом второго запоминающего блока, третьи выходы первого и второго запоминающих блоков соединены с первым и вторым входами блока проверки условий соответственно, третий вход которого соединен со вторым управляющим входом устройства.2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок проверки условий содеожит две схемы сравнения и элемент ИЛИ, причем первые входы первой и второй схем сравнения соединены соответственнос первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой и второй схем сравнения соединены соответственно с первым и. Повхан Техред М. Рейвес Корректор О. Билак Реда кт П пнсноССР ак филиал ППППатент, г. Ужгоро Проектная,вторым входами элемента ИЛИ, выход которого соединен с выходом блока. Источники информации,принятые во внимание при экспертизе502/64 Тираж 745 ВНИИПИ Государственног по делам изобретений 13035, Москва, Ж, Рауш

СмотретьЗаявка

2785262, 14.06.1979

ПРЕДПРИЯТИЕ ПЯ В-8751

ХЛЮНЕВ АЛЕКСЕЙ ЛЕОНИДОВИЧ, КУЗНЕЦОВ АЛЕКСАНДР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, управ-ления

Опубликовано: 15.05.1981

Код ссылки

<a href="https://patents.su/3-830384-mikroprogrammnoe-ustrojjstvo-uprav-leniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управ-ления</a>

Предыдущий патент: Перестраиваемое микропрограммноеустройство управления

Следующий патент: Микропрограммное устройствоуправления

Случайный патент: Подметально-уборочная машина