Блок выборки адресов запоминающегоустройства

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

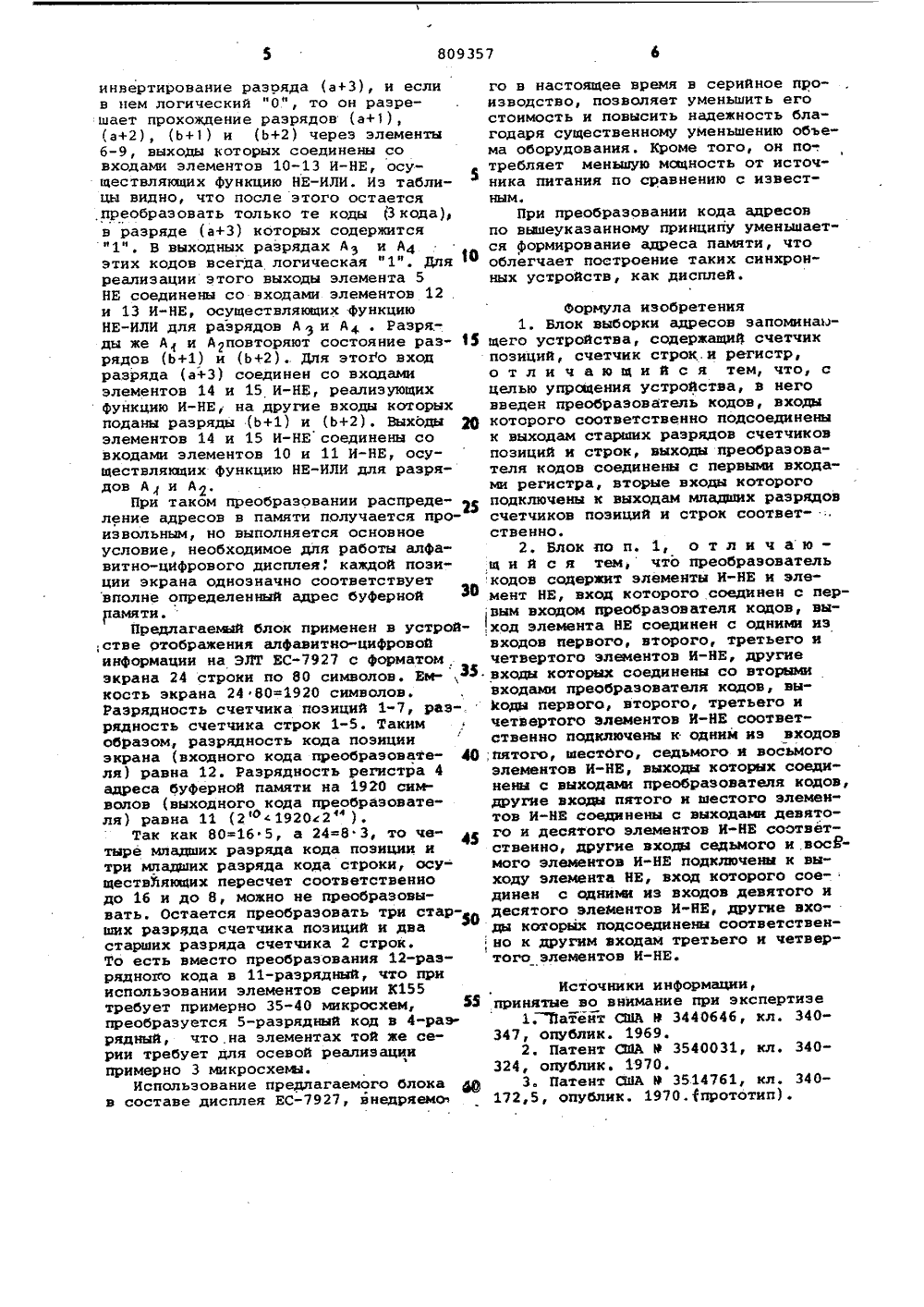

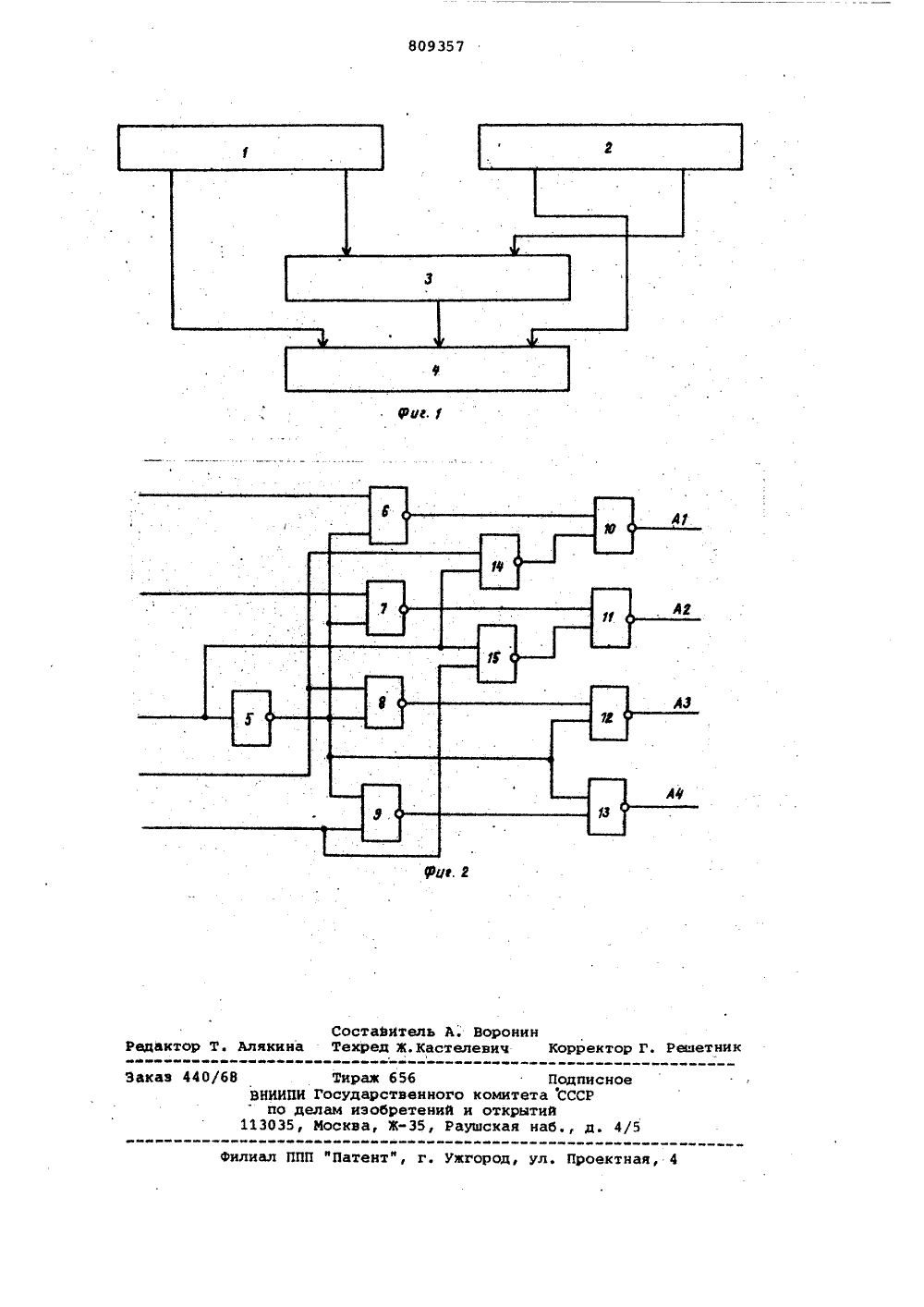

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ И АВТОУСКОМУ СВ ТВЛЬСТВУСафа Сфаетскнк Сецналнстнческих Республик(51)М. Кл.з 6 11 С 8/00 Государственный комитет СССР ио яелаи изобретений и открытий(54) ВЛОК ВЫБОРКИ АДРЕСОВ ЗАПОМИНАЮЩЕГО УСТРОЙСТВАИзобретение относится к вычисли- " тельной технике и может быть использовано в устройствах отображения алфавитно-цифровой информацик на экране ЭЛТ (дисплеях), применяющихся в каче стве буферного эапоьвнакщего устрой- . ства (ЗУ) с произвольным доступом.Известно устройство отображения, .в котором преобразование кода адреса 1 экрана в адрес буферного ЗУ реалкзс вано по классическому способу "деектфратор - шифратор", В состав блока вы-. бора адресов такого устройства входит счетчик позиций, счетчик строк, один многоступенчатый дешифратор, шифратор,И регистр адреса ЗУ (11. Недостатками такого устройства являются большие затраты оборудования, необходимого для построения двшифрато 26 ра и шифратора, многоступенчатость схема преобразователя и, как следствие этого, значительные задержки адресных сигналов при прохождении через эту схему, большое число связей между элементами и связанная с ннм сложность их реализации печатным монтажом, а также значительная мощность, потребляемая блоком выбора адресов от источников питания. 30 Известно также устройство, содержащее счетчик позиций, счетчик строк,деввфраторы младших разрядов счетчи-ков поэкций и строк, дешифраторы старших разрядов счетчиков позиций истрок к регистр адреса (2).Наиболее близким по техническойсущности к предлагаемому являетсяблок управления выбором адресов запоавюнаквюего устройства, в состав которого входят счетчик позиций, счетчикстрок и регистрадреса Зу 3,Однако для адресации ЗУ требуетсявведение в устройство дополнительного несикхронизированного реверсивногосчетчика адреса ЗУ и схем, управляющих его работой; значительная и непостоянная задержка форзщрования адреса, зависящая от исходного к требуемого адреса, что создает серьезныенеудобства при построении таких синхронаах устройств, как дисплей.Цель изобретения - упрощение устройства.Поставленная цель достигается тем,что в блок выборки адресов запоминающего устройства, содержащий счетчикпозиций, счетчик строк и регистр,введен преобразователь кодов, входыкоторого соответственно подсоединенык выходамстарших разрядов счетчиковпозиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входы которогоподключены к выходам младших разрядов счетчиков позиций и строк соответственно, а также тем, что преобразователь кодов содержит элементы И-НЕ1 и элемент НЕ, вход которого соединенс первымвходом преобразователя кодов,выход элемента НЕ соединен с однимииз входов первого, второго, третьего 1,и четвертого элементов И-НЕ, другиевходы которых соединены со вторыми входами преобразователя кодов, выходы первого, второго, третьего и четвертогоэлементов И-НЕ соответственно подключены к одним из входов пятого, шестого, седьмого и восьмого элементов,.И-НЕ, выходы которых соединены с выходами преобразователя кодов, другиевходы пятого и шестого элементов И-НЕ щсоединены с выходами девятого и десятого элементов И-НЕ соответственно,другие входы седьмого и восьмого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен содними из входов девятого и десятогоэлементов И-НЕ, другие входы которыхподсоединены соответственно к другимвходам третьего и четвертого элементов И-НЕНа фиг. 1 изображена функциональ 30ная схема блока выборки адресов запоминающего устройства," на фиг, 2 Функциональная схема преобразователякодов.35Блок выборки адресов запоминающего устройства содержит счетчик 1 позиций, счетчик 2 строк, преобразователь 3 кодов, регистр 4Преобразователь кодов содержит эле"мент 5 НЕ и элементы 6-15 И-НЕ. . 10Блок работает следующим образом.Обозначим количество позиций сим-,волов в строка алфавитно-цифровогодисплея через И, а количество строкна экране через й, Предположим, что щчисла М и й состоят из двух сомножителей, один из которых является степенью числа 2, а второй соответственно равен 5 и 3; т.е.М 2 а 5 эОй 2 3,где а и Ь - любые числа натурального ряда, кроме нуля, т.е. а, Ь =1,2,.Очевидно, что число разрядов всчетчике 1 позиций равно (4+3). Соответственно число разрядов в счетчике2 строк равно (Ь+2). Общее количество разрядов в коде позиции экранаравно а+3+Ь+2 = а+Ь+5.Количество знакомест на экране, а 0соответственно и емкость буфернойпамяти, необходимой для хранения отображаемой на экране информации равной -М. Поскольку числа й и М не являют"ся степенью числа 2, то и их произве 65дение также не является степенью числа 2, т.е. 2" йМ 7." Отсюда видно,что количество разрядов в коде адреса буферной памяти, содержащей й: Мячеек, равно Х. Тогда 2 ф,5 2" Зс 2"241522 . Отсюда Х=а+Ь+4,Поскольку формат адреса экрана(а+Ь+5) не соответствует формату адреса буферной памяти (а+Ь+4), требуется преобразовать код адреса экрана в код адреса буферной памяти. Таккак входной код является избыточным,то при преобразовании его можно минимизировать. Так как а и Ь - степени числа 2, то в этих разрядах входного кода избыточности нет. СЛедовательно, минимизировать преобразователь 3за счет этих разрядов невозможно.Значит младшие разряды а счетчика 1позиций и ьщадшие разряды Ь счетчика 2 строк можно подать в регистр 4буферной памяти без преобразования,т.е. разряды а и Ь входного кода являются составной частью разрядов х выходного кода. Остается преобразовать пять разрядов в четыре разряда. Для. этого. старшие три разряда счетчика 1 позиций и старшие два разряда счетчика 2 строк подаются на вход преобразователя 3, с выхода которого четыре преобразованных разряда поступают в регистр 4 адреса буферной памяти.ПреобразователЬ работает следующим образом.Так как разряды (а+1)-(а+3) принимают пять состояний (от О до 4), а разряды (Ь+1) и (Ь+2) - три состояния (от 0 до 2), то можно записать таблицу состояний для данного преобразователя: Входные коды Выходные коды аа 1 а+2 (а+Э Ь+ГЬаа АаАаааА Поскольку распределение адресов в памяти может быть произвольным, то таблица строится по принципу максимальной похожести кодов. Если во входном разряде (а+3, логический "О" то разряды (а+1), (а 12), (Ь+1) н (Ь+2) повторяются в выходных разрядах Я, ,й Аф. На элементе 5 осущегтеяяется 0 0 0 1 0 0 О 10 0 1 1 0 0 0 1 0 0 0 1 0 О 0 1 0 1 1 0 0 0 1 О 0 0 1 0 0 О 1 0 1 1 0 0 . 0 1 0 0 0 0 0 1 1 1 1 1 0 0 О 0 0 О 0 0 1 0 О О 1 0 0 О О о г 0 0 0 1 0 1 1 0 1 1 1 О 1 1 1 0 0 0 0 О 0 0 1 0 0 1 0 0 0 1 1 О 1 0 0 1 0 1 1 0 1 1 0 0 1 1 0 О 1 0 0 1 1 0 1 1 0 1 1 1 1Формула изобретения1. Блок выборки адресов запоминающего устройства, содержащий счетчик позиций, счетчик строк.и регистр, отличающийся тем, что, с целью упрощения устройства, в него введен преобразователь кодов, входы которого соответственно подсоединены к выходам старших разрядов счетчиков позиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входы которого подключены к выходам младших разрядов счетчиков позиций и строк соответственно.2. Блок по п. 1, о т л и ч а ю - щ и й с я тем, что преобразователь кодов содержит элементы И-НЕ и элемент НЕ, вход которого соединен с первым входом преобразователя кодов, выход элемента НЕ соединен с одними из входов первого, второго, третьего и четвертого элементов И-НЕ, другие входы которых соединены со вторыми входами преобразователя кодов, выМоды первого, второго, третьего и четвертого элементов Й-НЕ соответственно подключены к одним иэ входов ;пятого, шестбго, седьмого и восьмого элементов И-НЕ, выходы которых соеди иены с выходами преобразователя кодов, другие входы пятого и шестого элементов И-НЕ соединены с выходами девятого и десятого элементов И-НЕ соответственно, другие входы седьмого и восУ- мого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен с одними иэ входов девятого и десятого элементов И-НЕ, другие вхо" ды которых подсоединены соответственно к другим входам третьего и четвертого элементов И-НЕ. инвертирование разряда (а+3), и еслив нем логический "О.", то он разрешает прохождение разрядов (а+1),(а+2), (Ь+1) и (Ь+2) через элементы6-9, выходы которых соединены совходами элементов 10-13 И-НЕ, осуществлякщих функцию НЕ-ИЛИ. Йэ таблицы видно, что после этого остаетсяпреобразовать только те коды (3 кода),в разряде (а+3) которых содержитсяф 1". В выходных разрядах А и А 4этих кодов всегда логическая "1 ф. для фреализации этого выходы элемента 5НЕ соединены со входами элементов 12 .и 13 И-НЕ, осуществляющих функциюНЕ-ИЛИ для разрядов АЗ и А . Разря;ды же А 1 и Аповторяют состояние разрядов (Ь+1) и (Ь+2). Для этого входразряда (а+3) соединен со входамиэлементов 14 и 15 И-НЕ, реализующихфункцию И-НЕ, на другие входы которыхподаны разряды (Ь+1) и (Ь+2). Выходы ;щэлементов 14 и 15 И-НЕ соединены совходами элементов 10 и 11 И-НЕ, осуществлякщих функцию НЕ-ИЛИ для разрядов А 1 и А 2,При таком преобразовании распреде"ление адресов в памяти получается произвольным, но выполняется основноеусловие, необходимое для работы алфавитно-цифрового дисплея каждой позиции экрана однозначно соответствуетвполне определенный адрес буферной Зрамяти.Предлагаемый блок применен в устрой,стве Отображения алфавитно-циФровойинформации на ЭЛТ ЕСс Форматомэкрана 24 строки по 80 символов. Емкость экрана 2480=1920 символов.Разрядность счетчика позиций 1-7, раз-,рядность счетчика строк 1-5. Такимобразом, разрядность кода позицииэкрана (входного кода преобразователя) равна 12. Разрядность регистра 4адреса буферной памяти на 1920 символов (выходного кода преобразователя) равна 11 (2 о 1920 с 2" ).Так как 80 16 5, а 24=8 3, то че"тыре младших разряда кода позиции итри младших разряда кода строки, осуществляющих пересчет соответственнодо 16 и до 8, можно не преобразовывать. Остается преобразовать три старших разряда счетчика позиций и двастарших разряда счетчика 2 строк.То есть вместо преобразования 12-разрядного кода в 11-разрядный, что прииспользовании элементов серии К 155требует примерно 35-40 микросхем, ээпреобразуется 5-разрядный код в 4-разрядный, что на элементах той же серии требует для осевой реализациипримерно 3 микросхем.Использование предлагаемого блока щв составе дисплея ЕС, внедряемо го в настоящее время в серийное производство, позволяет уменьшить его стоимость и повысить надежность благодаря существенному уменьшению объема оборудования. Кроме того, он по-. требляет меньшую мсщность от источника питания по сравнению с известным.При преобразовании кода адресов по выаеуказанному принципу уменьшается формирование адреса памяти, что облегчает построение таких синхронных устройств, как дисплей. Источники информации,принятые во внимание при экспертизе 1. Оатейт СОИ В 3440646, кл. 340347, опублик. 1969. 2. Патент США В 3540031, кл. 340324, опублик. 1970. 3. Патент США 9 3514761, кл. 340172,5, опублик. 1970.(прототип),809357 Составитель А.техред ж.кастел оронинич Корректор Г. Реиетник Редак Т. Аляки аказ О/68 Тираж 656 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, 3-35, Раушская наб., д. 4/5 филиал ППП фПатент", г. Ужгород, ул, Проектная, 4

СмотретьЗаявка

2722294, 05.02.1979

ПРЕДПРИЯТИЕ ПЯ М-5339

БУКЧИН ЛЕОНИД ВЛАДИМИРОВИЧ, ЧЕРВЯКОВА ЛАРИСА ГАВРИЛОВНА

МПК / Метки

Метки: адресов, блок, выборки, запоминающегоустройства

Опубликовано: 28.02.1981

Код ссылки

<a href="https://patents.su/4-809357-blok-vyborki-adresov-zapominayushhegoustrojjstva.html" target="_blank" rel="follow" title="База патентов СССР">Блок выборки адресов запоминающегоустройства</a>

Предыдущий патент: Устройство для считывания информации

Следующий патент: Буферное запоминающее устройство

Случайный патент: Устройство для облегчения извлечения саженцев из траншей зимнего хранения