Перестраиваемое микропрограммноеустройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 830383

Автор: Полонский

Текст

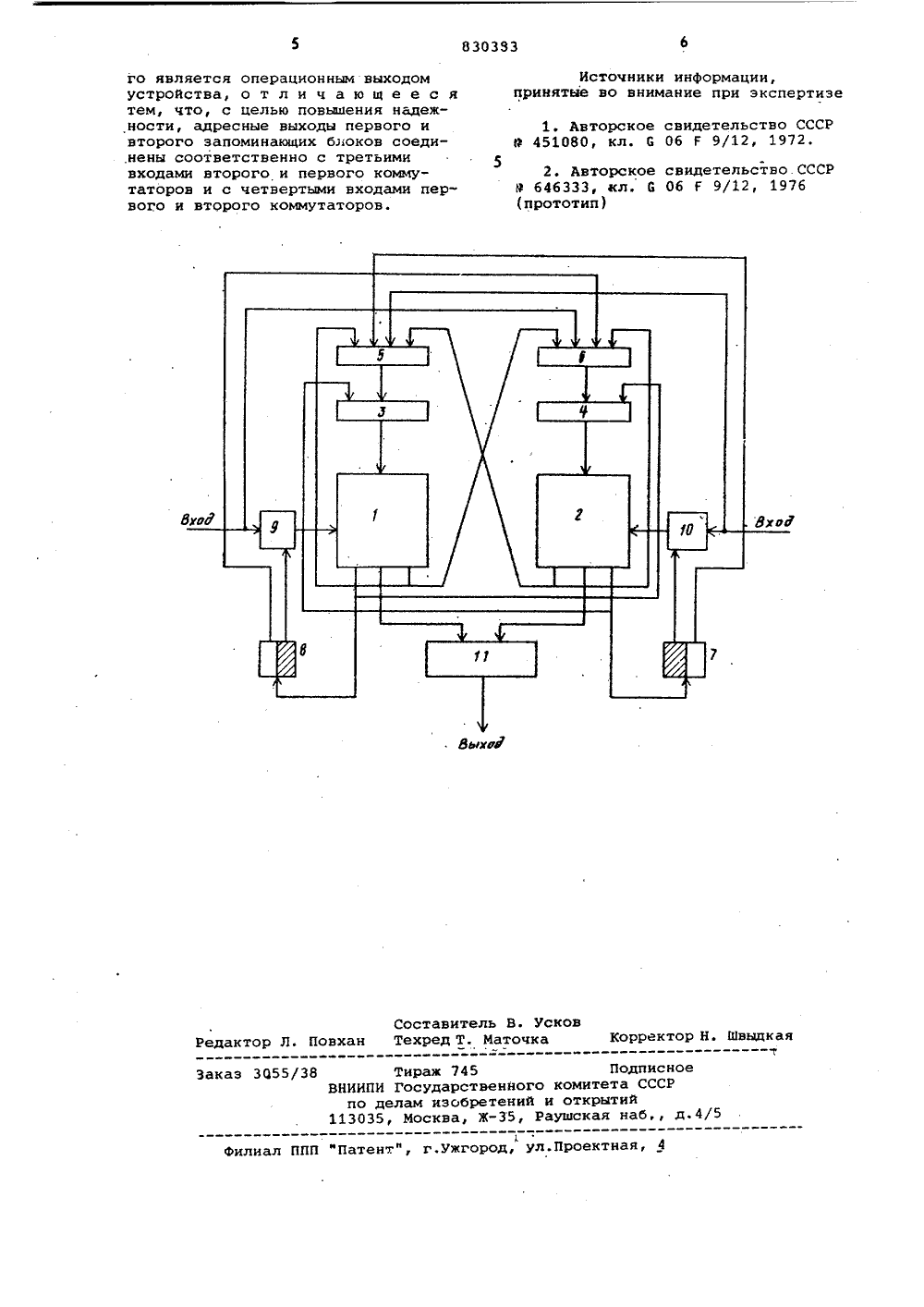

Союз Советских Социалистических Республик(22) Заявлеио 130679 (21) 2778839/18-2 с присоединением заявки йо 1)М. К 06 Г 9/22 арственный ко СССР елам нзоб н открыттет 23) Приоритет ретеннйнй ОпубликОваио 15.0581. Ьюллете 3) УДК 681.325(71) Заявите 4) ПЕРЕСТРАИВАЕМОЕ МИКРОПРОГРАММН УСТРОЙСТВО УПРАВЛЕНИЯйстваказаевозу по либочи по атком данного устрто, что в случае о регистров адресаенастройка на рабообработки отказовграмме. решения зад Недостявляетсяодного изможна перпрограммепо подпро Изобретение относится к вычислительной технике и может быть исполь. зовано в устройствах управления циФ- ровых вычислительчых машин.Известно микропрограммное устройство управления, содержащее триггеры, коммутаторы, схемы И, регист- ры адреса, запоминающие блокн 11 1.Недостаток устройства заключается в том, что в случае отказа одного из запоминающих блоков невозможна перенастройка на работу другого запоминающего блока, что снижает надежность устройства.Наиболее близким по технйческой сущности к предлагаемому является перестраиваемое микропрограь- мное устройство управления, которое содержит два запоминающих блока, два регистра адреса, два коммутатора, два триггера управления,два элемента И и элемент ИЛИ 2усеченному алгоритму. Это снижает надежность устройства.Цель изобретения - повышение на.дежности устройства.Поставленная цель достигаетсятем, что в пересматриваемом микропрограммном устройстве управления,содержащем два запоминающих блока, 10 два регистра адреса, два элементаИ, два коммутатора, два триггерауправления и элемент ИЛИ, первыевходы первого и второго коммутаторов соединены соответственнос нулевьвни выходами первого ивторого триггеров управления, выходы и",рвого и второго коммутаторов соединены соответственно спервыми инФормационными входами 2 О первого и второго регистров адреса, инФормационные выходы которыхсоединены соответственно с адреснымивходами первого и второго запоминающих блоков, управляющие вхо ды которых соединены соответственно с выходами первого и второгоэлементов И, первые входы которыхсоединены соответственно с первьвю и вторым управляющими входамиустройства . со вторыми входами1 О 15 2 О 25 35 40 45 50 55 60 б 5 второго и первого коммутаторов,вторые входы первого и второгоэлементов И соединены соответственно с единичными выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первогорегистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционныевыходы которых соединены соответстненно с первым и вторым входамиэлемента ИЛИ, выход которого является операционным выходом устройства, адресные выходы первого инторого эапомийающих блоков соединены соответственно с третьимивходами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов,На чертеже представлена функциональная схема устройства.Устройство содержит первый запоминающий блок 1, второй запоминающий блок 2, первый регистр 3 адреса, второй регистр 4 адреса,первый коммутатор 5, второй коммутатор б, первый триггер 7 управления, второй триггер 8 управления,первый элемент И 9, второй элементИ 10, элемент ИЛИ 11.( Устройство работает следующимобразом.Пусть н исходном состоянии первый триггер 7 управления и второйтриггер 8 управления находятся вединичном состоянии и пусть нарегистре 3 (4) адреса находитсяадрес микрокоманды, подлежащейсчитыванию. Так как триггеры 7 и8 управления находятся в единичномсостоянии, то они разрешают прохождения поступившего на вход тактового импульса через элементы И 9(10) и обеспечивают прохождение навыход коммутатора 5 сигналов с запоминающего блока 2, а на выходкоммутатора б сигналов с выхода запоминающего блока 1. На адресномвыходе запоминающего блока 1 (2)появляется считанная микрокоманда,и адрес следующей микрокоманды через коммутатор б (5) поступаети регистр 4 (3) адреса. На выходеустройства микрооперации с операционных выходон запоминающих блоков появляются поочередно.При отказе одного запоминающего блока, например 1 , и (или)одного регистра адреса, например4, происходит перестройка микропрограммного устройства, а именно:с управляющего выхода блока 1 навход регистра 4 адреса подаетсясигнал, устанавливающий на этомрегистре фиксиронаннь;й адрес. Сэтого же выхода запоминающегоблока 1 подается сигнал на счетный вход триггера 8, который устанавливает его в нулевое состоя-ние. При этом триггер закрываетэлемент И 9, блокируя запуск запоминающего блока 1, и одновременно коммутатор б обеспечивает прохождение на вход регистра 4 адреса сигнала с адресного выходазапоминающего блока 2. Адрес сле,дующей микрокоманды, считанный с выхода работающего запоминающего блока 2, поступает на вход коммутатора б, и далее в регистр адреса 4. По данному адресу запоминающий блок 2 выдает микрооперацию на элемент ИЛИ 11 и далее на выход устройства, а адрес следующей микрокоманды на коммутатор б.Таким образом, повышение надежности устройства достигается тем, что в случае .отказа одного иэ запоминающих блоков или регистра адреса, другой запоминающий блок перестраинаемого микропрограммного устройства продолжает работать и по фиксированному адресу устройство переходит на программу обработки отказов. Формула иобретения Перестраиваемое микропрограммное устройство управления, содержащее два запоминающих блока, два регистра адреса, два элемента И, два коммутатора, два триггера управления и элемент ИЛИ, первые входы первого и второго коммутаторов соединены соответственно с нулевыми выходами первого и второго триггеров управления, выходы первого и второго коммутаторов соединены соответственно с первыми информационными входами первого и второго регистров адреса, информационные выходы которых соединены соответственно с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым и вторым управляющими входами устройства и со вторыми входами второго и первого коммутаторов, вторые входы первого и второго элементов И соединены соответстненнос единичными выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первогс регистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционные выходы которых соединены соответственно с перным и вторым входами элемента ИЛИ, выход которо830383 оставитель В. Ускоехред Т. Маточка ктор Н. Швыдкая дактор Л. Повхан 745 Подписноерственного комитета СССРобретений и открытийа, Ж, Раушская наб д.4/5 Заказ 3055/3 ТиражНИИПИ Госудпо делам и13035, Моск филиал ППП "Патент", г.ужгород, ул.Проектная, 4 го является операционным выходомустройства, о т л и ч а ю ш е е с ятем, что, с целью повышения надежности, адресные выходы первого ивторого запоминающих блоков соеди,нены соответственно с третьимивходами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 451080, кл. 6 06 Г 9/12, 1972.52, Авторское свидетельство. СССРУ 646333, кл. С 06 Г 9/12, 1976

СмотретьЗаявка

2778839, 13.06.1979

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО КИЕВСКОГОУПРАВЛЕНИЯ ПРОЕКТНО МОНТАЖНЫХ РАБОТ

ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммноеустройство, перестраиваемое

Опубликовано: 15.05.1981

Код ссылки

<a href="https://patents.su/3-830383-perestraivaemoe-mikroprogrammnoeustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Перестраиваемое микропрограммноеустройство управления</a>

Предыдущий патент: Микропрограммное устройствоуправления

Следующий патент: Микропрограммное устройство управ-ления

Случайный патент: Ротационный вискозиметр