Устройство для умножения двоичнодесятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

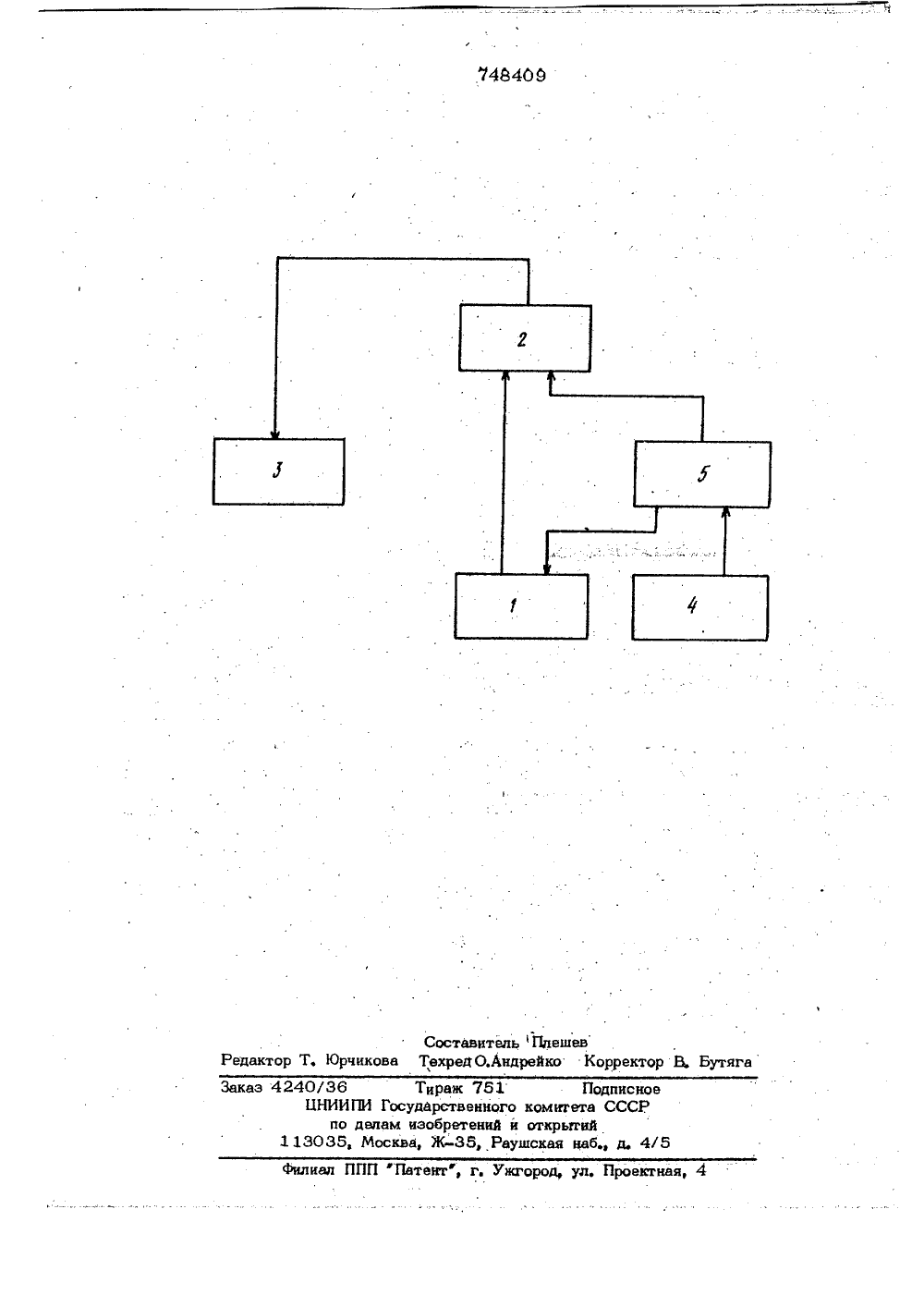

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоцналнстнческнкРеспублик(5 Г)М, Кл. 6 06 Р 7/39 с присоединением заявки УЙ -Гасударственный ттеннтет СССР(23) ПрнорнтетОпубликовано 15.07,80. Бюллетень М 26 по юам изобретений н открытийДата опубликования описании 17,07.80(72) Авторы изобретения Ю. С. Павленко и И. М. Петущак Киевский технологический институт легкой промышленности(54) УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ Изобретение относится к области вычислительной техники и предназначено дпяиспользования в специализированных вычислительных машинах,Известно устройство умножения двоичных чисел 1, в котором десятичное ум ножение осуществляется с помощью последовательного сложения, множимое прибавляется к частичному произведению столькораз, какова цифра множителя. Быстродейст-,вие такого устройства низкое, так как приоумножении на И -разрядный множитель нужно сделать 4,5 и сложений. Наиболее близким техническим решением к изобретению является устройство для умножения двоично-десятичных чисел 21, содержащее регистр множителя, сумматор частичных произведений, блоки сдвига и определения очередности цифр, причем раэ 20 рядиые выходы регистра множителя подключены к входам блока определейия очередности цифр, выходы которого подключены к управляющим входам блока сдвига,2выходы блока сдвига подключены к входамсумматора частичньм произведений.Однако известное устройство требуетзначительных аппаратурных затрат и обладает недостаточным быстродействием припроведении операций с числами, разрядность которых и ( 13,Целью изобретения является повышениебыстродействия устройства и снижение ап 1паратурных затрат,Бель достигается тем, что предложенное устройство дополнительно содержитблок удвоения множимого, разрядные ваходы которого соединены с разряднымивходами блока сдвига, выход блока определения очередности: цифр подключен к входу сдвига блока удвоения множителя, состоящего из И +3 разряда.На чертеже представлена структурнаясхема устройства умножения двоично-десятичных чисел.Устройство содержит блок 1 удвоениямножимого, блок 2 сдвига, сумматор 3частичных произведений, регистр 4 мно3 74840 жителя, блок 5 определения очередности цифр (БООЦ).В исходном состоянии в блок 1 удвоения множимого и регистр 4 множителя занесены коды сомножителей. В первом цикле умножения в БООЦ 5 определяют 5 ся тетрады множителя, содержащие еди- ницы в разряде 2 . Так, если множитель представлен числом 1000 1001 0010, 0001 0011 0001, то первой будет отме чена первая тетрада (счет тетрад справа налево), в нулевом разряде которой за писана единица.В данном случае БООЦ выдает сигналы, по которым множимое передается на блок 15 сдвига 2; а затем без проведения микро- операции сдвига на сумматор 3 частичных произведений. Йалее в БООЦ определяется единица во второй тетраде и выдаются сигналы передачи множимого из блока 1 уд воения множимого через блок сдвига на сумматор частичных произведений со сдвигом на один десятичный разряд влево. В результате последующего анализа тетрвд множителя обнаруживаются единицы . в 25 третьей и пятой тетрадах и множимое передается на сумматор частичных произведений со сдвигом соответственно на два и четыре десятичных разряда влево. После нахождения всех тетрад множителя, со держащих единицы в разряде 2, БООЦо дает разрешение на проведение второго цикла умножения. В начале второго цикла по сигналу 35 БООЦ 5 осуществляется удвоение содержимого блока 1 удвоения множимого. Удвоение осуществляется сдвигом кода множимого на один двоичный разряд влево и последующей коррекцией полученного при 40 сдвиге числа, Коррекция заключается в приприбавлении числа 6 (0110) к содержимому тех тетрад, где имеет место или наличие в тетраде чиспа больше девяти, или переход единичного сигнала из млад шей тетрвды в старшую. Затем аналогично предыдущему циклу определяются тетрады, содержащие единицы в разряде 2. В приведенноь( множителе такими тетрадвми являются вторая и четвертая, что 50 соответствует передаче содержащего бпо 1 ка 1 удвоения множимого в сумматор со сдвигом на один и три соответственно разряда влево в блоке сдвига 2,после чего дается разрешение БООЦ 5 на про ведение третьего числа умножения. Третий и четвертый циклы умножения осуществляются аналогично второму циклу.4. Итак, для получения чисел, кратных множимому, нужно осуществить три операции сдвига вместо восьми операцийсложения, как в прототипе, Для умножения на.п -разрядный множитель требуется осуществить три сдвига и 1,5 п сложений.Время осуществления операции сдвигаменьше времени осуществления операции сложения более чем в два раза.Среднее время умножения на и -разрядный множитель в предлагаемом устройстве Тп 1 бсл+ 4,5 илв прототипе Т = ЬВ + й 1.ь сл слгде .Ьсл - время осуществления операции сложения.Из уравнения М М = 1,51 л+1,5 п 1СЛсл . СЛ 1 д= 15 находим что время выполнения операции умножения в предлагаемом устройстве; меньше, чем в прототипе, если количество десятичных разрядов множителя п 4 13. В частности, для И=5 Т =% Т =131Оъ сл) и Одля о=О Тоу 4 фсл 1 Т =ЖУстройство можно выполнить нв современных интегральных микросхемах. Егоиспользование дает возможность умешшить конструктивные размеры вычисл ительной машины и повысить ее быстродействие,формула изобретенияУстройство для умножения двоичнодесятичных чисел, содержащее регистрмножителя, сумматор частичных произведений, блок сдвига и блок определенияочередности цифр, причем разрядные выходы регистра множителя подключены квходам блока определения очередностицифр, выходы которого подключены к управляющим входам блока сдвига, выходыблока сдвига подключены к входам сумматора частичцых произведений, о т л ич а ю щ е е с я тем, что,с целью повышения быстродействия устройства иснижения аппаратурных затрат, в неговведен блок удвоения множимого, содержащий О +3 разряда, где и - количестворазрядов множимого, при этом разрядныевыходы блока удвоения миожимого соединеныс разрядиымивходами блока сдвига, выходблока определения очередности цифр подключен к входу сдвига блока удвоения множимого,Источники информации,принятые во внимание при экспертизе1. Майоров С, А. Принципы организации цифровых машин, Ленинград, фМашиностроение", 1974, с. 322-323.2. Авторское свидетельство СССРМ 510714, кл. Я 06 Р 7/52,05,05.74 (прототин).СоставительПлешевактор Т, Юрчикова Техред О.Андрейко Корректор В. ППП Патентф, г. Ужгород, ул. Проект 4240/36 Тираж 781 ЦНИИ ПИ Государственного по делам изобретений и 113038, Москва, Ж, Рау

СмотретьЗаявка

2469468, 28.03.1977

КИЕВСКИЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ ЛЕГКОЙ ПРОМЫШЛЕННОСТИ

ПАВЛЕНКО ЮРИЙ СТЕПАНОВИЧ, ПЕТУЩАК ИРИНА МИХАЙЛОВНА

МПК / Метки

МПК: G06F 7/39

Метки: двоичнодесятичных, умножения, чисел

Опубликовано: 15.07.1980

Код ссылки

<a href="https://patents.su/3-748409-ustrojjstvo-dlya-umnozheniya-dvoichnodesyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двоичнодесятичных чисел</a>

Предыдущий патент: Устройство для сравнения двоичных чисел

Следующий патент: Устройство для деления двоичных чисел

Случайный патент: Колосниковый холодильник