Арифметическое устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 711570

Автор: Казаков

Текст

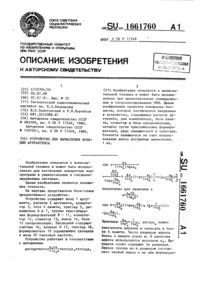

Союз Советских Социалистических Республик(51)М. Кл.2 6 06 Е 7/38 Государственный комитет ССС Р по делам изобретений и открытий(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО Изобретение относится к вычислительной технике и может использоваться в специализированных цифровых вычислительных машинах, работакщих в двоичной системе ,счисления с числами с фиксированной запятой.Известны арифметические устройства для сложения и умножения, содержащие регистры комбинацион Й суа тор, устройство управления и устройство анализа переполнения разрядной сетки. В процессе умножения в таких устройствах для исключения потерь единиц, возникающих при переполнени- ях, либо осуществляют предварительный сдвиг множимого вправо на один разряд, либо применяют специальные схемы анализа и коррекции 1) и 23. Недостатками таких устройств яв-ляется неоднозначность определенияпереполнения при сложении и умножении и сложная структура.Наиболее близким техническим решением к изобретению является арифметическое устройство, содержащее регистрслагаемого и регистр результата, одноразрядный сумМатор, линию задержки,схему анализа перепрлнения разряднойсетки и блок управления 2),Недостатком этого устройства является сложность проведения коррекции знака результата в случае переполнения разрядной сетки и органиэации арифметических модифицированных сдвигов в операциях умножения и деления.Цель изобретения - снижение аппаратурных затрат при органиэации коррекции результата.Это достигается тем, что в ариф" метическое устройство, содержащее первый и второй регистры, регистр результата и комбинационный сумматор, причем выход первого регистра и выход регистра результата подключены к входам комбинационного сумматора, выход которого соединен с входам регистра результата, младший разряд которого подключен к знаковому разряду второго регистра, дополнительно введены первый, второй, третий и четвертый элементы И и триггер, причем первые входы первого и четвертого, второго и третьего элементов И подключены соответственно к единично)му и нулевому выходам знакового разряда регистра результата, вторые вхоцы первого и третьего, второго и четвертого элемента И соединены соот- ветственно с нулевым и единичным выходами знакового разряда первого регистра, выходы первого и второго, третьего и четвертого элементов И подключены соответственно к установ ленным в единицу и нуль входам триггера, первый вход которого подключен к нулевому выходу сигнала переноса комбинационного сумматора, а выход триггера - к знаковому разряду регистра результата., На чертеже представлена структурная схема предлагаемого арифметического устройства. ьрифметическое устройство имеетпервый регистр 1, регистр результа,та 2, комбинационный сумматор 3, второй регистр 4, элементы И 5-8 и триггер 9.Перед началом ныпспнения операциисложения в регистре 1 хранится однослагаемое, в регистре 2 - второе, 20причем разрядные шины первого и второго регистров подключены к вхсднымшинам комбинационного сумматора 3,выходные шины которого подключены крегистру результата 2, 2Об а. опера нда представляют собойдйоичные числа с фиксированной запятой, записанные в дополнительном коде. Для записи знака чисел в регистрах 1 и 2 и в Комбинационном сумма".торе 3 используется по одному знаковому разряду. Установка триггера 9перед сложением производится по следующему правилу: если знаковые разряды регистров 1 и 2 сонпадают, тотриггер устанавливается в нуль еслизнаковые разряды регистров 1 и 2 отличаются, то триггер устанавливаетсяв единицу,Если в конце сложения возникаетперенос из нулевого разряда суммато" 40ра, то содержимое триггера иннертируется,Результат суммирования записывается в регистре результата 2.В случае переполнения разрядной.сетки арифметического устройства,содержимое триггеров 9 и знаковогоразряда регистра результата 12 несовпадает.При выполнении операции умноженияв исходном состоянни в регистре 1хранится множимое, в,;регистре 4 -множитель, Промежуточная сумма частичных произведений накапливается врегистре 2 и при сдвиге вправо младшая фасть ее переходит н старшие раэ"ряды регистра 4,Триггер 3 участвует в накоплениисумм частичных произведений в модифицированном дополнительном коде ииспользуется для осуществления модифицированного сдвига вправо. Знакпроизведения вырабатывается автоматически в ходе перемножения сомножителей и произведение получается в коде,соотнетстйущщем его знаку. 65 Перед началом умножения обнуляется триггер 3 и регистр .2 частичныхпроизведений, В каждом такте умножения анализируется младший разряд множителя, Если он равен единице, томножимое, расположенное и регистре1, складывается с содержимым регистра 2, как при операции сложений, гденакапливается сумма частичнйх произведений,Далее осуществляется операциясдвига,Содержимое триггера 9 регистровчастичных произведений и множителя4 сдвигается арифметически вправо наодин разряд.Циклический процесс умножения повторяется до выполнения заданного количества итераций.После п-го сдвига, где п - числодвоичных разрядов сомножителей, знаковый разряд. множителя переместитсян младший его разряд, по которомуосуществляется корректирующий шаг .Если младший разряд множителя равен нулю, то коррекции нет. В противтном случае имеет место корреляция;инвертированное содержимое регистрамножимого 1, увеличенное на единицу,суммируется с содержимым регистра 2частичных произведений.После окончания умножения старшиеразряды произведения располагаютсяв регистре 2, младшие разряды - встарших разрядах регистра 4.Формула изобретенияАрифметическое устройство, содержащее первый и второй регистры, регистр результата и комбинационный сумматор, причем выход первого регистра и выход регистра результата подключены к соответствующим входам комбинационного сумматора, выход которого соединен с входом регистра результата, младший разряд .которого подключен к знаковому разряду второго регистра, о т л и ч а ю щ е е с я тем, что, с целью снижения аппаратурных затрат, в устройство дополнительно введены первый, второй, третий и четвертый элементы И и триггер, причем первые входы первого и четвертого, второго и третьего элементов И подключены соответственно к единичному и нулевому выходам знакового разряда регистра результата, вторые входы первого и третьего, второго и четнертого элементов И соединены соответственно с нулевым и единичным выходами знакового разряда первого регистра, выходы первого и второго, третьего и четвертого элементон И подключены соответственно к установленным в единицу и нуль входам триггера, первый вход которого подключен к нуленому выходу сигнала переноса71 1570 6 Составитель В. Венцель ак тор Л, Лашкова Техред: М.Петко Корректор М. Шарошие Тираж 751 НИИПИ Государственного ко по делам изобретений и 35, Москва, Ж, Раушскаодписно 13/3 а тета СССкрытийнаб д. ППП 11 Патентф, г. Ужгоро Проектная ф комбинационного сумматора, а выходтриггера - к знаковому разряду регистра результата. Источники информации,принятые во внимание при экспертизе1, Дроздов Е. А., Комарницкий В.А. и Пятибратов а, П. Электронные вычислительные машины ЕС . - М 197 б.2. Авторское свидетельство СССР Р 429423, кл, 6 16 Г 7/54, 1975 (прототип) .

СмотретьЗаявка

2677129, 23.10.1978

ПРЕДПРИЯТИЕ ПЯ А-7451

КАЗАКОВ ПАВЕЛ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: арифметическое

Опубликовано: 25.01.1980

Код ссылки

<a href="https://patents.su/3-711570-arifmeticheskoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Арифметическое устройство</a>

Предыдущий патент: Устройство для выделения кода

Следующий патент: Устройство для суммирования импульсных последовательностей

Случайный патент: 162979