Процессорный модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 700863

Авторы: Винников, Кафтанников, Никитин

Текст

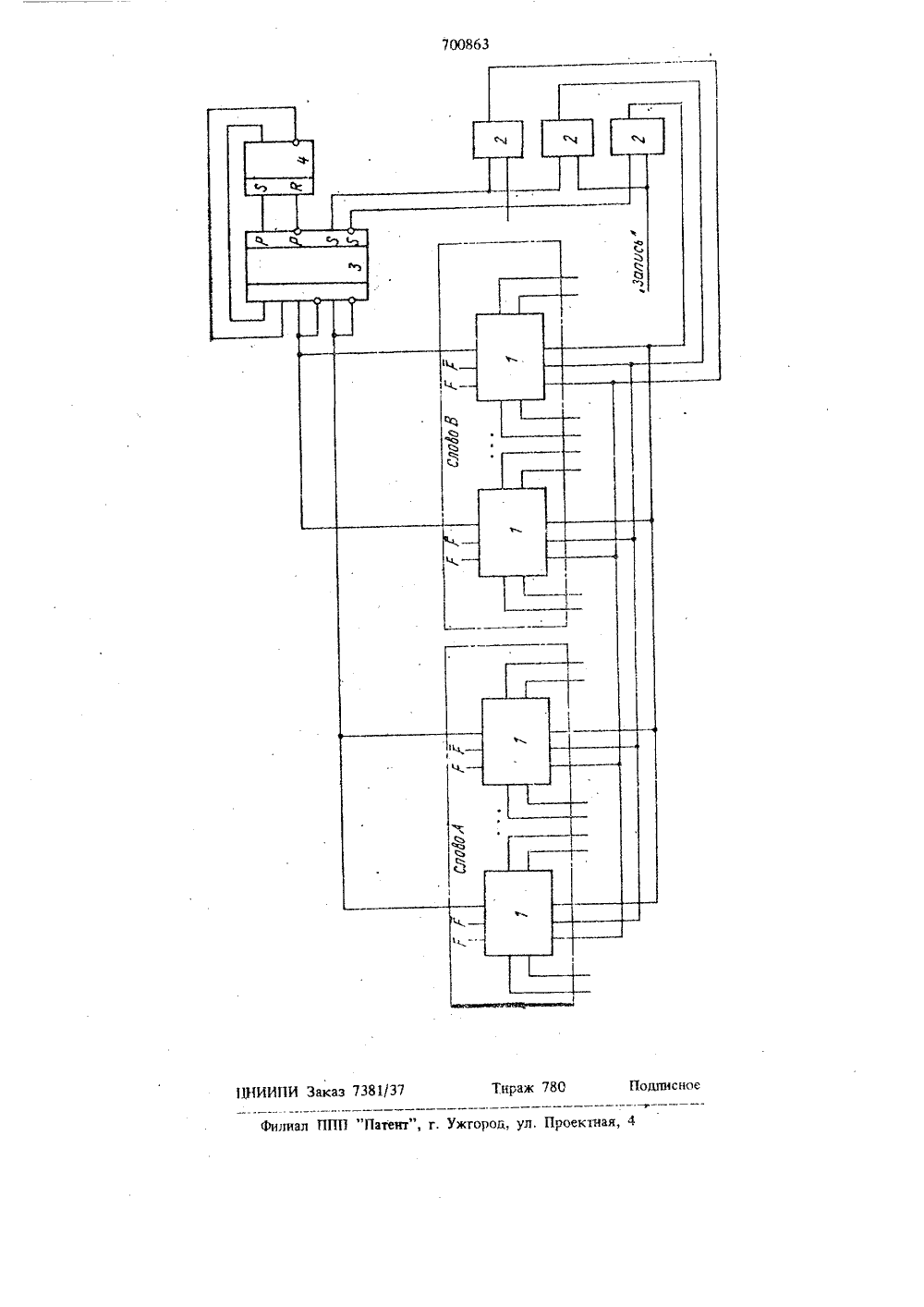

(22) За я влено 04.05.78 (21) 2609936/18-24 с присоединением заявки РЙ -(23) Приоритет но дедам изобретений и открытий(72) Авторы изобретения Б. В, Винников, И. Л. Кафтанников и Г. А. Никитин Челябинский политехнический институт имени Ленинского комсомола(54) ПРОЦЕССОРНЫЙ МОДУЛЬ Изобретение относится к вычислительной технике и может быть использовано при построении ассоциативных процессоров.Известен процессорный модуль, содержащий триггеры, элементы И, ИЛИ 1) . Недостатком5 его является низкое быстродействие. Наиболее близкое к изобретению техничес.кое решение - процессорный модуль, содержащий две группы ячеек памяти, входы разреше.10 ния записи которых соединены с выходом первого элемента И, входы разрешения считывания ячеек памяти соединены с выходом второго элемента И, первые входы первого и второго элементов И являются первым и вторым вхо.дами модуля, а вторые входы соединены с первым прямым выходом сумматора, второй прямой и инверсный выходы которого соединены с входами триггера, выходы которого подклю.чены к первому и второму входам сумматора, третий и четвертый входьг которого подключены к выходам ячеек памяти соответственно пер вой и второй групп. Модуль содержит кроме того ячейки памяти записи результата г 21,Недостаток модуля состоит в низком быстродействии.Цель изобретения - повышение быстродействия модуля.Цель достигается тем. что предлагаемый модуль содержит третий элемент И, первый вход которого является третьим входом модуля, второй вход соединен с первым инверсным выходом сумматора, а выход подключен к входу разрешения записи инверсного кода каждой ячейки памяти.На чертеже показан предлагаемый модуль.Модуль содержит ячейки 1 памяти, элементы И 2, сумматор 3, триггер 4.Модуль работает следующим образом.В первую и вторую группы ячеек памяти записываются соответственно первый и второй операнды. При выполнении команды опрос - запись и подаче на входы опроса разрядов операндов, а на входы записи сигнала Вь = 1, на прямом выходе сумматора формируется сигнал, равный результату суммирования разрядов и содержимого триггера, а на выходе третьего элемента И появляется его инверсия.3 700863 Единичный сигнал на прямом выходе сумматора позволяет записать единичный результатсуммирования, а сигнал на инверсном выходе нулевой результатсуммирования.Таким образом, результат одноразрядной операции может быть записан без предварительной обработки, а следовательно, быстродействие предлагаемого модуля выше известных. Формула изобретенияПроцессорный модуль, содержащий две группы ячеек памяти, входы разрешения записи . которых соединены с выходом первого элемен.5 та И, входы разрешения считывания ячеек памяти первой и второй групп соединены с выходом второго элемента И, первые входы первого и второго элементов И являются соответственно первым и вторым входами модуля, а вторые 2 о входы соединены с первым прямым выходом 4сумматора, второй прямой и инверсный выходыкоторого соединены с входами триггера, выходыкоторого подключены к первому и второмувходам сумматора, третий и четвертый входыкоторого подключены к выходам ячеек памятисоответственно первой и второй групп, о т л ич а ю щ и й с я тем, что, с целью повышениябыстродействия, он содержит третий элемент И,первый вход которого является третьим входоммодуля, второй вход соединен с первым инвер.сным выходом сумматора, а выход подключенк входу разрешения записи инверсного кодакаждой ячейки памяти.Истощщки информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР Ю 479114,кл. 6 Об Е 7/38, 1972,2, Медведев И, Л., Прантишвнли И. В Чудин А. А, Многопроцессорные вычислительныесистемы с перестраиваемой структурой, М. ИЛУ,1975, с. 42, 43 (прототип).

СмотретьЗаявка

2609936, 04.05.1978

ЧЕЛЯБИНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ВИННИКОВ БОРИС ВАСИЛЬЕВИЧ, КАФТАННИКОВ ИГОРЬ ЛЕОПОЛЬДОВИЧ, НИКИТИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: модуль, процессорный

Опубликовано: 30.11.1979

Код ссылки

<a href="https://patents.su/3-700863-processornyjj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Процессорный модуль</a>

Предыдущий патент: Адаптивный пороговый модуль

Следующий патент: Многофункциональный модуль

Случайный патент: Устройство для удержания пяточной части обуви в безопасном лыжном креплении