Запоминающее устройство с выборкой по содержимому

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 690486

Авторы: Арлазаров, Варпаховский, Волков, Годунов, Дагурова, Емельянов, Золотухина, Лихонинский, Лысиков, Макаров, Сорокин

Текст

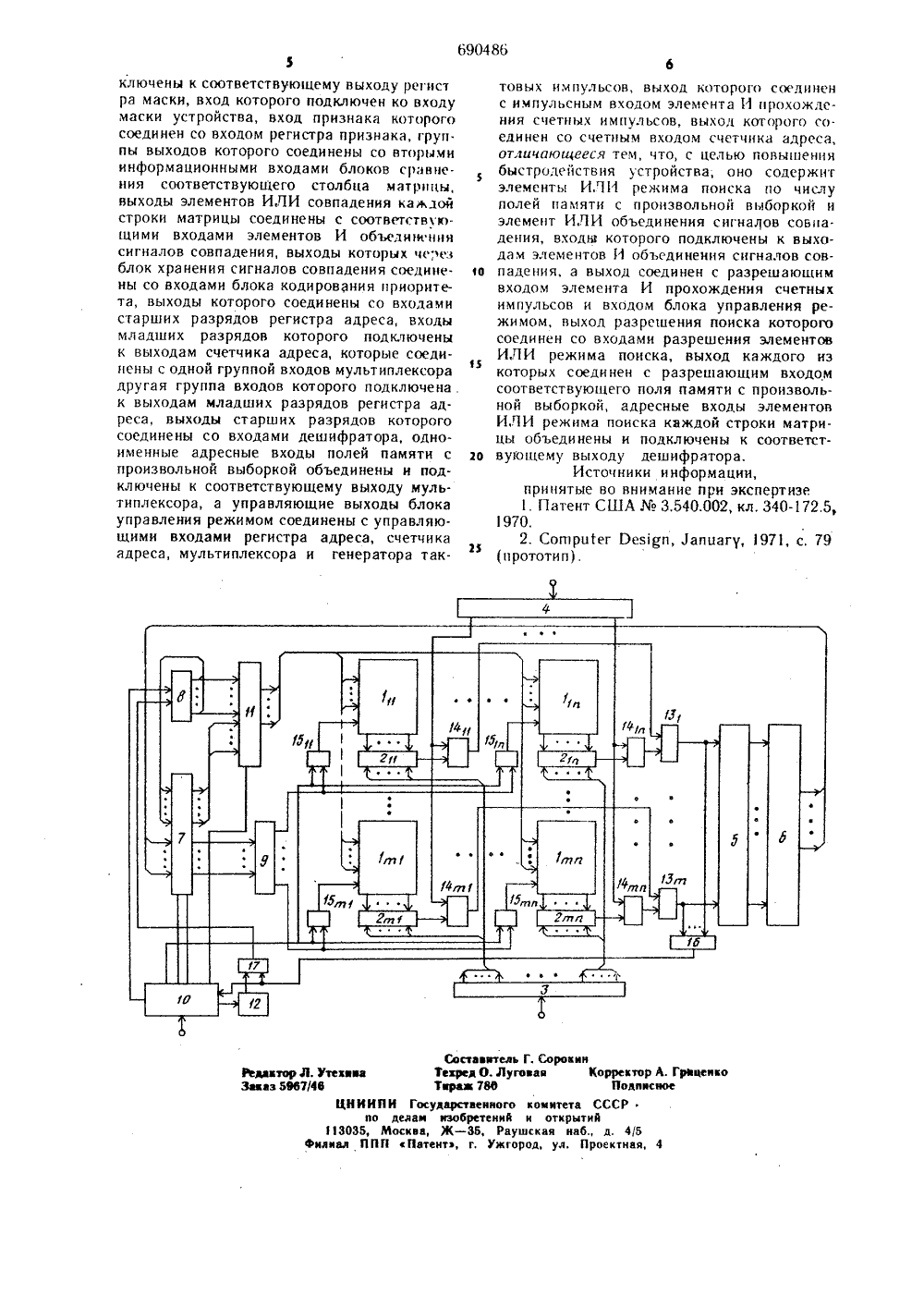

(51) М, Кл.б 06 Г 13/О ооударстаонный номнт ссср оо долам нзобратаннй и открытнй23) Прио ет -овано 05.10.79 53) УДК 681.325 (088.8 т Опубли нлетень3 Дата опубликования описания 15.10.79 чков, А. Н. ГодуновЗолотухина,ров и Г, К. Сорокин(71) Заявит рдена Ленина ттнститут проблем управления 54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВ С ВЫБОРКОЙ ПО СОДЕРЖИМОМУ к области вычисИзобретение относитсялительной техники,Известно ЗУ с выборкой по содержимому 11, состоящее из ассоциативных элементов и узла выбора слова. Недостатками такого ЗУ являются повышенная стоимость бита, высокие отношения вывод/схема и мощность рассеяния.Наиболее близким по технической сущности к изобретению является устройство 21, содержащее матрицу полей памяти с произвольной выборкой, выходы которых соединены с первыми информационными входами соответствующих блоков сравнения, выходы которых соединены со входом сигнала совпадения соответствующих элементов ИЛИ совпадения. Входы маскирования элементов ИЛИ совпадения каждого столбца матрицы объединены и подключены к соответствующему выходу регистра маски, вход которого подключен ко входу маски устройства, вход признака которого соединен со входом регистра признака, группы выходов которого соединены со вторыми информационными входами блоков сравнения соответствующего столбца матрицы. Выходы элементов ИЛИ совпадения каждой строки матрицы соединены с соответствующими входами элементов И объединения сигналов совпадения, выходы которых через блок хранения сигналов совпадения соединены со входами блока кодирования приоритета, выходы которого соединены со входами старших разрядов регистра адреса, входы младших разрядов которого подключены к выходам счет- чика адреса, которые соединены с одной группой входов мультиплексора, другая группа входов которого подключена к выходам, младших разрядов регистра адреса, Вь 1 ходы старших разрядов последнего соединены со входами дешифратора. Одноименные адресные входы полей памяти с произвольной выборкой объединены и подключены к соответствующему выходу мультиплексора, а управляющие выходы блока управления, режимом соединены с управляющими входами регистра адреса, счетчика адреса, мультиплексора и генератора тактовых импульсов ф выход которого соединен с импульсным входом элемента И прохождения счетных импульсов, выход которого соединен со счетным входом счетчика адреса.Формула изобретения Недостатком такого ус-р .йства являетсянизкое быстродействие, Целью изобретения является повьшениебыстродействия устройства. Поставленная цель достигается тем, что Предложенное устройетво содержйт элементы ИЛИ режима поиска по числу полей памяти с произвольной выборкой и элемент ИЛИ объединения сигналов совпадения, входы которого подключень к выходам элементов И объединения сигналов совпадения, а выход соединен с разрешающим входсм элемента И прохождения счетных импульсов и входом блока управления режимом, выход разрешения поиска которого:,динен со входами разрешения элементов ":,г 1 И режима поиска, вьгход каждого нз которых соединец с разрешающим входом соответствукццего поля памяти с произвольной выборкой. Лдресные входы элементов ИЛИ режима поиска каждой строки матрицы обьедигегг и подключены к соответствующему выходу дсшцфратора.Структурная схема устройства приведена на чертеже. Устройство содержит полн памяти с произвольной выборкой 1 - 1 гге, блоки сравнения 2, - 2,с, регистр признака 3, регистр маски 4, блок хранения сигналов совггадеция 5, блок кодирования приоритета 6, регистр адреса 7, счетчик адреса 8, дешифратор 9, блок управления режимом 10, мультггплессор 11, генератор тактовых импульсов 2, элементы И 13 - Згп объединения сигналов согцадения, элементы ИЛИ 14 - 4,щсовпадеггия, элементы ИЛИ 15 - 15 пл режима поиска, элемент ИЛИ 16 объединения сигналов совпадения, элемент И 17 прохождения счетных импульсов. Устройство работает следующим образом, В режиме поиска по содержимому блок управления режимом 10 устанавливает в нуль счетчик адреса 8 и с помощью мультиплексора 11 подключает выходы счетчика адреса 8 к адресным входам полей памяти1 и. Затем блок управления режимом 1 О вырабатывает сигнал режима поиска, который через элементы ИЛИ 5 - 5 п подается ца входы разрешения полей памяти 11 гги запускает генератор 12, импульсы с выхода которого через элемент И 17 подаются на вход счетчика адреса 8. В результате код адреса, подаваемьв на адресгпге входы полей памяти 1 - 1, увеличивается на единицу на каждый импульс гегератора 12, г ца блоки сравнения 2 - 2 гподаются очередные слова, выбираемые из полей памяти 1 - 1 л. На блоки сравнения 2 - 2 юл подаотея также данные из регистра признака 3. При совпадеции данных, хранимых в регистре признака 3 о 35 И 25 3. и слова, хранимого в полях памяти 1 - е блоки сравнения 2 - 2 гвьрабатгвак)т сиггалы сонгадеия, которые проходят через элементы ИЛИ 4- 4, объединяются элементом И 13, затем проходят элемент ИЛИ 6 и подаются ца вход элемента И 17,прекращая подачу импульсов от генератора 2 к счетчику адреса 8. В режиме поиска возможно маскирование. Например, можно замаскировать сигналы от блоков сравнения 2 - 2 юь подав сигналы логической единицы от регистра маски 4 на элементы ИЛИ 14 - 14 тПосле прекращения подачи тактовых импульсов на счетчик адреса 8 на адресных входах полей памяти 1 - гяур фиксируется младшая часть кода адреса. Может оказаться, что имеет место совпадение нескольких слов, хранимых в ЗУ с данными на регистре признака 3. В результате одновременно вырабатывается несколько сигналов совпадения на выходах элементов И 13 - 13, и в единицу устанавливается несколько индикаторов совпадения, расположецных в блоке хранения сигналов совпадения 5. В этом случае блок кодирования приоритета 6 генерирует код наименьшего значащего двоичного разряда (при этом считается, что входы блока 6 обозначены двоичным колом). Этот код образует старшую часть кода адреса искомого слова. Старшая часть кола адреса с выхода блока кодирования приоритета 6 подается для записи в соответствующие разряды регистра адреса 7. По сигналу с выхода элемента ИЛИ 16 блок управления режимом 10 производит перезапись в регистр адреса 7 младшей части кода адреса из счетчика адреса 8 и старшей части кода адреса с выходов блока кодирования приоритета 6. ЗУ с.выборкой по содержимому объемом И слов по сравнению с ЗУ с произвольной выборкой с единым полем памяти на 1 слов, но имеющим олин блок сравнения, дает в режиме поиска выигрыш в быстродействии в И/граз, где тг - число слов в поле памяти 1 с произвольной выборкой. Йо сравнению с ассоциативным ЗУ в предложенном ЗУ снижены стоимость бита, отношение вывод/схема и мощность рассеяния. Запоминающее устройство с выборкой по содержимому. содержащее матрицу полей памяти с произвольной выборкой, выходю которых соединены с первыми информационными входами соответствующих блоков сравнения, выходы которых соединены. со входом сигнала совпадения соответствующих элементов ИЛИ совпадения, входы маскирования элементов ИЛИ совпадения каждого столбца матрицы объединены и под690486 Соста ватель Текред О, Лу тараи 7 ВЕ И Государственного делам изобретений Москва, Ж - 36, Раув кПатентк, г. УжгорГ. Согаван Корректор А.ПодвнсноеРдавтар Л. Утекнна аз 6 М 7/46 ценно комитета ССС открытий скан наб д. д, ул. Проек/6ая,ключены к соответствующему выходу регист ра маски, вход которого подключен ко входу маски устройства, вход признака которого соединен со входом регистра признака, груп. пы выходов которого соединены со вторыми информационными входами блоков сравне. ния соответствующего столбца матрицы, выходы элементов ИЛИ совпадения каждой строки матрицы соединены с соответствующими входами элементов И объеднщ нии сигналов совпадения, выходы которых че;чез блок хранения сигналов совпадения соединены со входами блока кодирования приоритета, выходы которого соединены со входами старших разрядов регистра адреса, входы младших разрядов которого подключены к выходам счетчика адреса, которые соединены с одной группой входов мультиплексора другая группа входов которого подключена к выходам младших разрядов регистра адреса, выходы старших разрядов которого соединены со входами дешифратора, одноименные адресные входы полей памяти с произвольной выборкой объединены и подключены к соответствующему выходу мультиплексора, а управляющие выходы блока управления режимом соединены с управляющими входами регистра адреса, счетчика адреса, мультиплексора и генератора тактовых импульсов, выход которого соединенс импульсным входом элемента И прохождения счетных импульсов, выход которого соединен со счетным входом счетчика адреса,отличающееся тем, что, с целью повышениябыстродействия устройства, оно содержитэлементы ИЛИ режима поиска по числуполей памяти с произвольной выборкой иэлемент ИЛИ объединения сигналов совпадения, входя которого подключены к выходам элементов И объединения сигналов сов 1 о падения, а выход соединен с разрешающимвходом элемента И прохождения счетныхимпульсов и входом блока управления режимом, выход разрешения поиска которогосоединен со входами разрешения элементов15ИЛИ режима поиска, выход каждого изкоторых соединен с разрешающим входомсоответствующего поля памяти с произвольной выборкой, адресные входы элементовИЛИ режима поиска каждой строки матрицы объединены и подключены к соответстзо вующему выходу дешифратора.Источники информации,принятые во внимание при экспертизе1. Патент США3.540.002, кл. 340-172,5,1970.2 э2. Сопчри 1 ег Ое 61 дп, Заяцагу, 1971, с. 79

СмотретьЗаявка

2465508, 22.03.1977

ОРДЕНА ЛЕНИНА ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

АРЛАЗАРОВ ВЛАДИМИР ЛЬВОВИЧ, ВАРПАХОВСКИЙ АНДРЕЙ СОЛОМОНОВИЧ, ВОЛКОВ АЛЬБЕРТ ФЕДОРОВИЧ, ГОДУНОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ДАГУРОВА НАТАЛЬЯ ВИТАЛЬЕВНА, ЕМЕЛЬЯНОВ НИКОЛАЙ ЕВГЕНЬЕВИЧ, ЗОЛОТУХИНА ГАЛИНА МИХАЙЛОВНА, ЛИХОНИНСКИЙ ВАЛЕРИЙ СЕРГЕЕВИЧ, ЛЫСИКОВ ВИКТОР ТИХОНОВИЧ, МАКАРОВ ВАЛЕРИЙ АЛЕКСЕЕВИЧ, СОРОКИН ГЕНРИ КЛАВДИЕВИЧ

МПК / Метки

МПК: G06F 13/06

Метки: выборкой, запоминающее, содержимому

Опубликовано: 05.10.1979

Код ссылки

<a href="https://patents.su/3-690486-zapominayushhee-ustrojjstvo-s-vyborkojj-po-soderzhimomu.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с выборкой по содержимому</a>

Предыдущий патент: Устройство для контроля дешифраторов

Следующий патент: Устройство для сбора и обработки информации

Случайный патент: Способ получения -бромкарбоновых кислот ряда адамантана