Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

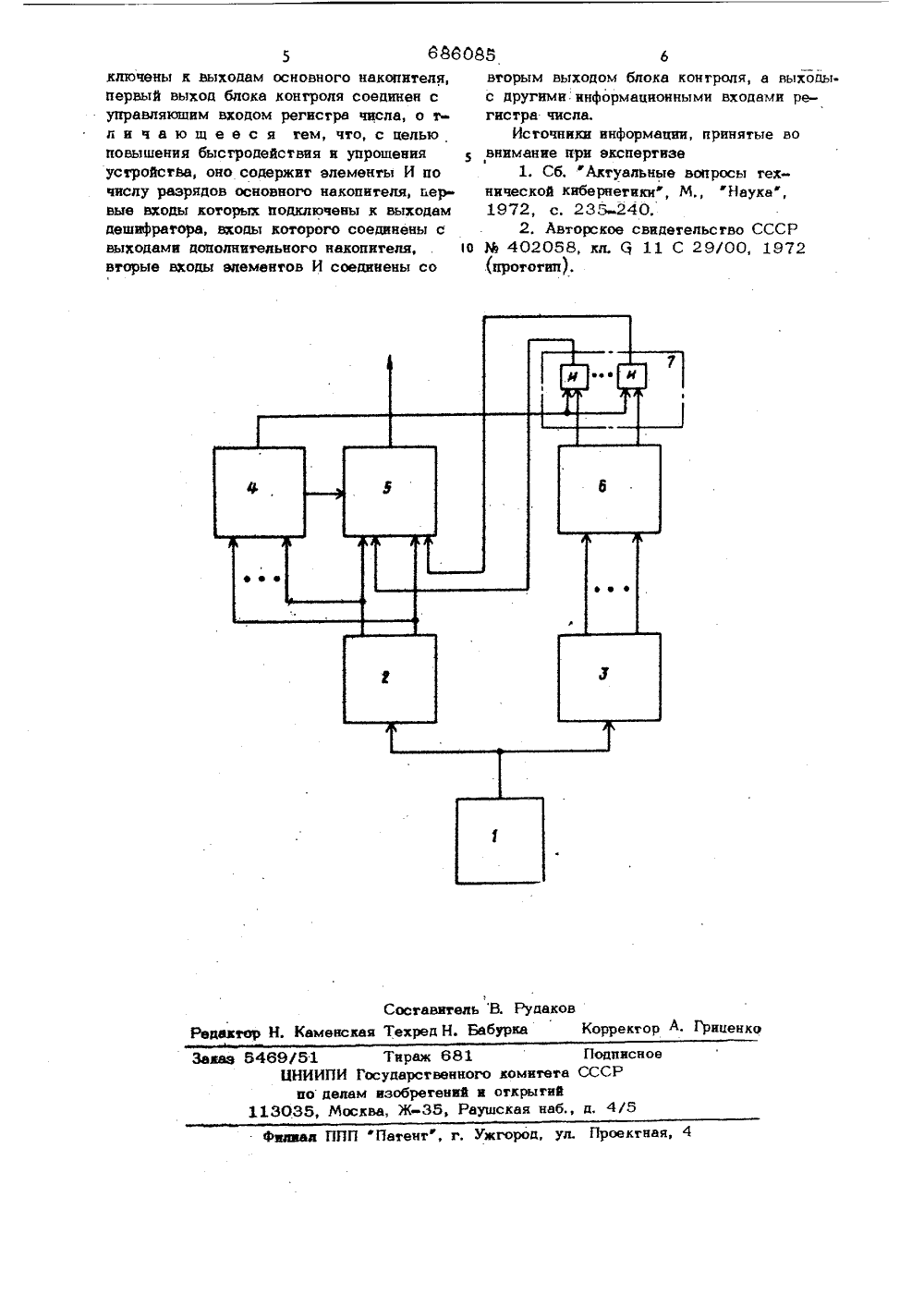

ОП " Е ИЗОБРЕТЕН ИЯ Союз СоветскихСоциалист ицесааРеспублик о 686 О 85соеднненн аявкнМ(23) Приорит еаудврствеевй канатат СССР аа делам кзобретвин к юткрнтай(72) Авторы изобретен и Култыгин, Б. Е. Глас И. Вариес и Г асовв Заявитель 54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВПЕ ОШИБО Недостатк устройстм являетнчества оборудоонтроля, а также рашения за счет ой информапии по м етогоеличеиие кол блока крремени об контрольн смгсильное уввания за счеувеличениеФорм яро мниХеммингу,Изобретение относится к области запоминаюших устройств.Известно запоминающее устройство с исправлением ошибок, содержашее регистр числа, блок контроля, основной блок намя% ти, дополнительный блок памяти и дешифратор 1. В этом устройстве осушествпя ется исправление одиночных ошибок при считывании путем сравнения контрольной информации по Хеммингу, считанной из дополнительного блока памяти одновременч но со считымнием числа из основного блока памяти, с контрольной информапией по Хеммингу, сформированной блоком кон тропя, дальнейшей дешифрвпией результата сравнения и корректированием числа в регистре числа йо результату .дешифрации..1 аиболее близким техническим решением к данному изобретению является запоминаюшее устройство с исправлением ошн бок, содержашее основной и дополнительный накопители, блок выборки адресов, дешифратор, блок контроля н регистр числе, выполненный на триГгерах со счетными входами, причем выход блока выборки адресов соединен со входами накопителей, входы блока контроля и одни из информационных входов регистра числа подключены к выходам основного накопителя, первый выход блока контроля соединен с уп равляюшим входом регистра числа 2.Недостатком этого запоминающего уст ройства является сильное увеличение количестм оборудования за счет сложного блока контроля, за счет организации резерва запоминающих элементов для замены ими дефектных запоминающих элементоь, а также при оргвнизайин полноразряь ного запоминающего устройства из одноразрядных накопителей. Другим недостатком является невозможность использования4щий вход регистра числа 5 поступает сигнал разрешения выдачи числа. Одновременно с другого выхода блока контроля 4поступает сигнал, закрывающий все вторые входы элементов И 7. В случае если блок контроля 4 фиксирует наличиеошибки, с первого выхода блока контроля4 на управляющий вход регистра числа5 поступает сигнал, запрещающий выдачу О числа. Одновременно со второго выходаблока контроля 4 поступает сигнал, открывающий вторые входы элементов И 7.Параллельно считыванию числа из основного накопителя 2 по этому же адресу происходит считывание числа из дополнительного накопителя 3, в котором хранится код номера дефектного разряда.Код номера дефектного разряда поступаетна дешифратор 6, возбуждая один нз еговыходов, связанный с первым входом соответствующего элемента И 7, Сигнал свыбранного элемента И поступает на счеьный вход того триггера регистра числа8, в котором зафиксировано наличие дефектного запоминающего элемента основного накопителя 2; при этом происходитинвертирование состояния триггера в регистре числа 5.в неисправном разряде. ЗОПосле коррекции информации в регистречисла с первого выхода блока контроля4 на управляющий вход регистра числа 5поступает сигнал, разрешающий выдачу .скорректированного числа,Предлагаемое запоминающее ус гройс т 55во с исправлением ошибок,. вызванных, дефектами накопителя, выгодно отличаемся от проглотила тем, что имеет эначительно более простую структуру, так как неимеет резерва запоминающих элементовдля замены дефектных запоминающих элементов, а также за счет того, что схемыкоррекции организованы не поразрядно, адля всего полноразрядного блока немци.45Оно имеет значительно меньшую глубинусхем коррекции, что повышает быстродействие устройства. 686085 Запоминающее устройство с исправлением ошибок, содержащее основной и дополнительный накопители, блок выборки, 55 адресов, дешифратор, блок контроля и регистр числа, причем выход блока выбор ки адресов соединен со входами накопите лей, входы блока контроля и орин иэ ии формационных входов регистра числа под накопителей, выполненных совместно сосхемами записи и воспроизведения.Целью изобретения является повышениебыстродействия н упрощение запоминающего устройства с использованием возникающих в процессе изготовления накопителей дефектных запоминающих элементов.Это достигается тем, что предлагаемое устройство содержит элементы И почислу разрядов основного накопителя, пер вые входы которых подключены к выходамдешифратора, входы которого соединены свыходами дополнительного накопителя, вто.рые входы элементов И соединены со вторым выходом блока контроля, а выходы с 1другими информационными входами регис тра чис ла.На чертеже представлена блок-схемапредложенного запоминающего устройства.ОЗапоминающее устройство содержитблок выборки адресов 1, основной некоепитель 2, дополнительный накопитель 3,блок контроля 4, регистр числа 5, выполненный на триггерах со счетным входом, дешифратор 6, элементы И 7,Первые входы элементов И 7 подключены к выходам дешифратора 6, входыкоторого соединены с выходами накопителя 3, вторые входы элементов И 7 соеливены с одним из входов блока контроля 4, а выходы - с одним иэ информационныхвходов, регистра числа 8.При этом основной накопитель 2 содержит некоторое количество дефектныхзапоминающих элементов, но.не болееодного по каждому адресу. Адреса дефектных.запоминающих элементов заранее известны и по этим же адресам в дополнительном накопителе 3 хранятся коды номеров дефектных разрядов. Йополнительный накопитель 3 дефектов не имеет,Запоминающее устройство .работаетследукяиим образом,Блок выборки адресов 1 формируеткод адреса, который одновременно посту"пает на адресные входы основного 2 идополнительного 3 накопителей. В режимесчитывания число "иэ основного накопителя 2, который содержит дефектные эапоминающие элементы, совместно с разрядом контроля по четности параллельнопоступает на блок контроля 4 и счетныевходы регистра числа 5. Блок контроля4 производит проверку правильности числа, считанного из основного накопителя2 ив случае отсутствия ошибок с одного из выходов контроля 4 на управляюФормула изобретения 15 686088оключены к выходам основного накопителя, вторым выходом блока контроля, а выходыпервый выход блока контроля соединен с с другимиинформацноннымн входами реуправляюшим входом регистра числа, о т- гистра числа.личающееся тем, что,с целью Источники информации, принятые воповышения быстродействия и упрощения 5 внимание цри экспертизеустройства, оно содержит элементы И по 1. Сб, "Актуальные вопросы гехчислу разрядов основного накопителя, пер- нической кибернегнкнф, М., "Наука,вые входы которых подключены к выходам 1972, с. 235-240,дешифратора, входы которого соединены с 2. Авторское свидетельство СССРвыходами дополнительного накопителя, . 1 О М 402058, кл.11 С 29/00, 1972вторые входы елементов И соединены со .(прототип).

СмотретьЗаявка

2605169, 13.04.1978

ПРЕДПРИЯТИЕ ПЯ А-1178

КУЛТЫГИН АНАТОЛИЙ КОНСТАНТИНОВИЧ, ГЛАСКО БОРИС ЕВГЕНЬЕВИЧ, ВАРИЕС НИНА ИОСИФОВНА, ВЛАСОВА ГАЛИНА ХРИСАНОВНА

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.09.1979

Код ссылки

<a href="https://patents.su/3-686085-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Блок выборки для интегральных запоминающих устройств с переменной длиной слова

Следующий патент: Способ динамическй поляризации ядер

Случайный патент: Вибросито