Перестраиваемое микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

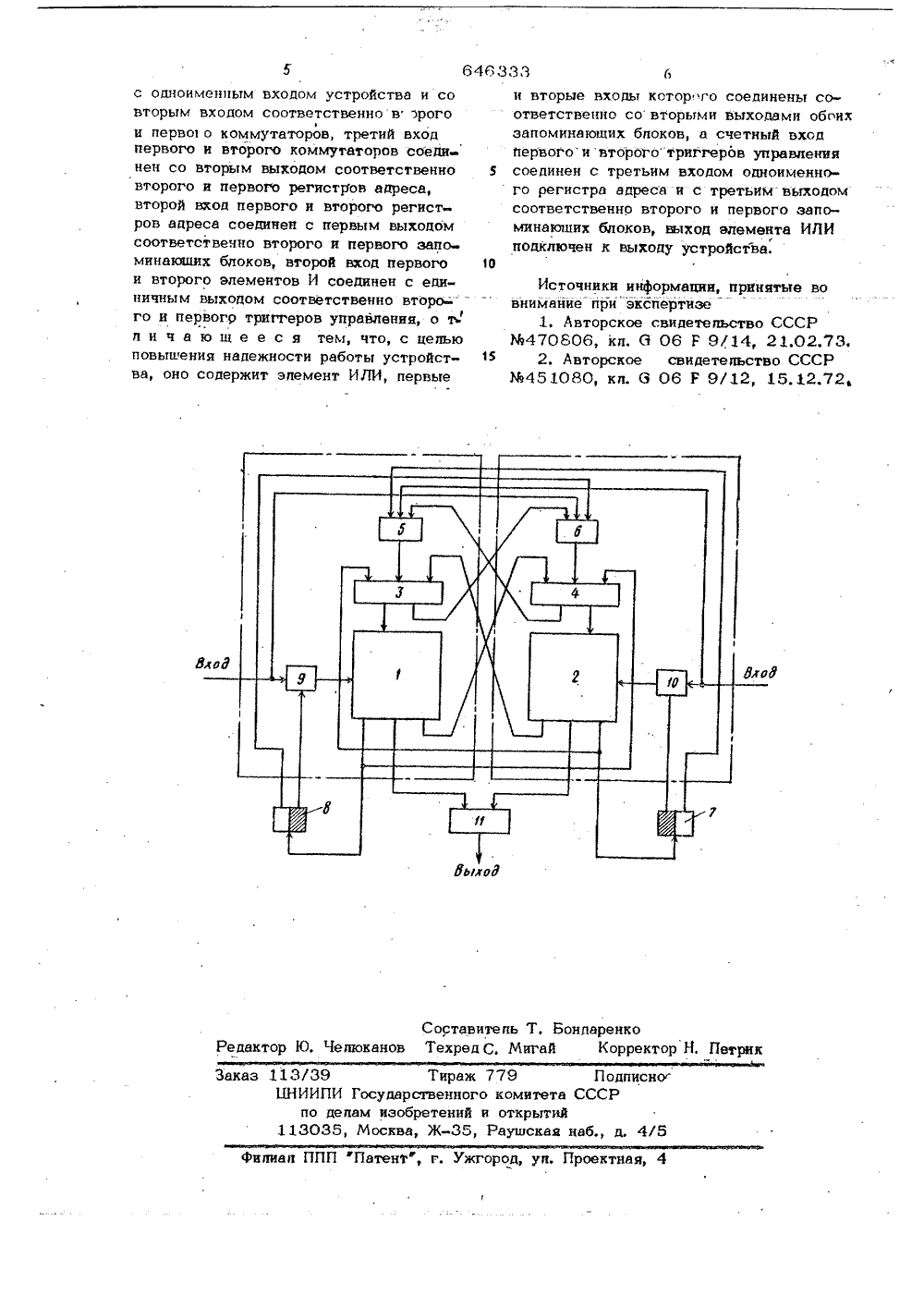

ОП ЙСАнии п 1646333 Союз Советсиик Социалистических Республик(61) Дополнительное к авт, сеид-ву 51) М. Кл т ) 241 12 8 д/18-24 22) Зая 6 Г 9/1:; заявкиприсоед 3) Прио тетковано 05,кударатааеьб юаатет СССР аа делам изобретеей и открытий5 81. 325 088,8) 2,79,5.о ия описа бликов и 08.0 та 2) Авторы изобретени Байдв и М, П. Газу(54) ПЕРЕСТРА ИВАЕМОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ мное стр мут вы- второервого с перого и выход са соеамятиЫХ динен запани дого за выходом одноименного эл нта И, го элемента вход первого и второ ен с одноименным в первый И соед ройс тв ходом уст- соответсти со вторым входоморого и первого коход первого и втор ммутв тора,го коммутвходом соото регистра нно в третийтора сое динен со вторым выно второго и перво ветстве Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления цифровых вычислительных машин,Известен микропрограммный проиессор ) с восствиовлеяием при сбоях, содержащий блок регистров, блок контроля, арифметико-логический блок, регистр адреса микрокоманд, блок сопряжения с оперативной памятью, блок управления, счетчик сбоев, блок п микрокоманд, регистр промежуточн результатов и элементы И.Недостаток известного устройства заключается в том, что восстановление работы микропрограммного процессора после сбоя происходит не сразу, а лишь после того как старший разряд счетчика сбоев устанавливается в единипу, что вносит дополнительную задержку в процесс управления обработкой информации. Кроме того, дополнительно введенное оборудование снижвет надежность системы. Известно также микропрограм устройство управлениями , содер двв запоминающих блока, два рег адреса, два элемента И, два ком тсрв и двв триггера управления,5 чем первый вход первого и второ коммутатора соединен с нулевым,ходом соответственно первоГо и го триггера управления, выход и и второго коммутатора соединен еО вым входом соответственно перв второго регистра адреса, первый первого и второго регистра адрепервым входом одноименногоающего блока, второй вход кажпоминающего блока соединен с646333 40 45 50 55 ф3адреса, второй ход первого и второго" " " регистра адреса соединен с первым выходом соответственно второго и йервогозапоминающего блока, второй входпервого и второго элемента И соединенс единичным выходом соответственновторого и первого триггера управцения,Недостаток известного устройствазакпючается в том, что в случае отказаодного из запоминающих бпоков нет возможности перестройки на работу другого запоминающего блока, что снижаетв целом функциональную надежность всего устройства.Цепью изобретения является повышение надежности работы устройства.Бпя этого в устройство введен элемент ИЛИ, первые и вторые входы которого соединены соответственно со вторыми выходами обоих запоминающихбпоков, а счетный вход первого и второго триггера управпения соединен стретьим Входом одноименного регистраадреса и с третьим выходом соответст" венно второго и первого запоминающегоблока, выход элемента ИЛИ подключен квыходу устройства.На чертеже представлена функциональная схема предлагаемого устройства.Устройство содержит первый запоминающий блок 1, второй запоминающийблок 2, первый регистр адреса 3, второй регистр адреса 4, первый коммутатор 6, второй коммутатор 6, первыйтриггер управления 7, второй триггеру 1 равпения 8, первый элемент И 9второй элемент И 10, элемент ИЛИ 11,Устройство работает следующим образом.Пусть в исходном "состоянии первыйтриггер управления 7 и второй триггер8 управления находятся в единичномсостоянии и пусть на регистре 3 (4)адреса находится адрес микрокоманды,подлежащей считыванию. Так как триггеры 7, 8 находятся в единичном состоянии,то они разрешают прохождениепоступившего на вход тактового импульса через элемент И 9 (10) и блокируюткоммутаторы 5 6. Яа третьем выходезапоминающего блока 1 (2) появляетсясчитанная микрокоманда, а адрес следующей микрокоманды заводится на регистр 4 (3) адреса другого блока. Навыходе устройства микрооперации с первого и второго блоков появляются поочередно. При отказе одного из запомвнаюших блоков, например 1, происходитперестройка на работу другого запоминающего блока 2, а именно; со второговыхода отказавшего запоминающего бпо ка 1 подается на третий вход регистра4 адреса работающего блока сигнвп,устанавливающий на этом регистре фиксированный адрес. С того же выхода загоминаюшего бпока 1 подаетс. сигнал 10 на счетный вход триггера 8, которыйустанавпивает его в нулевое состояние.Адрес спедуюшей микрокоманды, считанный с выхода запоминающего работающего блока 2, поступает на вход 15 регистра 3 адреса отказавшего блока.,Йапее этот адрес через разбпокированный коммутатор 6 работающего блокапоступает на регистр 4 адреса этогоблока. По данному адресу запоминающий блок 2 выдает микрооперацию наэлемент ИЛИ 11 и дане на выход устройства, а адрес следующей микрокоманды заводится на регистр 3 адресаотказавшего бпока.Таким образом, повышение функционапьной надежности устройства достигается тем, что в случае отказа одногоиз запоминающих блоков, другой запоминающий блок перестраиваемого микропрограммного устройства продолжаетработать и по фиксированному адресуустройство переходит на программу обработки отказа либо на подпрограммурешения данной задачи по усеченномуалгоритму. Устройство же прототип вслучае отказа одного из запоминающихустройств прекращает выдачу информации. формула изобретенияПерестраиваемое микропрограммное устройство управпения, содержащее два запоминающих блока, два регистра адреса, два элемента И, два коммутатора и два триггера управления, причем первый вход первого и второго коммутаторов соединен с нулевым выходом соответственно первого и второго триггеров управления, выход первого и второго коммутаторов соединен с первым входом соответственно первого и второго ре гистров адреса, первый выход первого и второго регистров адреса соединен с первым входом одноименного запоминающего блока, второй вход каждого запоминающего блока соединен с выходом одноименного элемента И, первый вход первого и второго элементов И соединен646333 ыюЯ Составитель Т, БондаренкоРедактор Ю. Челюканов ТехредС, Мигай Корректор Н, П7 ПодписноССР 9смите таоткрытийаушскаа 13/39 Тираж 7 ЦНИИПИ Государственного по делам изобретений и 113035, Москва, Ж, Рак д. 4/5 ППП фПатентф, г. Ужгород, ун, Проектная, 4 с одноименным входом устройства и совторым входом соответственно в рогои перво о коммутаторов, третий входпервого и второго коммутаторов соединен со вторым выходом соответственновторого и первого регистров адреса,второй вход первого и второго регистров адреса соединен с первым выходомсоответственно второго и первого запоминающих блоков, второй вход первогои второго элементов И соединен с единичным выходом соответственно второго и первогр триггеров управлении, о т-л и ч а ю щ е е с я тем, что, с цельюповьтения надежности работы устройства оно содержит элемент ИЛИ, первые н вторые входь которго соединены соответственно со вторьми выходами обликзапоминаюших блоков, а счетный входпервогои второго триггеров управления 5 соединен с третьим входом одноименного регистра адреса и с третьим выходомсоответственно второго и первого запоминающих блоков, выход элемента ИЛИГподключен к выходу устройства.1 О Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

СмотретьЗаявка

2411285, 11.10.1976

ОРДЕНА ЛЕНИНА, ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПРЕДПРИЯТИЕ ПЯ А-7160

БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, ГАЗУК МАЙЯ ПАВЛОВНА

МПК / Метки

МПК: G06F 9/12

Метки: микропрограммное, перестраиваемое

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/3-646333-perestraivaemoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Перестраиваемое микропрограммное устройство управления</a>

Предыдущий патент: Устройство управления вычислительной машины

Следующий патент: Устройство микропрограммного управления

Случайный патент: Биполярный источник эталонного напряжения