Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 646334

Авторы: Завьялов, Кузнецов, Лезин, Мараховский

Текст

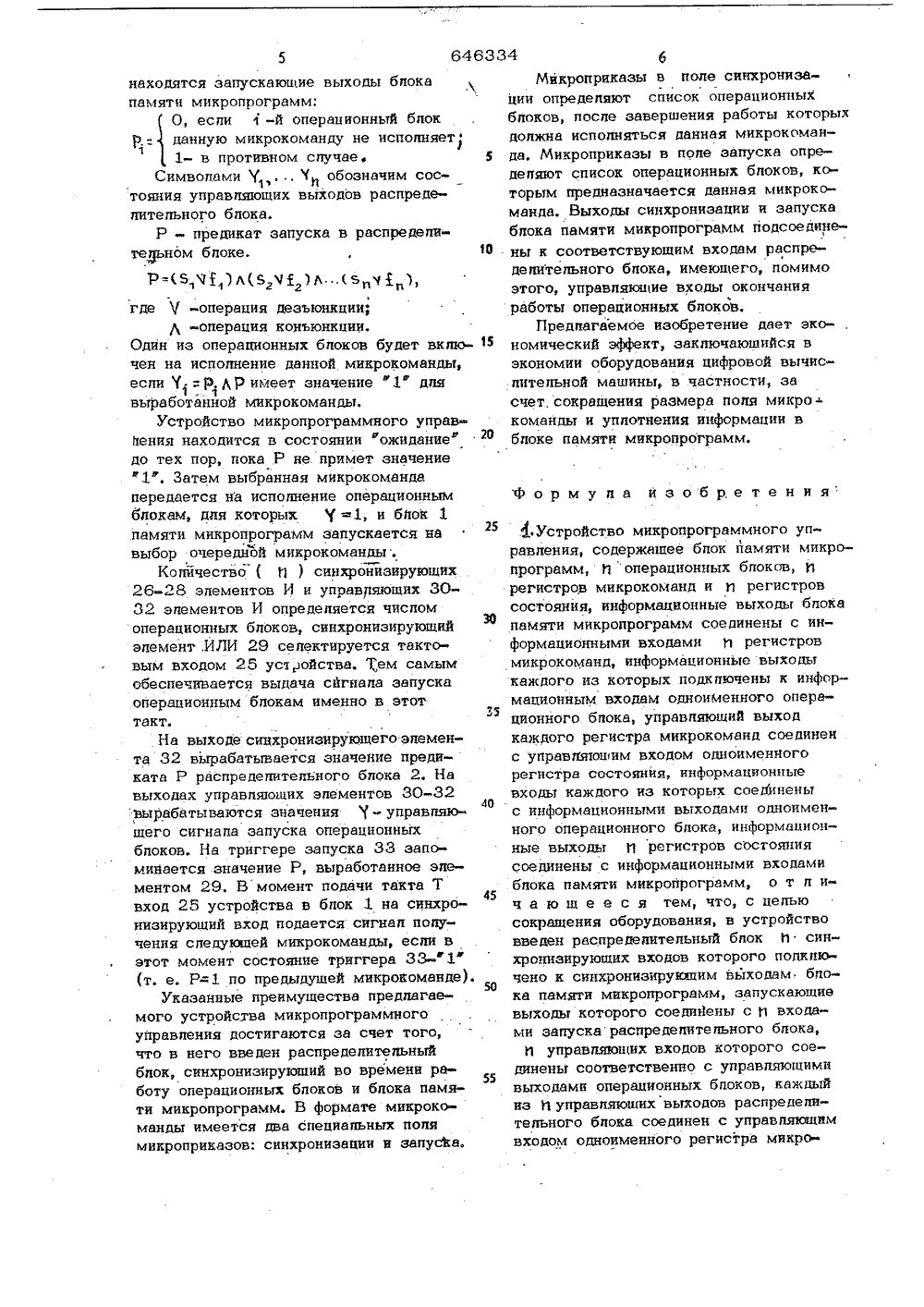

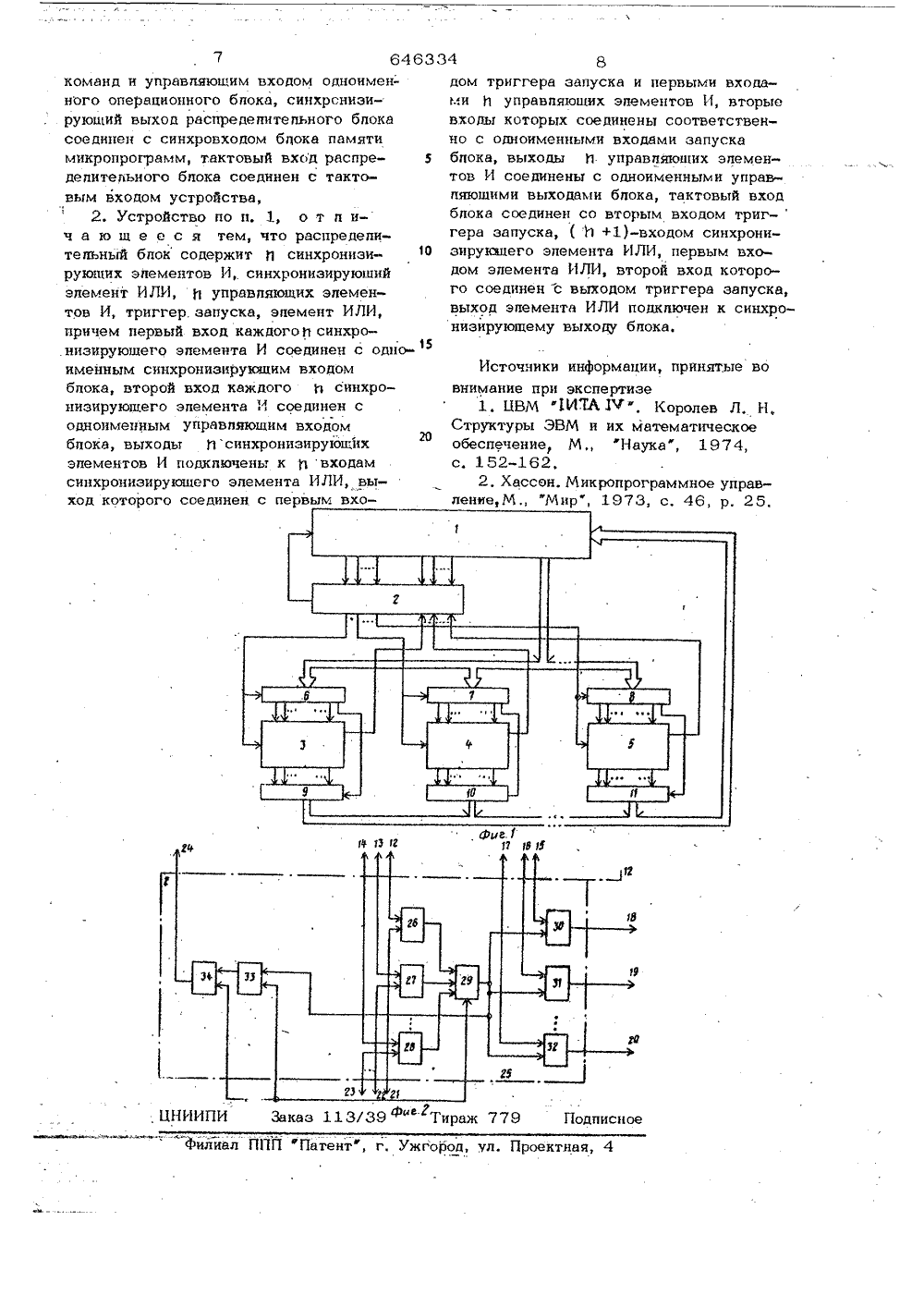

Союз Советских Социалистических Республик(51) М, К 6(21) 2373734/1 аявкиооудоротооинвй иосссроо делам иэооретви отнрытий ите(5 Опубликовано 05.02.79 БюллетеньДата опубликования описания 08,02,7 ЙК 681.3 088,8)В,П,З 72) Авторы изобретенн ялов, В. Е. Кузнецов, Г. В, Лезин и В. Б, Мараховский Государственное союзное конструкторско-технологичесбюро по проектированию счетных машин 71) Заявител ТР СТВО М ИКРОПРОГРАММНОГОПРАВЛЕНИЯ В известилепьно работзапускаютсякомандой.При этомды определимикронриказовустройств,рмат микоокома марны м числом х запускаемых сядля 1Изобретение относится к области вычислительной техники и может быть использовано при построении ЦВМ среднего быстродействия.Известна многопроцессорная цифровая вычислительная машина, содержащая устройство централизованного управления работой процессоров, которое посыпает общие команды подмножеству общего множества процессора, регистр моды дпя регистрации состояний процессоров, анапизируемых,устройствами централизо-, ванного управления, и регистр маски управляемый этим устройством и опре депяющий подмножество процессоров, выполняющих общую команду 1.Наиболее близким но техническому решению к предложенному устройству является микропрограммное устройство управления, содержащее блок памяти микропрограмм, )1 операционных блоков, и регистров микрокоманд и 1 т регистров состояний, причем информационные выходы блока памяти микропрограмм соединены с информационными входами и регистров микрокоманд, информационные выходы каждого из которых подключены к Информационным входам одноименного операционного 5 блока, управляющий выход каждого регистра микроКоманд соединен с управляющим входом одноименного регист)а состояния, информационные входы каждого из которых соединены с информационными выходами одноименного опе- рапионного блока, информапионные выходырегистров состояния соединены с информационными входами блокапамяти микропрограммЯ.5 ом. устройстве все парапюшие операционные блокиодновременно, общей микро3В ПРМ со средним ипи мапым быстродействием допустимы режимы работы, когда возможна выдача одновременных микроприказов не всем усто ройствам, могущим работать одновре менно, а лишь некоторой их части.Недостатком известного устройства в этих режимах явпяется большой объем памяти микропрограмм из-за неиспопьзования попей микрокоманды, предназначенных дпя управпения незапускаемых устройств. Цепь прелпагаемого. изобретения- сокращение оборудования.Для этого в предлагаемое устройствр введен распредепцтецьный бпок,усинхоо" низирующих входов которого подкпючено. к синхронизирующим,выходам бцока памяти микропрограмм, запускающие вы. ходы которого соединены с и входами запуска распредепитепьного бцока, Иуправпяющих входов которого соединены соответственно с управпяющими выходами операционных бпоков, каждый из Цуправпяющих выходов распредепитепьного бпока соединен с управпяющим входом одноименного регистра микрокоманд и управпяющим входом одноименного операционного блока, синхронизирующий выход распределитепьного блока соединен . с синхровходом блока памяти микропрограмм, тактовый вход распредепительного бпока соединен. с тактовым входом устройства, причем распределительный бпок содержит д -синхронизи рующих элементов И, синхронизирующий эпемент ИЛИ, И управпяющих эпементов И, триггер запуска, эпемент ИЛИ, причем первый вход каждогосинхронизирующего элемента И соединен с одноименным синхронизирующим входом блока, второй вход каждого д синхронизирующего эпемента И соединен с одноименным управпяющим входом бпока, выходы д синхронизирующих эпементов И подкпючены квходам синхронизирующего эпемента ИЛИ, выход которого соединен с первым входом триггера запуска и первыми входами б управпяющих элементов И, вторые входы которых соединены соответственно с одноименными входами запуска бпока, выходыуправляющих апементоц И соединены с одноименными управшпощими выходми бпока, тактовый вход блока соединен со вторым входом триг- гера запуска, ( и+1)-входом синхронизирующего элемента ИЛИ, первым входом эпемента ИЛИ, второй вход которого с выходом триггера запуска, выход эпемента ИЛИ подкпючен к синхронизи руюдему выходу бпока,Общая блок-схема предлагаемого устройства показана на фиг, 1. На фиг, 2 приведена структурная схема распредещ тельного блока 2.Бпок схема содержит; блок 1 памяти микропрограмм, распределительный блок 2, операционные бпоки 3, 4 5, регистры 6-8 микрокомаид, регистры 9-11 со стояний.". Структурная, схема распредепитеш ного бпака 2 содержит синхронизирую щие входи 12, 13, 14, входы запуска 15, 16, 17 управляющие выходы 18, 19, 20, управпяющие входы 21, 22, 23 синхронизирующий выход 24, тактовый вход 25 устройства, синхронизирующие 26, 27, 28 элементы И, синхронизирующий эпемент ИЛИ 29, управпяющие,ЗО, 31, 32 эпементы И, триггер запуска 33, эпемент 34 ИЛИ,Рассмотрение работы устройстваудобно начать с момента когда блоком Зф 1 памяти микропрограмм выработана дпя испоцнения очередная микрокоманда.Обозначим символами 3, 5 микроЗ 5 приказы синхронизации в попе микро- команды, поступающие на синхронизирующие входы 12, 13, 14 распределитепьного блока, причем . И - чиспо операционных бпоков; 40 - О, еспи данная микрокоманда должна исполняться по пе завершения работы 1-м операционным блоком, - 1, если момент вкпючения данной микрокоманды на исполнение не зависит от состояния 1-го операционного бпока . Символами , , обозначим состояния управляющих вйходов операцион ных бпоков: - О, еспи, з-й операционный блок занят выпопнением ранее поданной микрокоманды не обязательно предыдущей) 1- 1-й операционный бок работу закончил. Симвавми Р,Р обозначим микро приказы, в попе запуска микрокоманды6463находятся запускающие выходы блокапамяти микропрограмм;О, если 1 -й операционный блокр.- данную микрокоманду не исполняет ф1- в противном случае5Символами У, ., Ч обозначим сос 1тояния управляющих выходов распределительного блока.Р - предикат запуска в распределительном блоке,1 ОР=СЬ:,Ч 11 л(ьмХ )Л "1 эпчХр)где 7 -операция деэъюнкции;д -операция конъюнкции.Один из операционных блоков будет вклю-чен на исполнение данной микрокоманды,если У =Р ЛР имеет значение 1 длявыработанной микрокоманды,Устройство микропрограммного управления находится в состоянии "ожидание" 0до тех пор, пока Р не примет значение"1". Затем выбранная микрокомвндапередается на исполнение операционнымблокам, для которых1, и блок 1памяти микропрограмм запускается навыбор очередной микрокоманды .Колйчество ( И ) синхронизирующих .26-28 элементов И и управляющих 3032 элементов И определяется числомоперационных блоков, синхрониэирующийэлемент,ИЛИ 29 селектируется тактовым входом 25 уст,эойства, ем самымобеспечивается выдача сигнала запускаоперационным блокам именно в этот7такт.На выходе синхронизирующего элемента 32 вырабатывается значение предиката Р распределительного блока 2. Навыходах управляющих элементов 30-32вырабатываются значения- управпяю 40щего сигнала запуска операционныхблоков. На триггере запуска 33 запоминается значение Р, выработанное элементом 29. Вмомент подачи такта Твход 25 устройства в блок 1 на синхро 45ниэирующий вход подается сигнал попучения слецуквпей микрокомвнды, если вэтот момент состояние триггера 33-1(т. е. Рд 1 по предыдущей микрокоманде).50Укаэанные преимущества предлагаемого устройства микропрограммногоуправления достигаются за счет того,что в него введен распределительныйблок, синхронизируюший во времени работу операционных блоков и блока памяти микропрограмм, В формате микрокоманды имеется цва специальных полямикроприказов: синхронизации и запуска. 34 бМикроприказы в поле синхронизации определяют список операционных блоков, после завершения работы которыя должна исполняться данная микрокоманда. Микроприказы в поле запуска опредеипот список операционных блоков, которым предназначается данная микрокоманда. Выходы синхронизации и запуска блока памяти микропрограмм подсоединены к соответствующим входам распределительного блока, имеющего, помимо этого, управляющие входы окончания работы операционных блоков.Предлагаемое изобретение дает экономический эффект, заключающийся в экономии оборудования цифровой вычислительной машины, в частностиэа счет. сокращения размера поля микро команды и уплотнения информации в блоке памяти микропрограмм,Формула изобретения:3,.Устройство микропрограммного управления, содержащее блок памяти микропрограмм, И операционных блоков,регистров микрокоманд и П регистров состояния, информационные выходы блока памяти микропрограмм соединены с информационными входамирегистров микрокоманд, информационные выходы каждого иэ которых подключены к информационным входам одноименного операционного блока, управляющий выход каждого регистра микрокоманд соединен с управипошим входом одноименного регистра состояния, информационные входы каждого из которых соединены с информационными выходами Одноименного операционного блока, информационные выходы И регистров состояния соединены с информационными входами блока памяти микропрограмм, о т л ич а ю ш е е с я тем, что, с целью сокращения оборудования, в устройство введен распределительный блок и синхронизирующих входов которого подключено к синхронизируюшим выходам, блока памяти микропрограмм, запускающие выходы которого соединены с д входа ми запуска распределительного блока, и управляющих входов которого соединены соответственно с управляющими выходами операционных блоков, каждый из и управляюц(их выходов распределительного блока соединен с управляющим входом одноименного регистра микрс646334 НИИПИ Заказ 113/39 Ф"Тираж 77 Подписное филиал ППП ент", г. Ужгород, ул тная команд и управпяющим входом одноимен-ного операционного блока, синхрснизи. руюций выход распределительного блока соединен с синхровходом блока памяти микропрограмм, тактовый вход распределительного блока соединен с тактовым входом устройства,2. Устройство по п. 1, о т и ич а ю ш е е с я тем, что распределительный блок содержит и синхронизируюших элементов И, синхронизируюший элемент ИЛИ,управляющих элементов И, триггер. запуска, эпемент ИЛИ, причем первый вход каждого И синхро.низирующего эпемента И соединен с одноименным синхронизируюшим входом блока, второй вход каждого Ь синхронизируюшего элемента И соединен с одноименным управляющим входом блока, выходы и синхронизируюших элементов И подключены к 1 входам синхронизируюшего элемента ИЛИ, выход которого соединен. с первым входом триггера запуска и первыми входами и управляющих элементов И, вторыевходы которых соединены соответственно с одноименными входами запуска5 блока, выходы и. управпяюших элементов И соединены с одноименными управпяюшими выходами блока, тактовый входблока соединен со вторым входом триг-гера запуска, ( И +1)-входом синхрони 1 О зируюшего элемента ИЛИ, первым входом элемента ИЛИ, второй вход которого соединен с выходом триггера запуска,выход эпемента ИЛИ подкпючен к синхронизируюшему выходу блока,5 Источники информации, принятые во внимание при экспертизе1, БВМ "1 ИТА Г", Королев Л, Н Структуры ЭВМ и их математическое обеспечение, М Н ука", 1974, с, 152-162,2. Хассон. Микропрограммное управление,М., "Мир", 1973, с. 46, р. 25.

СмотретьЗаявка

2373734, 21.06.1976

ГОСУДАРСТВЕННОЕ СОЮЗНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО ПО ПРОЕКТИРОВАНИЮ СЧЕТНЫХ МАШИН

ЗАВЬЯЛОВ ВАЛЕРИЙ ПЕТРОВИЧ, КУЗНЕЦОВ ВАЛЕНТИН ЕВГЕНЬЕВИЧ, ЛЕЗИН ГЕНРИХ ВАЛЕРИЕВИЧ, МАРАХОВСКИЙ ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммного

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/4-646334-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Перестраиваемое микропрограммное устройство управления

Следующий патент: Запоминающее устройство

Случайный патент: Способ определения гексенала