Тестовый модуль для контроля параметров интегральных микросхем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

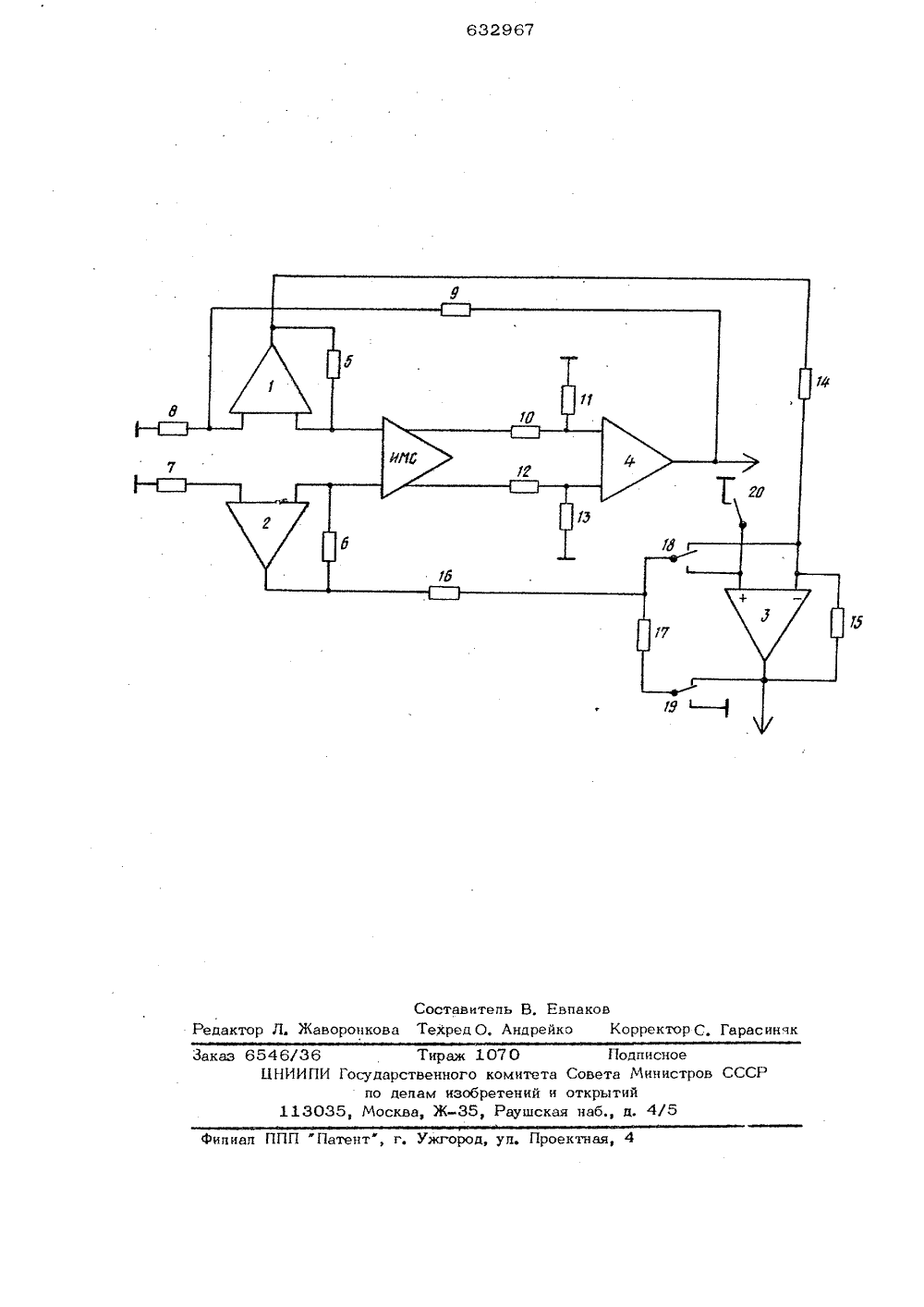

О П "В Е ИЗОБРЕТЕН ИЯ Союз Советских Социалистиыеских Республик) Заявлеио 28.04.77 (21) 2480157/18-21 К 31/2 явки .Ме кударственай намнт Совета Инннстроа ССС аа делам нзобрвтеннйн атнрытнй 3) УДК 621 31 .7 99(088,8 1,78,5 ю нь Ме 42 ания описания 16.117КОНТРОЛЯ ПАРАМЕТРОВМИКРОСХЕМ депцтепя напряжения, через депцтепь напряжения - с выходом второго операциочного усипитепя первые выходныеклеммы первого, второго и третьего перекпючатепей соединены соответственно собщей шиной, цнвертирующим входом третьего операционного усипитепя и выходом третьего операционного усилителя,а вторые выходные кпеммы второго итретьего переключателей соединены соответственно с цецнвертирующим входомтретьего операционного усипитепя ц общей шиной. к области элеи может быт вах дпя контропмикросхем.технической сущности явпяется известный тестовый ь дупь дня контроля параметров цнтеграпьных микросхем цо авт. св, Ее 570856, содержащий четыре операционных усилите пя, резистцвные детали напряжения и резистор температурной стабипиэацци.Недостатком этого тестового модупя явпяется невозможность измерения средн го входного тока смешения.цепь изобретения - расширение фуцкционапьных воэможностей путем обеспечения измерения среднего входного тока На чертеже приведена ма тестового модуля. руктурна Тестовый моаупь дпя метров ицтеграпьцых ми четыре операционных усц резисторы 5,6, резистор стабипцэаццц 7, депитепь эи на резисторах 8,9, че напряжения ца резисторах 13, 14, 15, 16, 17 и т тактов 18, 19, 20,росхе пцтеп темп обрат тыре10,конт ров интеграпьных микротрц перекпючатепя причем мы первого, второго и треючатепей соединены соответмет а схем вве входные тьего пе(45) Дата опублик Изобретение относитроизмерцтельной техникцспопьзовацо в устройстпинейцых ицтеграпьныхНацбопее бпиэким по мый тестовый модупь дпя цвертирующцм входом треонного усилителя, выходом ня парам содержит1-4, ратурной ной свядепитепя ппы кон632967 Тестовый модуль дпя контроля параметров интегральных микросхем работает спедуюшим образом. Режим испытуемой интегральной микросхемы (на чертеже не показана) устанавливается опера- У ционным усилителем 4, устанавпиваюшим равенство входных напряжений испытуемой интегральной микросхемы. Так как операционные усилители 1 и 2 идентичны и согласованы по своим параметрам, то . Ф к входам испытуемой интегральной микросхемы приложено лишь напряжение смещения нуляс и выходное напряжение операционного усилителя 1 равно а смРь -5 СМЬТестовый модуль дпя контроля параф метров интегральных микросхем по авт.св.570856, о т и и ч а ю ш и й с ятем, что, с целью расширения функциональных возможностей путем обеспечения измерения среднего тока, в него введены фф три переключателя, причем. входные клеммы первого, второго и третьего переклю. чателей соединены соответственно с неинвертируюшим входом третьего операцион: ного усилителя, выходом делителя напряжения, через депитепь напряжения - свыходом второго операционного усилителя, первые выходные клеммы первого,второго и третьего переключателей соединены соответственно с обшей шиной, ин 4. вертируюшим входом третьего операционного усилителя и выходом третьего опе,рационного усилителя, а вторые выходныеклеммы второго и третьего перекпючате 43лей соединены соответственно снеинвертируюшим входом третьего операционногоусилителя и обшей шиной,1 са фосеа 2 где Чд = 100 Р 8Выходные напряжения Б и Ез на выходах операционных усилителей 1 и 2 рав- ны где 75 = Й, - -ДНа выходе операционного усилителя 3 действует напряжение Е. а так какй 14=Ч 15 = Я 1 о = Я 17( ц 1. ЕЕаКа.1 1 - -е -" - ц Таким образом, выходное напряжение операционного усилителя 3 прямо пропорционально лопусумме входных токов,При другом положении контактов контактных групп 18, 19, 20 производитсяизмерение разности входных токов,Введение трех контактных групп позвопяет повысить универсальность тестового модуля, депаетего пригоднымдляиэмерения всех типов операционных и дифференциальных усилителей.Предпагаемый тестовый модуль нетребует последовательного сбора тестовыхсхем дпя измерения параметров интегральных микросхем, не требует коммутацииих измеритепьных цепей,приводящих кувепичению временных задержек, обусловленных переходными процессами в цепяхкоррекция, дает возможность измеренияпараметров интегральных микросхем беззаполнения промежуточных результатови вычислений,формула изобретения70 За 46/36ЦНИИПИ исноеинистров ССС ипиап ППП "Патент", г, Ужгород, ул. Проектная,Тираж Государственного по делам изоб 5, Москва, Ж

СмотретьЗаявка

2480157, 28.04.1977

ПРЕДПРИЯТИЕ ПЯ А-7501

ДУБОВИС ВЛАДИМИР МОИСЕЕВИЧ, АНТОНОВ ЮРИЙ ИВАНОВИЧ, ЧЕРНЫШЕВ ЮРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G01R 31/319

Метки: интегральных, микросхем, модуль, параметров, тестовый

Опубликовано: 15.11.1978

Код ссылки

<a href="https://patents.su/3-632967-testovyjj-modul-dlya-kontrolya-parametrov-integralnykh-mikroskhem.html" target="_blank" rel="follow" title="База патентов СССР">Тестовый модуль для контроля параметров интегральных микросхем</a>

Предыдущий патент: Способ определения места повреждения кабеля

Следующий патент: Устройство для измерения параметров морского волнения

Случайный патент: Стекловаренная ванная печь