Тестовый модуль для контроля параметров интегральных микросхем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

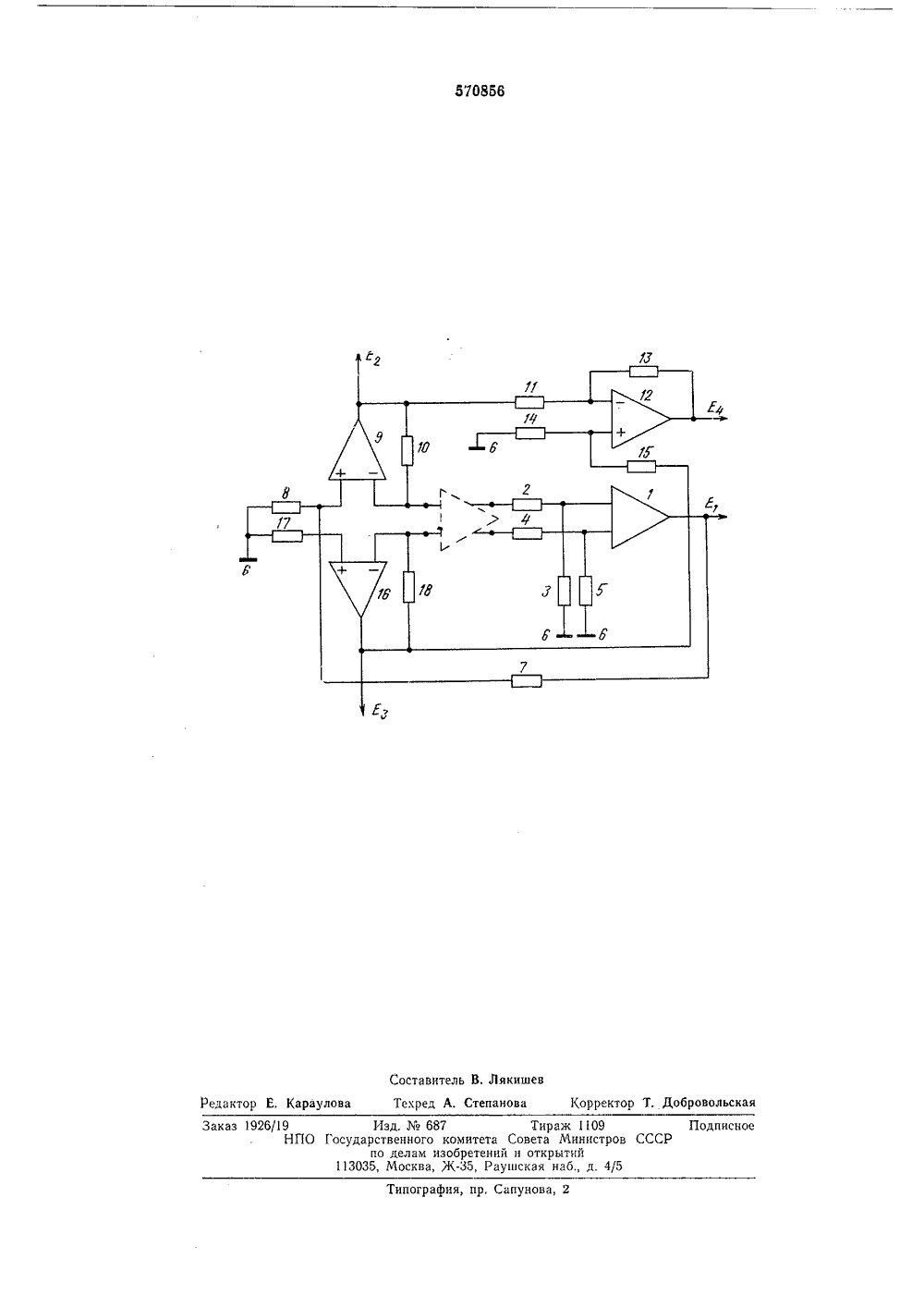

Оойооюз;,. 1 мйтбктно-тем пиеской 6;цлиотека МБА р 70856 ОПИСАНИЕ ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ,(22) Заявл 29.04.76 51) М. Кл 2 б 01 К 31/28 киприсоединением дарственнын комит 3) Пр ет овета Министров СССпо делам изобретений и открытий публиковано 30,08.77. Бюллетень32 3) УДК 621.318.799(088.8) 3.09.7 ан ткования та оп(71) Заявите 4) ТЕСТОВЫЙ МОДУЛЬ ДЛЯ КОНТРОЛЯ ПАРАМЕТР ИНТЕГРАЛЬНЫХ МИКРОСХЕМ2 турная схехя.параметровусилительлителю на, подклю. дами нспыструк модх роля держи ыкд Зи 4, у выхо Изобретение относится к электронной технике и может использоваться при контроле линейных микросхем в условиях серийного производства в комплексе с автоматическим измерительным оборудованием.Известен тестовый модуль для контроля параметров микросхем с дифференциальным выходом, содержащий вспомогательный усилитель, входы которого подключены к резисторным делителям напряжения, включенным соответственно между выходами испытуемой микросхемы и общей шиной, делитель обратной связи, включенный между выходом вспомогательного усилителя и общей шиной, резистор температурной стабилизации и измерительные резисторы, параллельно которым подключены переключатели.Однако этот тестовый модуль имеет низкое быстродействие из-за коммутации входных цепей испытуемой микросхемы при сборе тестовых схем для контроля отдельных параметров микросхемы, которая приводит к увеличению временных задержек на тестах, обусловленнных переходными процессами в це. пях коррекции и требует применения в сос. таве автоматизированного измерительного оборудования дорогостоящего электронно-вычислительного устройства,Цель изобретения - исключение коммутации цепей контролируемой интегральной микросхемы. Для этого в предлагаемый тестовый модульдля контроля параметров интегральных микросхем введены два дополнительных делителя напряжения, два резистора и три операцион ных усилителя, неинвертирующий вход первого из которых подключен к делителю обратной связи, неинвертирующий вход второго через резистор температурной стабилизации подключен к общей шине, а инвертирующие 10 входы первого и второго операционных усилителей подсоединены к соответствующим входам контролируемой микросхемы и через резисторы к выходам первого и второго операционных усилителей, причем один из входов 15 третьего операционного усилителя подключенк одному из дополнительных делителей напряжения, включенному между выходами первого и третьего операционных усилителей, а второй вход третьего операционного усилите ля подключен к второму дополнительному делителю напряжения, включенному между выходом второго операционного усилителя и общей шиной. 25 На чертеже представленама предлагаемого тестовогоТестовый модуль для континтегральных микросхем со1, входы которого подключен30 пряжения на резисторах 2,ченных соответственно межд5 10 20 25 ц с Ез - вх 1(91 Ез - Увх, , И 1 туемой микросхемы и общей шиной 6; резистор 7, подключенный к выходу вспомогательного усилителя, и резистор 8, подключенный к общей шине, образуют делитель обратной связи, к которому подключен неинвертирующий вход операционного усилителя 9, инвертирующий вход которого подключен к одному из входов испытуемой интегральной микросхемы и через резистор 10 к выходу операционного усилителя 9, к которому через резистор 11 подключен вход операционного усилителя 12, соединенный с выходом через резистор 13, а другой вход - к делителю напряжения на резисторах 14 и 15, включенному между общей шиной и выходом операционного усилителя 16, неинвертирующий вход которого подключен через резистор 17 температурной стабилизации к общей шине, а инвертирующий вход - к второму входу испытуемой интегральной микросхемы и через резистор 18 к выходу.Режим испытуемой интегральной микросхемы определяется усилителем 1, устанавливающим равенство выходных напряжений испытуемой интегральной микросхемы. Испытуемая интегральная микросхема и усилитель 1 охвачены глубокой отрицательной обратной связью по постоянному току посредством резисторов 7 и 8, Входные токи сбалансированной испытуемой микросхемы поступают соответственно на инвертирующие входы операционных усилителей 9 и 16, которые соединены с выходами через резисторы 10 и 18,Если усилители 9 и 16 идентичны и согласованы по своим параметрам, то к входам испытуемой микросхемы приложено напряжение смещения нуля и выходном напряжение на выходе вспомогательного усилителя равно причем сопротивление резистора Яб= 1 ООЯ 7. Выходные напряжения Ез и Ез на выходах операционных усилителей 9 и 16 равны Выходное напряжение Ез на выходе усилителя 12, осуществляющего вычитание напряжений Е, и Ез, определяется выражением 19 (1+ 1 з 1 Е %194 3(1 4 19 11 Р 11 Если выбрать Я 1 о=Р 1 з, Р 14=й 1 з и Й 11=Р 1 з,то 30 35 40 45 50 55 4Ев: ( вхЙ) ( 1 вх, Р):- (вх, вх,) й -вхйПолучаем значения параметров одновременно: на выходе вспомогательного усилителя 1 - напряжение, равное - 100 Уввна выходах усилителей 9 и 16 - напряжения, пропорциональные входным токам смещения, на вы. ходе усилителя 12 - напряжение, пропорцио. нальное разности входных токов, исключая коммутацию входных цепей испытуемой мик. росхемы.Тестовый модуль не требует последовательного сбора тестовых схем для измерения указанных выше параметров микросхемы, не имеет коммутирующих элементов для коммутации входных цепей микросхемы, приводящих к увеличению временных задержек, обусловленных переходными процессами в цепях коррекции, дает возможность измерения параметров микросхемы без запоминания промежуточных результатов и вычислений. Формула изобретения Тестовый модуль для контроля параметров интегральных микросхем, содержащий усилитель, входы которого подключены к делителям напряжения, включенным соответственно между выходами испытуемой микросхемы и общей шиной, делитель обратной связи, включенный между выходом усилителя и общей шиной, и резистор температурной стабилизации, отл и ч а ю щи й ся тем, что, с целью исключения коммутаций цепей контролируемой интегральной микросхемы, в него введены два дополнительных делителя напряжения, два резистора и три операционных усилителя, неинвертирующий вход первого из которых подключен к делителю обратной связи, неинвертирующий вход второго через резистор температурной стабилизации подключен к общей шине, а инвертирующие входы первого и второго операционных усилителей подсоединены к соответствующим входам контролируемой интегральной микросхемы и через резисторы к выходам первого и второго операционных усилителей, причем один из входов третьего операционного усилителя подключен к одному из дополнительных делителей напряжения, включенному между выходами первого и третьего операционных усилителей, а второй вход третьего операционного усилителя подключен к второму дополнительному делителю напряжения, включенному между выходом второго операционного усилителя и общей шиной.6708 бб Составитель В. Лякишев Техред А. Степанова Корректор Т. Добровольская Редактор Е, Караулова Типография, пр, Сапунова, 2 Заказ 1926/19 Изд.687 Тираж 1109 Подписное НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 45

СмотретьЗаявка

2351714, 29.04.1976

ПРЕДПРИЯТИЕ ПЯ А-7501

ДУБОВИС ВЛАДИМИР МОИСЕЕВИЧ, АНТОНОВ ЮРИЙ ИВАНОВИЧ, ЧЕРНЫШОВ ЮРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G01R 31/303

Метки: интегральных, микросхем, модуль, параметров, тестовый

Опубликовано: 30.08.1977

Код ссылки

<a href="https://patents.su/3-570856-testovyjj-modul-dlya-kontrolya-parametrov-integralnykh-mikroskhem.html" target="_blank" rel="follow" title="База патентов СССР">Тестовый модуль для контроля параметров интегральных микросхем</a>

Предыдущий патент: Устройство для автоматического контроля параметров радиоэлектронной аппаратуры

Следующий патент: Датчик градиента магнитного поля

Случайный патент: Устройство для образования буронабивных свай