Преобразователь двоичных чисел в двоично-десятичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 503234

Авторы: Заболотский, Цыпленков

Текст

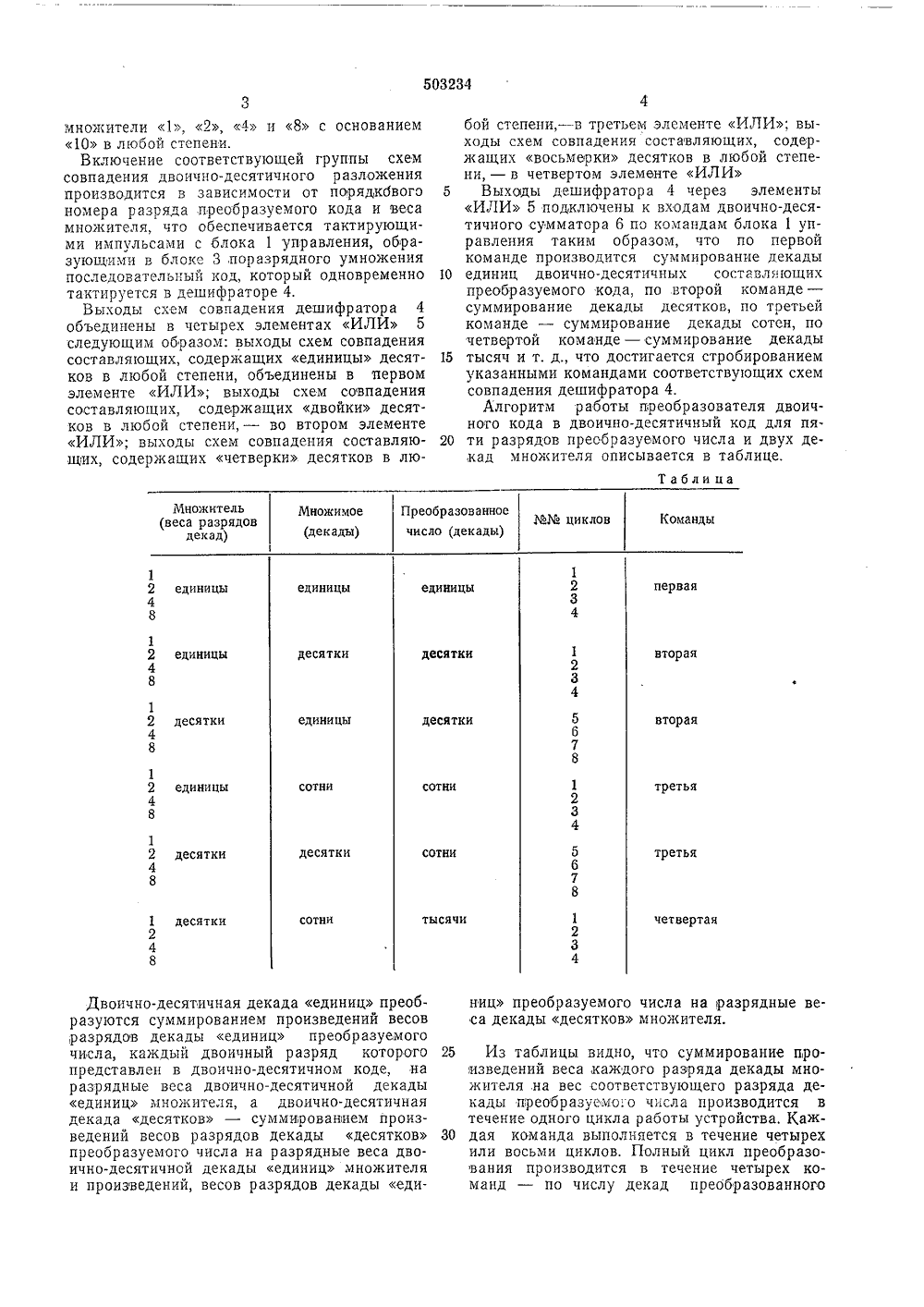

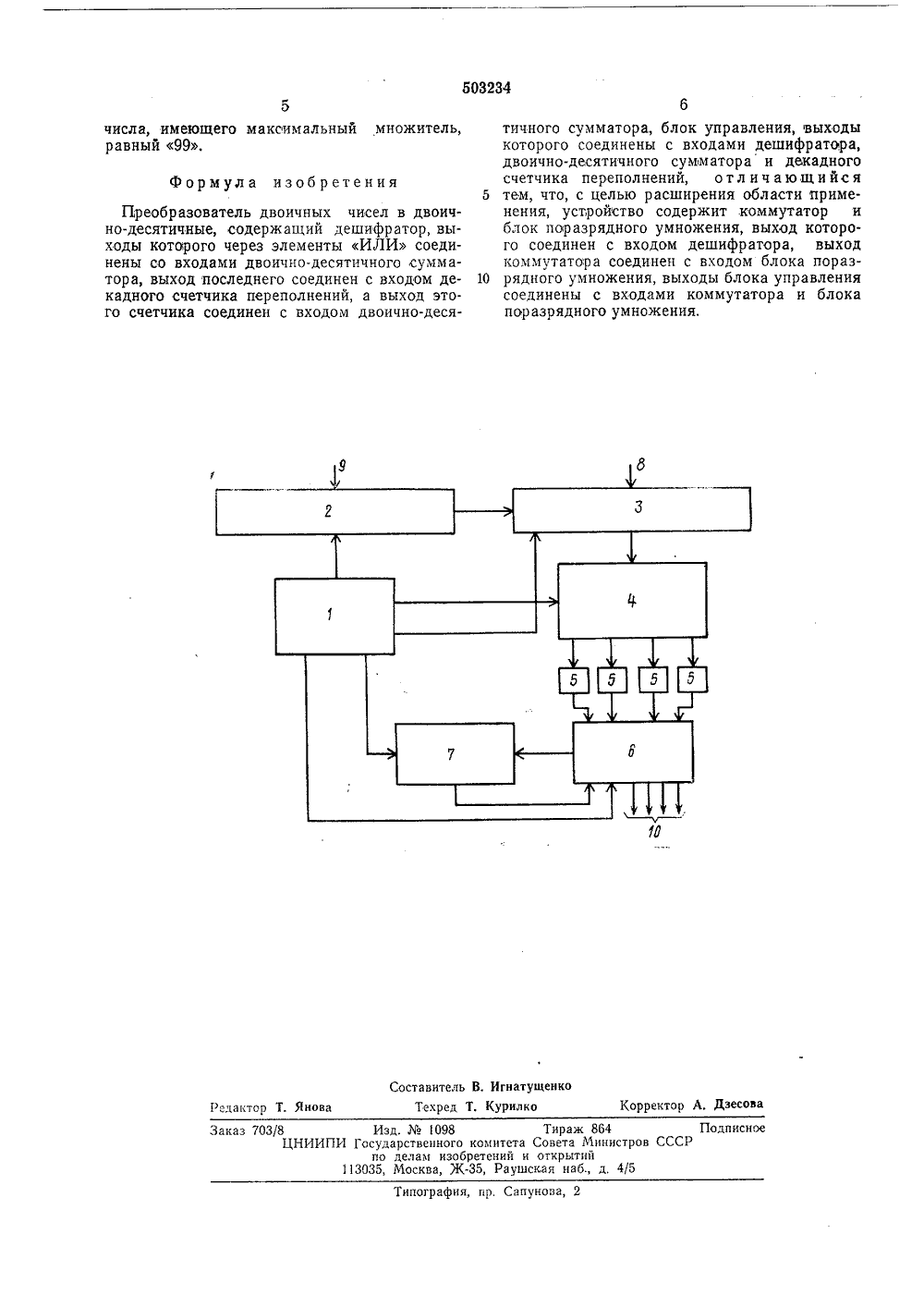

5 ОЗ 2 З 4 ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Совотокик Социалистическик) М, Клзб 06 Г 5/02 22) Заявлено 27.05.74 (21) 2027375/18-2 рисоединением заявки сударственныи комите 23) П итет авета Министров ССС о делам изобретений и открытий публиковано 15.02.76, Бюллетень6 ата опубликования описания 19.04.76 81,825.53088.8) 3)) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЕ томати значен лв Н чертеже поель.длагаемый1 управлендиого умноИЛИ 5, дадный счетного числа,но-десятичн зоватПре блок разря тыб, дек двоич двоич Изобретение относится к области ав ки и вычислительной техники и предна о для преобразования кодов.Известен преобразователь двоичных чисе двоично-десятичные, содержащий дешифратор, выходы которого через элементы ИЛИ соединены с входами двоично-десятичного сумматора, декадный счетчик переполненный и блок управления,Известный преобразователь преобразовывает числа только с одним, заранее заданным масштабным коэффициентом,С целью расширения области применения предлагаемый преобразователь содержит коммутатор и блок поразрядного умножения, выход которого соединен с входом дешифратора, выход коммутатора соединен с входом блока поразрядного умножения, выходы блока управления соединены с входами коммутатора и блока поразрядного умножения. ан предлагаемыи преобра преобразователь содержит ия, коммутатор 2, блок 3 пожения, дешифратор 4, элеменвоично-десятичный сумматор чик 7 переполнений, вход 8 вход 9 множителя, выход 10 ого кода,Устройство работает следующим образом.Двоична-десятичный код множителя, являющийся масштабным коэффициентом, поступает через вход 9 на коммутатор 2, который по следовательно коммутирует двоичные разрядыдвоично-десятичных декад множителя на блок 3 поразрядного умножения; те разряды декад множителя, которые имеют одинаковый вес (1, 2, 4, 8), объединяются в коммута торе 2 по схеме дизъюнкции.В блоке 3 поразрядного умножения производится умножение каждого разряда преобразуемого двоичного числа, поступающего через вход 8 на соответствующие разряды декад 15 множителя.Полученные произведения в виде последовательного двоичного кода поступают в дешифратор 4 двоично-десятичных составляющих (и+ 3) разрядов двоичного числа, где и - 20 разрядность преобразуемого двоичного кода.Дешифратор 4 содержит количество группсхем совпадений, равное числу (и + 3) разрядов .двоичного числа.Число схем совпадений в каждой группе оп ределяется количеством двоично-десятичныхсоставляющих соответствующих разрядов двоичного числа.Дешифратор 4 раскладывает на двоично-десятичные составляющие любой разряд преоб разуемого двоичного числа, умноженного на(декады) Команды ММ циклов 12 единицы 48 первая единицы единицы 12 единицы 48 десятки десятки вторая 1 2 десятки 48 единицы десятки вторая 12 единицы 48 сотни сотни третья 12 десятки 48 десятки сотни третья 1 десятки 248 сотни тысячи четвертая множители 1, 2, 4 и 8 с основанием 10 в любой степени.Включение соответствующей группы схем совпадения двоично-десятичного разложения производится в зависимости от порядкбвого номера разряда преобразуемого кода и веса множителя, что обеспечивается тактирующими импульсами с блока 1 управления, образующими в блоке З,поразрядного умножения последовательный код, который одновременно тактируется в дешифраторе 4,Выходы схем совпадения дешифратора 4 объединены в четырех элементах ИЛИ 5 следующим образом: выходы схем совпадения составляющих, содержащих единицы десятков в любой степени, объединены в первом элементе ИЛИ; выходы схем совпадения составляющих, содержащих двойки десятков в любой степени, - во втором элементе ИЛИ; выходы схем совпадения составляющих, содержащих четверки десятков в люДвоично-десятичная декада единиц преобразуются суммированием произведений весов ,разрядов декады единиц преобразуемого числа, каждый двоичный разряд которото представлен в двоично-десятичном коде, на разрядные веса двоично-десятичной декады единиц множителя, а двоично-десятичная декада десятков - суммированием произведений весов разрядов декады десятков преобразуемого числа на разрядные веса двоично-десятичной декады единиц множителя и произведений, весов разрядов декады едибой степени, - в третьем элементе ИЛИ; выходы схем совпадения составляющих, содержащих восьмерки десятков в любой степени, - в четвертом элементе ИЛИ5 Выходы дешифратора 4 через элементыИЛИ 5 подключены к входам двоично-десятичного сумматора 6 по командам блока 1 управления таким образом, что по первой команде производится суммирование декады 10 единиц двоично-десятичных составляющихпреобразуемого кода, по второй команде - суммирование декады десятков, по третьей команде - суммирование декады сотен, по четвертой команде - суммирование декады 15 тысяч и т. д., что достигается стробированиемуказанными командами соответствующих схем совпадения дешифратора 4.Алгоритм работы преобразователя двоичного кода в двоично-десятичный код для пя ти разрядов преобразуемого числа и двух де,кад множителя описывается в таблице. ниц преобразуемого числа на разрядные веса декады десятков множителя,25 Из таблицы видно, что суммирование про:изведений веса, каждого разряда декады множителя на вес соответствующего разряда декады преобразуемо;о числа производится в течение одного цикла работы устройства, Каж дая команда выполняется в течение четырехили восьми циклов. Полный цикл преобразования производится в течение четырех команд - по числу декад преобразованного503234 Формула изобретения Составитель В. Игнатущенкоктар Т. Янова Техред Т. Курилко Корректор А, Дзесов аз 70 Подписноеов СССР Тираж 864а Совета Миниси открытийшская наб., д, 4 Изд.1098 1 Государственного комите по делам изобретений 113035, Москва, Ж, РаИ Типография, пр. Сапунова числа, имеющего максимальный множитель,равный 99,Преобразователь двоичных чисел в двоично-десятичные, содержа 1 ций дешифратор, выходы которого через элементы ИЛИ соединены со входами двоично-десятичного сумматора, выход последнего соединен с входом декадного счетчика переполнений, а выход этого счетчика соединен с входом двоично-десятичного сумматора, блок управления, выходы которого соединены с входами дешифратора, двоично-десятичного сумматора и декадного счетчика переполнений, о тл и ч а ющ и йс я 5 тем, что, с целью расширения области применения, устройство содержит .коммутатор и блок поразрядного умножения, выход которого соединен с входом дешифратора, выход коммутатора соединен с входом блока пораз рядного умножения, выходы блока управлениясоединены с входами коммутатора и блока поразрядного умножения.

СмотретьЗаявка

2027375, 27.05.1974

ПРЕДПРИЯТИЕ ПЯ Г-4172

ЦЫПЛЕНКОВ СТАНИСЛАВ КОНСТАНТИНОВИЧ, ЗАБОЛОТСКИЙ ВАСИЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичные, двоичных, чисел

Опубликовано: 15.02.1976

Код ссылки

<a href="https://patents.su/3-503234-preobrazovatel-dvoichnykh-chisel-v-dvoichno-desyatichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичных чисел в двоично-десятичные</a>

Предыдущий патент: Устройство для отображения информации

Следующий патент: Коммутационный регистровый элемент

Случайный патент: Способ контроля качества обрезиненного невулканизованного корда