Устройство для умножения двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 748412

Авторы: Волковыский, Попов, Совкова

Текст

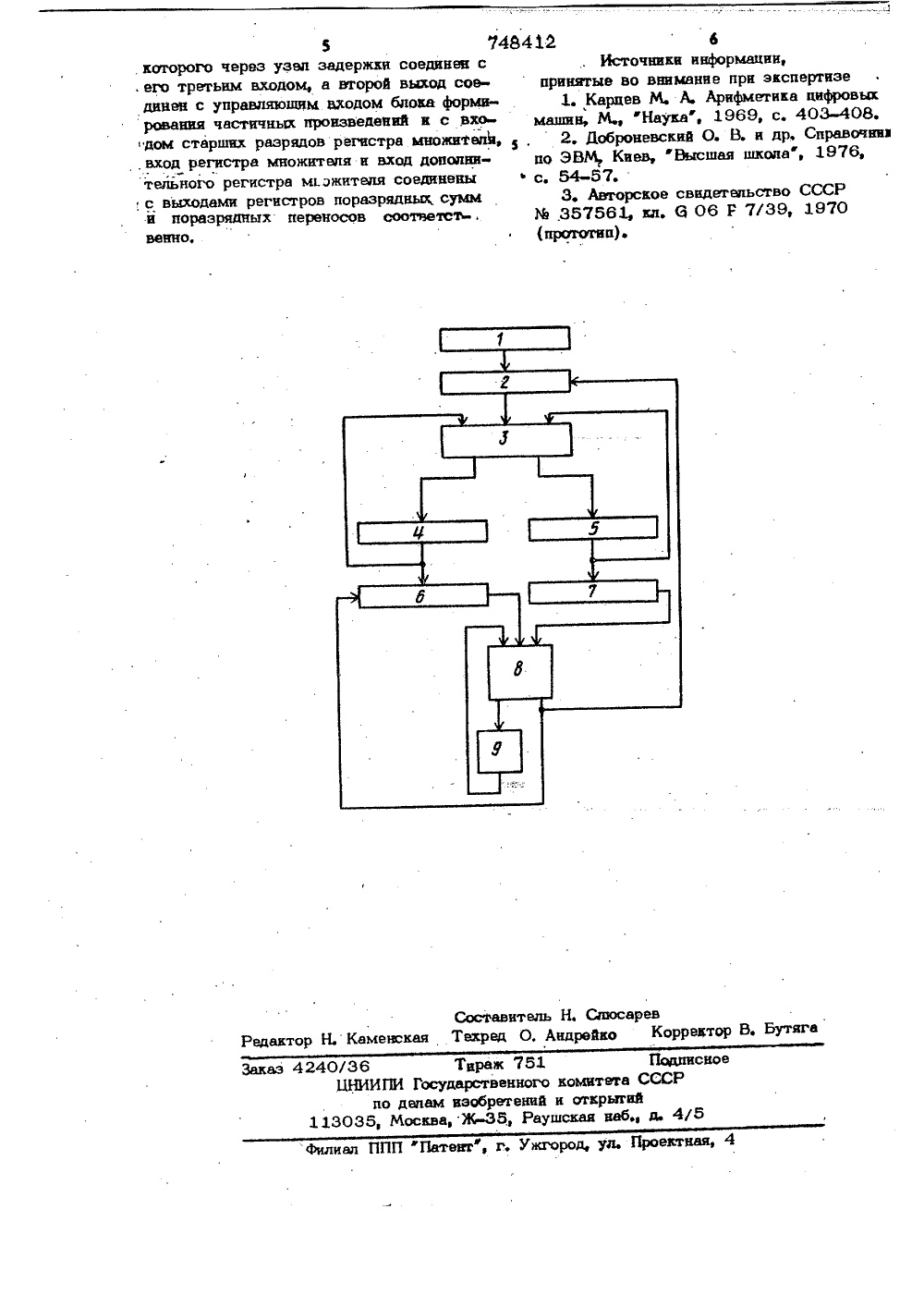

О П И С А И И Е748412ИЗОБРЕТЕНИЯ Союз Советски кСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 30.05.78 (21) 2622996/18-24 с присоединением заявки РЙ -Гасударственный ка 1 внтет СССР(23) Приоритет Опубликовано 15,07.80. Бюллетень Рй 26 иф делам извбретеннй н открытийДата опубликования описания 17,07,80(72) Автор изобретения В, Л. Волковыский, А. И. Попов и И, А, Совкова Рязанский радиотехнический институт(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХЧИСЕЛ 1Изобретение относится к области вы.числительной техники и может бьггь использовано в арифметических устройствах специализированных цифровых вычислительныхмашин,Известны устройства для умножениядвоичных чисел, содержащие регистрымножимого и множителя, схему формирования частичных произведений, блок поразрядного суммирования Ц, 211 ОНедостатком иэвестньгх. устройств является недостаточное быстродействие всвязи с затратами времени на приведениедвухрядного кода произведения.Наиболее близким аналогом является15устройство для умножения двоичных чисел,содержашее регистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формированиячастичных произведений, блок поразрядного суммирования частичных произведений.Выход младших разрядов регистра множителя соединен с управляюшим входом блока формирования частичных произведений,2выход регистра множимого через блок формирования частичных произведений сое. динен с одним.иэ входов блока поразрядного суммирования, два других входа которого соединены соответственно с выходами регистров поразрядных сумм и переносов, а выходы - со входами этих регистров Г 31За счет включения в состав схемы формирования частичных произведений дополнительных цепей сдвига 1 и преобразования множимого, в каждом такте работы данного устройства выполняется умножение на два разряда множителя.Недостатком данного устройства является недостаточное быстродействие в связи с затратами времени на приведение двухразрядного кода произведения,Белью изобретения является увеличение быстродействия устройства при выполнении многократных умножений.Для достижения этой цвпи в устройство введены дополнительный регистр множителя, сумматор и узел задержки, причем вы748412 ходы младших разрядов регистра множите. ля и дополнительного регистра множителясоединены соответственно с первым и вторым входами сумматора, первый выходкоторого через узел задеряски соединен с5его третьим входом, а второй выход соединен с управляющим входом блока формирования частичных произведений и со входом старших разрядов регистра множителя, второй вход регистра множителя ивход дополнительного регистра множителя.соединены с выходами регистров поразряд ных сумм и поразрядных переносов соответственно. Разрядность сумматора (одинили два) определяется числом одновременно анализируемых разрядов множителя.На чертеже представлена функциональная схема устройства.Устройство содержит регистр множимого 1, блок формирования частичных произведений 2, блок поразрядного суммирования 3, регистр поразрядных сумм 4, регистр поразрядных переносов 5, регистрымножителя 6 и 7, сумматор 8, узел задержки 9.25Умножение в устройстве производится,начиная с младших разрядов множителя. Висходном состоянии в регистре 1 записаномножимое, в регистрах 6 и 7 две компененты (двухрядный код) множителя, регистры 4 и 5 - в нулевом состоянии. Младшие разряды двухрядного кода множителяподаются с регистров 6 и 7 на входысумматора 8, где производится их суммирование,Сумма с выкода сумматора 8 поступает на управляющий вход блока формирования частичных произведений 2, а переносиз старшего разряда сумматора 8 поступает на узел задержки 9, где задерживается на один такт и добавляется к млЖшему разряду сумматора 8, Блок формирования частичных произведений 2 формирует частичные произведения, равные нулю,множимому 5, удвоенному множимомуили инверсному коду множимого (последние два значения возможны только приодновременном умножении на два разряда множителя) в зависимости от значениясуммы сумматора 8.50 Частичное произведение поступает йаблок поразрядного суммирования 3, где складывается со сдвинутым вправо на " число одновременно анализируемых раз-, 55 рядов множителя содержимым регистров поразрядных сумм и поразрядных переносов 4 и 5. Результат сложения в двухрядном коде записывается в регистры 4и 5.Одновременно производится сдвигвправо содержимого регистров 6 и 7 начисло одновременно анапиэируемьас разрядов множителя, а сумма с выхода сумматора 8 записывается в освободившиесястаршие разряды регистра 6,Описанная процедура повторяется доокончания анализа всех разрядов множителя. В результате в регистрах 4 и 5сформирован двухрядный код произведениячисла, записанного в регистре 1, на сумму чисел, первоначально записанных в регистрах 6 и 7, а в регистре 6 - сформирована сумма этих чисел.При выполнении многократных умножений двухрядный код произведения из регистров 4 и 5 передается в регистры 6и 7 соответственно и в следующем цикле умножения играет роль множителя.Введение в устройство дополнительногорегистра множимого, двоичного сумматораи урупа задержки позволяет существенносократить время выполнения многократныхумножений и операций вид А х (В + С)по сравнению с прототипом,В зависимости от кратности умножения, разрядности сомножителей и числаодновременно анапизируемых разрядовмножителя этот выигрыш составляет от10% до 30% при незначительных дополнит эпьных затратах оборудования. формула изобретения Устройство для умножения двоичных чисел, содержащее регистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формирования частичных произведений, блок поразрядного суммирования, причем выход регистра множимого через блок формирования частичных произведений соединен с одним из входов блока поразрядного суммирования, два других входа которого соединены соответственно с выходами регистров поразрядных сумм и поразрядных переносов, а выходы соответственно со входами этих регистров, о т л и ч а ю ш е е с я тей, что, с целью повышения быстродействия, в него введены дополнитепьный регистр множитвпя, сумматор и узел задержки, причем выходы младших разрядов регистра множителя и дополнительного регистра множителя соединены соответственно с первая-Нвторым входамн сумматора, пеРвый выход. которого через узел задержки соединен с . Источники информации,. его третьим входом, а второй выход сое- принятые во внимание при экспертизединен с управляюшим входом блока форми. Карцев М, А. Арифметика пифровыхрования частичных произведений и с вхо- машин, МфНаука, 1969, с. 403-408.дом старших разрядов регистра множитай, , 2. Доброневский О. В, и др, Справочниз, вход регистра множитепя и вход дополни- по ЭВМ, Киев, Высшая школа", 1976,тельного регистра мэжителя соединеныс. 54-57.с выходами регистров поразрядных, сумм 3, Авторское свидетельство СССРи поразрядных переносов соотеетсь-, % 357861 кл. 6 06 Р 7/39, 1970венно, (прототип)О/36 Тираж 781 БНИИПИ Государственного по делам изобретений 38, Москва, Ж, Рау иал ППП Патеог, г, Ужгород, ул, ПроектПодпис комитета СССР и открыгий шская наб., д. 4/8

СмотретьЗаявка

2622996, 30.05.1978

РЯЗАНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ВОЛКОВЫСКИЙ ВЛАДИМИР ЛЬВОВИЧ, ПОПОВ АЛЕКСАНДР ИВАНОВИЧ, СОВКОВА ИННА АЛЕКСАНДРОВНА

МПК / Метки

МПК: G06F 7/39

Метки: двоичных, умножения, чисел

Опубликовано: 15.07.1980

Код ссылки

<a href="https://patents.su/3-748412-ustrojjstvo-dlya-umnozheniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двоичных чисел</a>

Предыдущий патент: Устройство для умножения двоичных чисел

Следующий патент: Микропрограммное устройство управления

Случайный патент: Всасывающее сопло для систем пневмотранспорта