Устройство для умножения двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 748411

Авторы: Волковыский, Попов

Текст

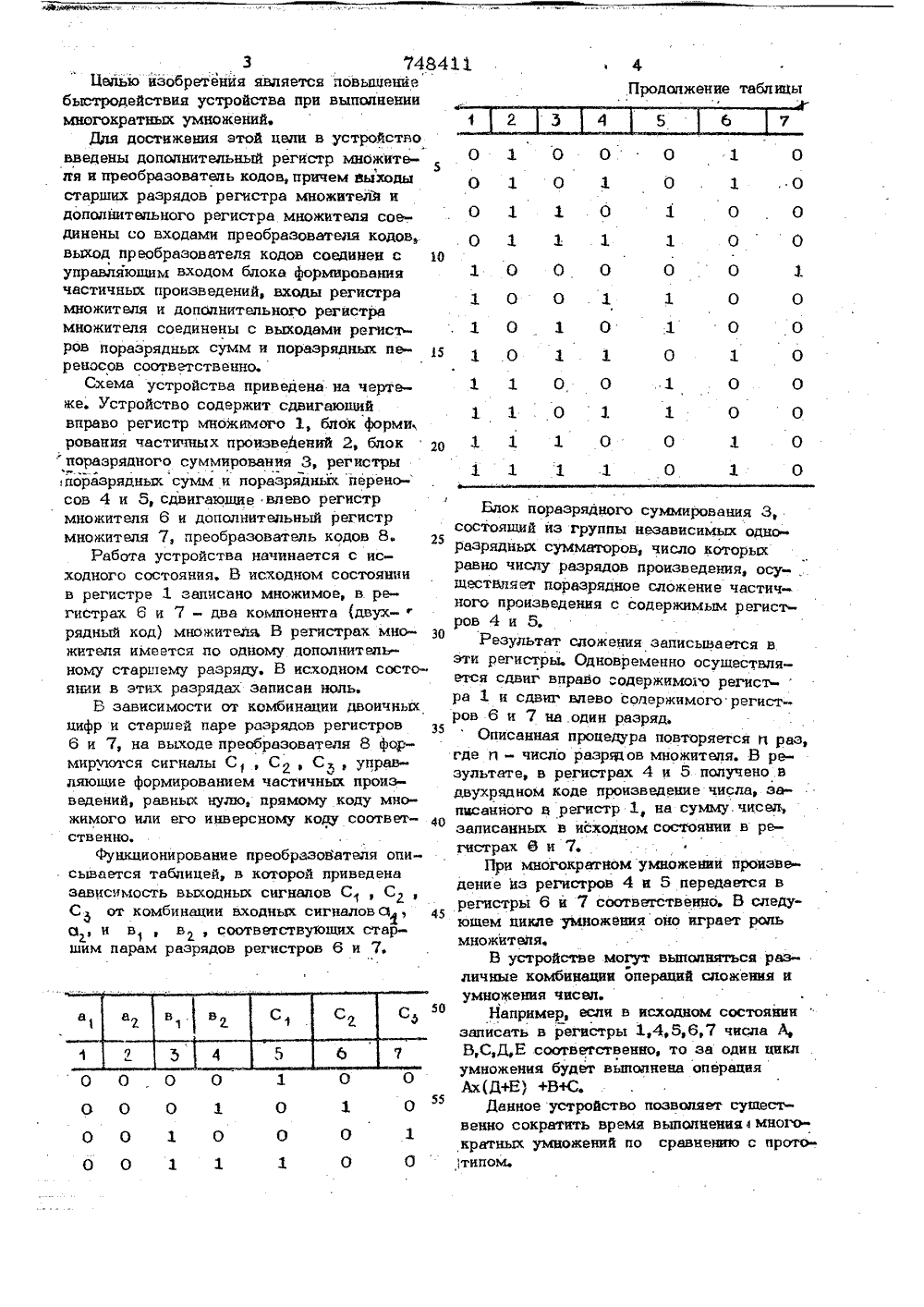

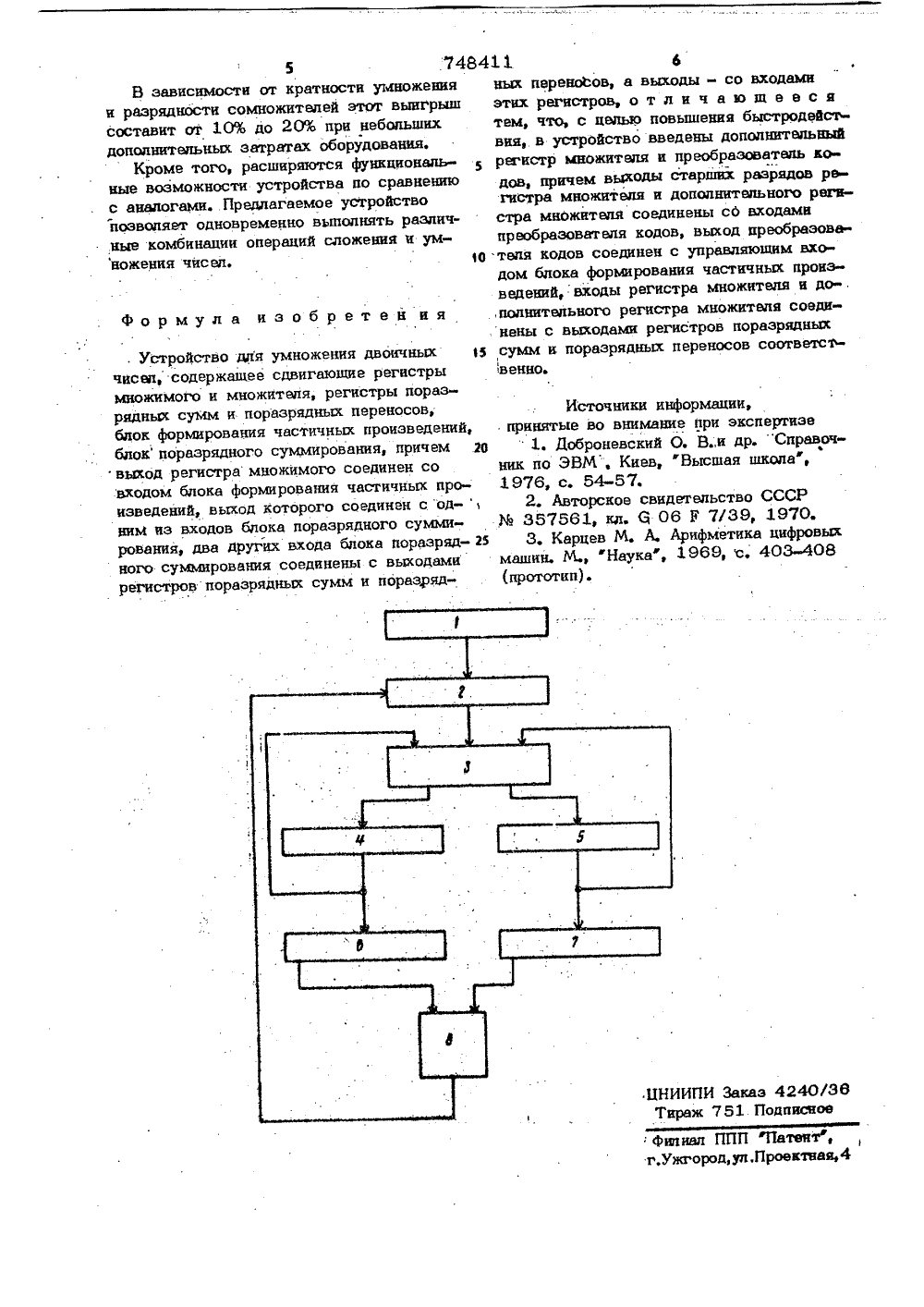

(23) Приоритет ллетень Мя 17,07. 2 публиковано 15.07.80. Бе 3) УДК 681.325 (088.8) делам изобретен и открытий. Поп овыски Рязанский радиотехнический институт Заявител ВОИЧНЫХ ЛЯ УМНОЖЕ 54) УСТ РО Изобретение относится к области вьтчйслительной техники и может быть использовано в арифметических устройствах спьциапизированных цифров ых вычислительныхмашин.Известны устройства содержащие регистры множимого и множителя, схему формирования частичных произведений, блок суммирования частичных произведений. Умножение в таких устройствах на чинается с младших разрядов множителя Щ, ЯНедостатком известных устройств является недостаточное быстродействие в связи с затратами времени на приведение двухрядного кода произведения.Наиболее близким к изобретению является устройство для умножения двоичных чисел 3), содержащее сдвигающие регистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формирования частичных произведений, блок поразрядного суммирования. Кроме этого в устройстве выход вля ется недосвязи с затрадвухрядного ен старшего разряда регистра множителя соединен с управляющим входом блока формирования частичных произведений, информационный вход которого соединен с вьаодом регистра множимого, а выход с однимиз входов блока поразрядного суммирования, два других входа которого соединены с выходами регистров поразрядных сумми поразрядных переносов , а выходы - совходами этих регистров.тоУмножение в данном устройстве осушествляется, начиная со старших разрядов. множителя.Это устройство имеет некоторое преимущество перед вышеупомянуть 15ми, так как метод умножениразрядов облегчает совмещениумножения с устройством делляет одновременно с умножесуммирование.Недостатком устройства ястаточное быстродействие втами времени на привед иекода произведения.Продолжение таблицы 5 6 7 О 1 О О О О 1 О 1 О О О О О 1 1 . О О 1 1 1 1 О О О 1 О О . 1 О О О О О О О 1 О 1 О 1 .О 1 1 О О О О 1 1 О О 1 1 О 1 1 1 1 О 1 1 1 1 О О О О О О О Блок поразрядного суммирования 3,состоящий иэ группы независимых одноразрядных сумматоров, число которыхравно числу разрядов произведения, осущестипяет поразрядное сложение частичного произведения с содержимым регистров 4 и 5.Результат сложения записывается вэти регистры. Одновременно осуществляется сдвиг вправо содержимого регист-ра 1 и сдвиг влево содержимого регистров 6 и 7 на один разряд.Описанная процедура повторяется о раз,где л - число разрядов множителя. В результате, в регистрах 4 и 5 получено вдвухрядном коде произведение числа, записанного в регистр 1, на сумму. чиселзаписанных в исходном состоянии в регистрах 6 и 7,При многократном умножении произведение нз регистров 4 и 5 передается врегистры 6 и 7 соответственно. В следующем цикле умножения оно играет рольмножителя.В устройстве могут выполняться рюличные комбинации операций сложения иумножения чисел.Например, если в исходном состояниизаписать в регистры 1,4,5,6,7 числа А,В,С,Д,Е соответственно, то эа один циклумножения будет выполнена операцияАх(Д+Е) +ВС.Данное устройство позволяет существенно сократить время выполнения,1 многократных умножений по сравнению с прототипом. 50 О О О О О О 1 1 1 3 74841Целью изобретения является повышение быстродействия устройства при выполнении многократных умножений.Для достижения этой цели в устройство введены дополнительный регистр множите 5 ля и преобразователь кодов, причем выходы старших разрядов регистра множителл 3 и дополнительного регистра множителя соединены со входами преобразователя кодов, выход преобразователя кодов соединен с 10 управляющим входом блока формирования частичных произведений, входы регистра множителя и дополнительного регистра множителя соединены с выходами регистров поразрядных сумм и поразрядных переносов соответственно.Схема устройства приведена на чертеже. Устройство содержит сдвигающий вправо регистр миожимого 1, блок форми, рования частичных произведений 2, блок 20 поразрядного суммирования 3, регистры .поразрядных сумм и поразрядных перено- сов 4 и 5, сдвигающие влево регистр множителя 6 и дополнительный регистр множителя 7, преобразователь кодов 8. 25Работа устройства начинается с исходного состояния. В исходном состоянии в регистре 1 записано множимое, в регистрах 6 и 7 - два компонента (двух-рядный код) множит иж В регистрах мно 30 жителя имеется ло одному дополнительному старшему разряду, В исходном состоянии в этих разрядах записан ноль.Б зависимости от комбинации двоичных цифр и старшей паре разрядов регистров 6 и 7, на выходе преобразователя 8 формируются си палы С, С ф С 1 уп,равляющие формированием частичнйх произведений, равных нулю, прямому коду множимого или его инверсному коду соответственно.функционирование преобразователя описывается таблицей, в которой приведена зависимость выходных сигналов С, С, С от комбинации входных сигналов с 3, а 5 а, и в, в, соответствукици.х старшим парам разрядов регистров 6 и 7.5 .748411 6В зависимости от кратности умножения ных паренсов, а выходы - со входами и разрядности сомножителей этот выигрыш этих регистров о т л и ч а ю щ е е с я составит от 10% до 20% при небольших тем, что, с целью повышения быстродейсвдополнительных затратах оборудования. вия, в устройство введены дополнительныйКроме того, расширяются функциональ-регистр множителя и преобразователь оные воэможности устройства по сравнению дов, причем выходы старших разрядов ре с аналогами. Предлагаемое устройство гистра множителя и дополнительного реги- позволяет одновременно выполнять раэлич- стра множителя соединены сд входами ные комбинации операций сложения и уь- преобразователя кодов, выход преобраэованожения чисел. 10 тепя кодов соединен с управляющим входом блока формирования частичных произведений, входы регистра множителя и до-, ф о р м у л а и з о б р е т е н и я,полнительного регистра множителя соединены с выходами регистров поразрядных сумм и поразрядных переносов соответсФ- венно.. Устройство дпя умножения двоичных и чисм, содержащее сдвигающие регистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формирования частичных произведений, блок поразрядного суммирования, причем 20 выход регистра множимого соединен со входом блока формирования частичных произведений, выход Которого соединен с од-ним из входов блока поразрядного суммирования, два другнх входа блока Поразряд ного суммирования соединены с выходами регистров поразрядных сумм и поразядИсточники информации,принятые во внимание при экспертизе1. Йоброневский О. В.,и др. Справочник по ЭВМ, Киев, "Высшая школа,1976, с. 54-57.2. Авторское свидетельство СССРЫ 357561, кл. 6 06 Р 7/39, 1970.3. Карцев М. А. Арифметика цифровыхмашин. М., "Наука, 1969, с, 403-408ИПИ Заказ 4240ираж 751 Подписное филиал ППП фПатентф, г,Ужгород, ул Проектная,4

СмотретьЗаявка

2618667, 22.05.1978

РЯЗАНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ВОЛКОВЫСКИЙ ВЛАДИМИР ЛЬВОВИЧ, ПОПОВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/39

Метки: двоичных, умножения, чисел

Опубликовано: 15.07.1980

Код ссылки

<a href="https://patents.su/3-748411-ustrojjstvo-dlya-umnozheniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двоичных чисел</a>

Предыдущий патент: Устройство для деления двоичных чисел

Следующий патент: Устройство для умножения двоичных чисел

Случайный патент: Противоугонное устройство