Устройство управления умножением двоично-десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

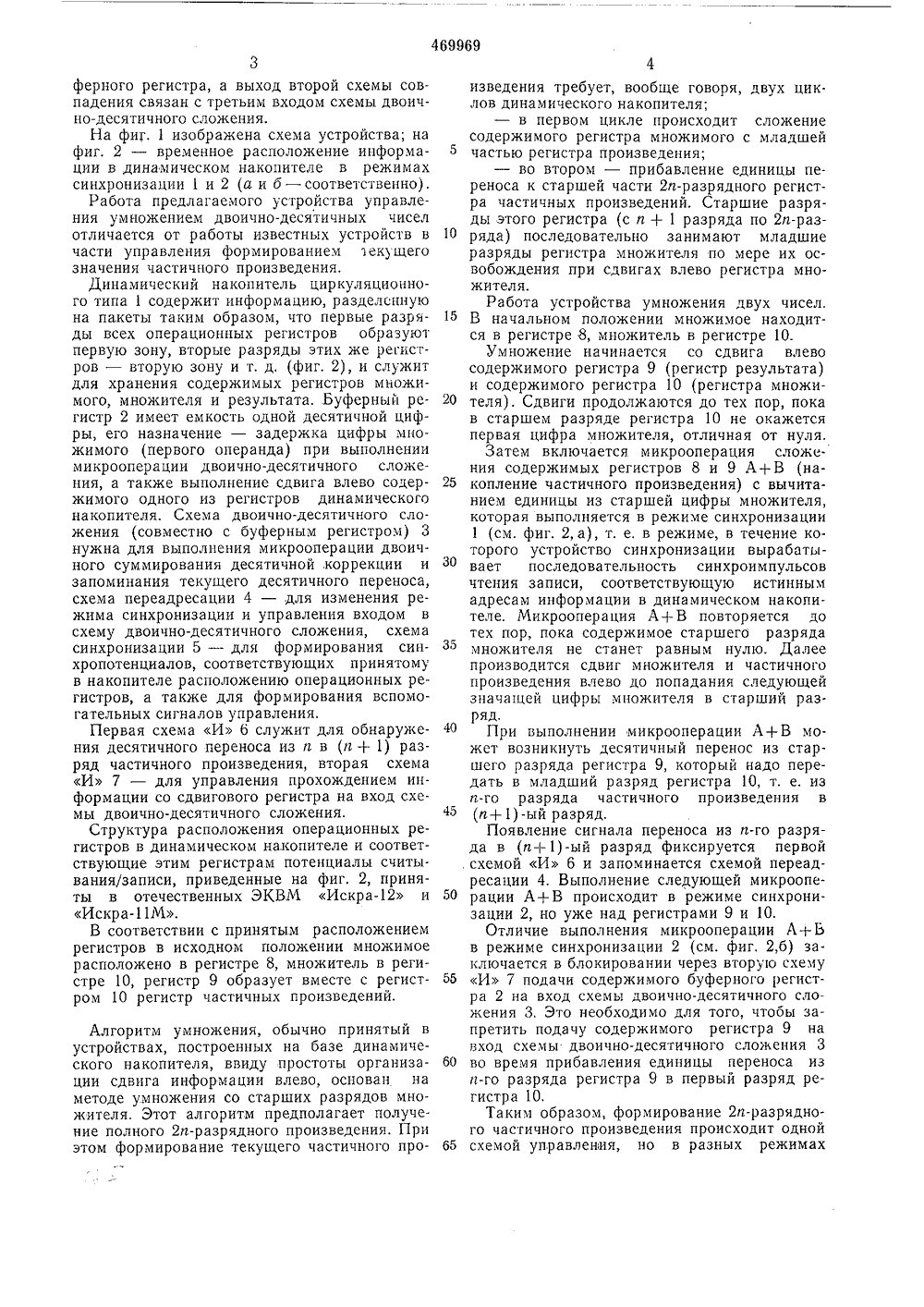

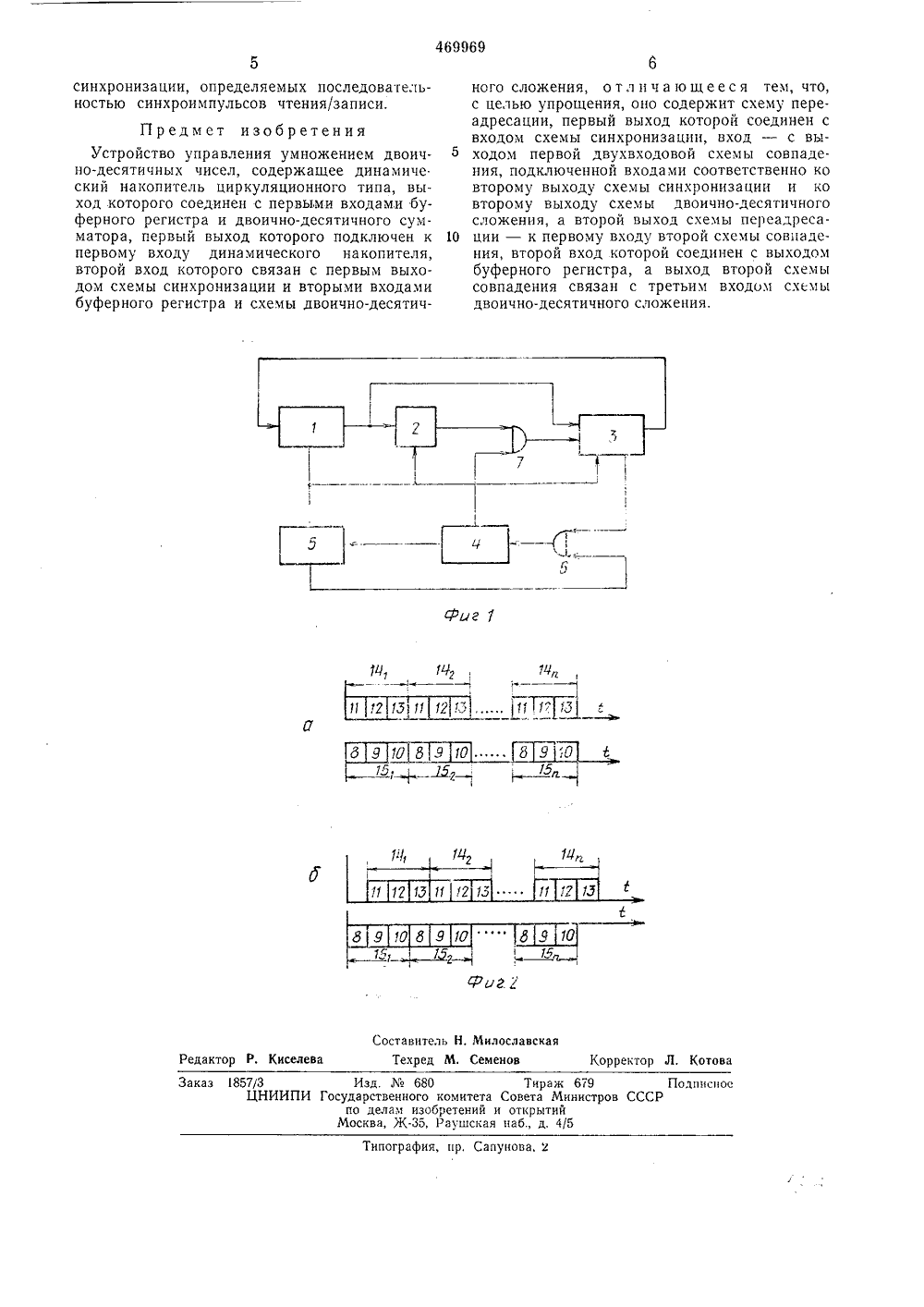

Союз Советских Социалистических Республик(32) ПриоритетОпубликовано 05,05.75. Бюллетень М 17Дата опубликования описания 31.07.75 Государственный комитет Совета Министров СССР 3) УДК 81.325.5(72) Авторы изобретен Б. И, Панферов, В, С, Громов, Б. Я. Фельдман,А, И, Малин, А, А. Минаев и Ю, А. Тетерин Институт электронных управляющих машин и Орловский завод управляющих вычислительных машин1 Заявите 4) УСТРОЙСТВО УПРАВЛЕНИЯ УМНОЖЕНИЕМ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛИзобретение относится к области вычпс;штельнои техники, в частности к вычислигельным машинам, использующим в качестве операционных (арифметических) регистров накопитель динамического типа (например, магиитострикционную линию задержки),Известны устройства подооного типа, например, применяемые в электронных клавчшных вычислительных машинах.Ы устройствах умножения известных машин, содержащих динамический накопительинформации, схему двоично-десятичного сло.жения, буферный регистр на одну десятичнуюцифру и схему синхронизации, используютсялиоо две схемы управления двоично-десятичным сложением для получения 2 и-разрядногопроизведения, либо одна схема управлениядвоично-десятичным сложением, но с устройством синхронизации с удвоенным модулемпересчета и дополнительными логическими 2 псхемами,11 рименение двух схем управления двоичнодесятичным сложением при получении 2 п-разрядного произведения связано с тем, что возникающий перенос из и-го десятичного разряда в (и + 1)-ый разряд т-го частичного произведения необходимо прибавить в том циклединамического накопителя, в котором происходит формирование первыхразрядов следующего (т + 1) -го частичного произведения. 30 Зто обстоятельство делает необходимым иметь в этих устройствах умножения две различные схемы управления входами в сумматор, две схемы для хранения текущих десятичных переносов.Организация так называемого сплошного 2 п-разрядного регистра частичных произведений, хотя и позволяет обоитись единой схемой управления двоично-десятичным сложением, но требует дополнительного оборудования в устройстве синхронизации этой машины, что относится к недостатку известных устройств.Целью изобретения является экономия оборудования устройства управления умножением за счет введения единой схемы управления двоично-десятичным сложением при получении 2 п-разрядных частичных произведений, но без усложнения устройства синхронизации.Сущность изобретения состоит в том, что устройство управления умножением двоичнодесятичных чисел содержит схему переадресации, первый выход которой соединен со входом схемы синхронизации, вход - с выходом первой двухвходовой схемы совпадения, подключенной входами соответствен;ю ко второму выходу схемы синхронизации и к второму выходу схемы двоично-десятичного сложения, а второй выход схемы переадресации - с первым входом второй схемы совпадения, второй вход которой соединен с выходом бу 469969ферного регистра, а выход второй схемы совпадения связан с третьим входом схемы двоично-десятичного сложения.На фиг. 1 изображена схема устройства; на фиг. 2 - временное расположение информации в динамическом накопителе в режимах синхронизации 1 и 2 (а и б - соответственно).Работа предлагаемого устройства управления умножением двоично-десятичных чисел отличается от работы известных устройств в части управления формированием влекущего значения частичного произведения.Динамический накопитель циркуляционного типа 1 содержит информацию, разделенную на пакеты таким образом, что первые разряды всех операционных регистров образуют первую зону, вторые разряды этих же регистров - вторую зону и т. д. (фиг. 2), и служит для хранения содержимых регистров множимого, множителя и результата. Буферный регистр 2 имеет емкость одной десятичной цифры, его назначение - задержка цифры множимого (первого операнда) при выполнении микрооперации двоично-десятичного сложения, а также выполнение сдвига влево содержимого одного из регистров динамического накопителя. Схема двоично-десятичного сложения (совместно с буферным регистром) 3 нужна для выполнения микрооперации двоичного суммирования десятичной, коррекции и запоминания текущего десятичного переноса, схема переадресации 4 - для изменения режима синхронизации и управления входом в схему двоично-десятичного сложения, схема синхронизации 5 - для формирования синхропотенциалов, соответствующих принятому в накопителе расположению операционных регистров, а также для формирования вспомогательных сигналов управления,Первая схема И 6 служит для обнаружения десятичного переноса из п в (и+ 1) разряд частичного произведения, вторая схема И 7 - для управления прохождением информации со сдвигового регистра на вход схемы двоично-десятичного сложения.Структура расположения операционных регистров в динамическом накопителе и соответствующие этим регистрам потенциалы считывания/записи, приведенные на фиг, 2, приняты в отечественных ЭКВМ Искраи ИскраМ.В соответствии с принятым расположением регистров в исходном положении множимое расположено в регистре 8, множитель в регистре 10, регистр 9 образует вместе с регистром 10 регистр частичных произведений. Алгоритм умножения, обычно принятый в устройствах, построенных на базе динамического накопителя, ввиду простоты организации сдвига информации влево, основан на методе умножения со старших разрядов множителя, Этот алгоритм предполагает получение полного 2 п-разрядного произведения. При этом формирование текущего частичного произведения требует, вообще говоря, двух циклов динамического накопителя;- в первом цикле происходит сложениесодержимого регистра множимого с младшейчастью регистра произведения;- во втором - прибавление единицы переноса к старшей части 2 п-разрядного регистра частичных произведений. Старшие разряды этого регистра (с п + 1 разряда по 2 п-раз 10 ряда) последовательно занимают младшиеразряды регистра множителя по мере их освобождения при сдвигах влево регистра множителя,Работа устройства умножения двух чисел.15 В начальном положении множимое находится в регистре 8, множитель в регистре 10.Умножение начинается со сдвига влевосодержимого регистра 9 (регистр результата)и содержимого регистра 10 (регистра множи 20 теля). Сдвиги продолжаются до тех пор, покав старшем разряде регистра 10 не окажетсяпервая цифра множителя, отличная от нуля,Затем включается микрооперация сложения содержимых регистров 8 и 9 А+В (на 25 копление частичного произведения) с вычитанием единицы из старшей цифры множителя,которая выполняется в режиме синхронизации1 (см. фиг. 2,а), т. е. в режиме, в течение которого устройство синхронизации вырабатывает последовательность сии хроим пульсовчтения записи, соответствующую истиннымадресам информации в динамическом накопителе. Микрооперация А+ В повторяется дотех пор, пока содержимое старшего разрядамножителя не станет равным нулю. Далеепроизводится сдвиг множителя и частичногопроизведения влево до попадания следующейзначащей цифры множителя в старший разрядд.4 О При выполнении микрооперации А+В может возникнуть десятичный перенос из старшего разряда регистра 9, который надо передать в младший разряд регистра 10, т. е. изи-го разряда частичного произведения в(п+ 1)-ый разряд,Появление сигнала переноса из п-го разряда в (п+ 1)-ый разряд фиксируется первой. схемой И 6 и запоминается схемой переадресации 4. Выполнение следующей микроопе 50 рации А+ В происходит в режиме синхронизации 2, но уже над регистрами 9 и 10.Отличие выполнения микрооперации Л+Ьв режиме синхронизации 2 (см. фиг. 2,б) заключается в блокировании через вторую схему55 И 7 подачи содержимого буферного регистра 2 на вход схемы двоично-десятичного сложения 3. Это необходимо для того, чтобы запретить подачу содержимого регистра 9 навход схемы двоично-десятичного сложения 360 во время прибавления единицы переноса изи-го разряда регистра 9 в первый разряд регистра 10.Таким образом, формирование 2 и-разрядного частичного произведения происходит одной65 схемой управления, но в разных режимах469969 Цг ) 14 д2:) 7)рУ) 1%,1 гвалт ЯД15 д 91 5 Составитель Н. Милославскаяедактор Р. Киселева Техред М. Семенов Корректор Л, Котова каз 857/3ЦНИИПИ Изд. М 680 сударственногопо делам изоб Москва, Ж,Тираж 679 Совета Министро открытий наб., д, 4/5ПодписноСР омитетаетенийаушская Типография, пр, Сапунова синхронизации, определяемых последовательностью синхроимпульсов чтения/записи. Предмет изобретенияУстройство управления умножением двоично-десятичных чисел, содержащее динамиче. ский накопитель циркуляционного типа, выход которого соединен с первыми входами буферного регистра и двоично-десятичного сумматора, первый выход которого подключен к первому входу динамического накопителя, второй вход которого связан с первым выходом схемы синхронизации и вторыми входами буферного регистра и схемы двоично-десятичного сложения, отличающееся тем, что, с целью упрощения, оно содержит схему переадресации, первый выход которой соединен с входом схемы синхронизации, вход - с выходом первой двухвходовой схемы совпадения, подключенной входами соответственно ко второму выходу схемы синхронизации и ко второму выходу схемы двоично-десятичного сложения, а второй выход схемы переадреса ции - к первому входу второй схемы совпадения, второй вход которой соединен с выходом буферного регистра, а выход второй схемы совпадения связан с третьим входом схемы двоично-десятичного сложения.

СмотретьЗаявка

1831947, 25.09.1972

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН, ОРЛОВСКИЙ ЗАВОД УПРАВЛЯЮЩИХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

ПАНФЕРОВ БОРИС ИВАНОВИЧ, ГРОМОВ ВЛАДИМИР СЕРГЕЕВИЧ, ФЕЛЬДМАН БОРИС ЯКОВЛЕВИЧ, МАЛИН АНАТОЛИЙ ИЛЬИЧ, МИНАЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ТЕТЕРИН ЮРИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/39

Метки: двоично-десятичных, умножением, чисел

Опубликовано: 05.05.1975

Код ссылки

<a href="https://patents.su/3-469969-ustrojjstvo-upravleniya-umnozheniem-dvoichno-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления умножением двоично-десятичных чисел</a>

Предыдущий патент: Пневматический счетчик импульсов

Следующий патент: Множительное устройство

Случайный патент: Тампонажная смесь