I всггсоэзнля i дискретно-аналоговый интегратордтгт л: тк; г v-:

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 370614

Автор: Вител

Текст

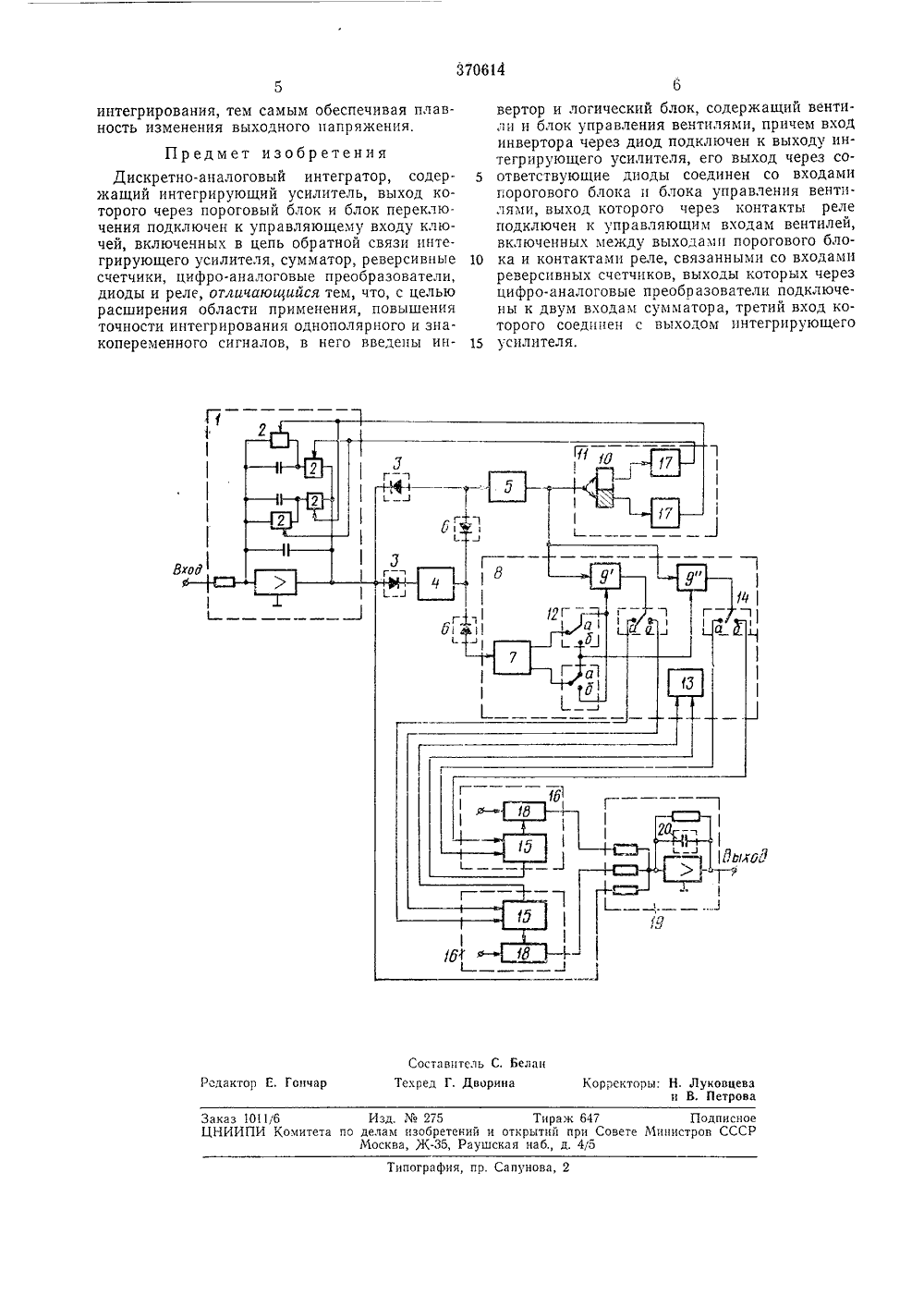

Союз Соватскиа Социалистическиа РеспуОливЗависимое от авт. свидетельства6 д /1 Заявлено 14.Х 11.1970 (Юв 1496752/18-24с присоединением заявкииорите Комитет по делам заоретекий и открытиЯ при Совете Микистасе СССРпубликовано 15 Л 1.1973. Бюллетень1 ата опубликования описания 24.1 Ч.1973 ДК 681,332(088,8) Автортзобретени3 аявитель Г. М. Хаиндрава лисский научно-исследовательский институт приборостроен и средств автоматизацииРг " " .Я 1 ф,л, цП 1" ,от 1т а:а 1; =. ;".". :":,ИСКРЕТН ИНТЕГ ЛОГО Изобретение относится к области приборостроения и может быть использовано как в электронных вычислительных машинах, так и в различных устройствах автоматики для осуществления операции долговременного интегрирования входной информации, представленной в виде непериодической, знакопеременной функции.Известен дискретно-аналоговый интегратор, построенный на базе интегрирующего уснли теля с переключающимися конденсаторами в цепи обратной связи. Однако, с его помощью возможно осуществление интегрирования только положительного входного сигнала; невозможно выполнение долговременного интегрп рова ния отрицательной и непериодической, знакопеременной функции, что сужает область его применения, кроме того, ему свойственна низкая точность интегрирования.С целью расширения области применения, 20 повышения точности интегрирования только положительного или только отрицательного и непериодического, знакопеременного сигнала, предлагается дискретно-аналоговый интегратор, собранный на элементах дискретной и 25 аналоговой вычислительной техники.Сущность предлагаемого изобретения состоит в том, что интегрирование непериодической знакопеременной функции производится алгебраическим суммированием сигналов од новременно двух видов - дискретного и аналогового. В результате существенно повышается точность интегрирования и уменьшаются габариты запоминающето блока.На чертеже представлена функциональная схема предлагаемого устройства,Она состоит из интегрирующего усилителя 1 с двумя накопительными конденсаторами С и демпферирующим конденсатором Свключенными в цепь обратной связи, а также электронными ключами 2, с помощью которых производится переключение и разряд конденсаторов С. С помощью конденсатора С, производится сглаживание всплеска напряжения на выходе интегрирующего усилителя во время переключения конденсаторов С.Выход интегрирующего усилителя 1 через развязывающие диоды 8 подключен ко входу инвертора 4 и порогового устройства б, а выход инвертора 4 через другие развязывающие диоды б подключен ко входу порогового устройства б и ко входу блока управления вентилями 7 логического устройства 8. К вентилям 9 и 9" логического устройства 8 подсоединен выход порогового устройства б, также подключенный к счетному входу статического триггера 10 блока переключения 11.С помощью перекидных контактов 12 электромагнитного реле релейного блока 18 выходы блока 7 связываются с управляющими вхо 3дами вентилей 9 и 9", выходные цепи которыхчерез другие перекидные контакты 14 тогоже релейного блока 13, связаны со входнымицепями реверсивных двоичных счетчиков 15и 1 Г (счетчики сохраняют информацию приаварийном выключении питающего напряжения), реверсивного запоминающего преобразователя дискретного сигнала в аналоговое напряжение 1 б. Выходные цепи статическоготриггера 10 через согласующие блоки 17 подключены к управляющим входам электронныхключей 2 интегрирующего усилителя 1, а выходные цепи цифро-аналоговых преобразователей 18 и 18" блоков 1 б подсоединены ковходу сумматора 19, который дополнительноснабжен запоминающим конденсатором 20.Ко входу сумматора 19 также подсоединенвыход интегрирующего усилителя 1,Работа дискретно-аналогового интеграторапроисходит следующим образом.Напряжение на входе интегрируется с помощью интегрирующего усилителя 1 до пороговой величины, определяемой пороговым устройством 5. Поскольку входной сигнал представляет непериодическую, знакопеременнуюфункцию времени, то на выходе интегрирующего усилителя может образоваться напряжение обеих полярностей, т. е, как плюс, так иминус. Пороговое устройство чувствительнотолько к. одному знаку входного напряжения(минусу) поэтому положительный сигнал спомощью инвертора 4 меняет знак и через развязывающие диоды б поступает на тот жевход порогового устройства 5 и на вход блока7 управления вентилями 9 и 9".Когда выходное напряжение интегрирующего усилителя 1 достигает пороговой величины,на выходе порогового устройства 5 появляетсяимпульс, который с одной стороны воздействует на счетный вход статического триггера 10и меняет его состояние на противоположное,в результате чего производится переключениеработающего конденсатора С на разряженный и цикл интегрирования повторяется с нулевым начальным условием,В исходном состоянии перекидные контакты 12 и 14 релейного блока 13 удерживаютсяв состоянии а, которому соответствует нулевое состояние обеих или одного реверсивныхдвоичных счетчиков 15,В случае отрицательной полярности выходного напряжения интегрирующего усилителя1, что соответствует положительной полярности входного напряжения, на выходе инвертора 4, напряжение отсутствует; соответственно оно отсутствует и на входе блока 7. Следовательно, на вход порогового устройства 5отрицательное выходное напряжение интегрирующего усилителя 1 поступает непосредственно через развязывающий диод 3.При отсутствии отрицательного напряженияна входе блока 7 (следовательно на его входдействует нулевое входное напряжение), наего выходе удерживаются два управляющихнапряжения, (полярностью указанной в скоб 370614 5 10 15 20 25 Зо 35 40 45 Интегральное значение некоторой, непериодической, знакопеременной функции напряжения, выражается алгебраической суммой с отдельных противополярных площадей, преобразованных в пропорциональное количество импульсов, складывание которых в дискретной форме осуществляется с помощью применения двух реверсивных, двоичных счетчиков 15 и 15", а аналоговая форма суммирования, осуществленная сумматором 19, позволяющим получить высокую точность результата долговременного интегрирования,Кроме того, включением в цепь обратной связи выходного суммирующего усилителя 19, конденсатора 20 осуществляется достаточная инерционность сумматора, что необходимо для устранения скачков и разрывности процесса 50 55 60 65 ках на фиг. 1), Под действием этих напряжений вентиль 9" находится в отпертом состоянии, а 9 - в запертом (поскольку полупроводниковые вентили в данной схеме отпираются отрицательным управляющим напряжением, а положительным - запираются).Следовательно, импульс образованный на выходе порогового устройства 5 пройдет через вентиль 9", контакт 14 по шине сложения ШС и запишется в реверсивном двоичном счетчике 15 реверсивного цифро-аналогового преобразователя 18 импульсы преобразуются в аналоговое напряжение отрицательной полярности.Если на выходе интегрирующего усилителя 1 полярность нарастающего напряжения положительная, то на выходе блока 4 превращается - в отрицательное и воздействует как на вход порогового устройства 5, так и на блок управления вентилями 7. При подаче отрицательного напряжения на вход блока 7 на его выходах управляющие напряжения меняют полярность на противоположную, Следовательно, отопрется вентиль 9 и запрется 9". В этом случае импульсы с выхода порогового устройства 5 пройдет через вентиль 9 другой контакт 14 по шине сложения ШС реверсивного двоичного счетчика 15" и запишутся в нем. С помощью цифро-аналогового преобразователя 18" импульсы преобразуются в форму аналогового напряжения положительной полярности и подаются на вход сумматора 19.Допустим в течение определенного периода на вход интегрирующего усилителя 1 действует напряжение положительной полярности, тогда импульсы, образованные на выходе порогового устройства 5 суммируются (накапливаются) в реверсивном двоичном счетчике 15.С выхода блока 18 импульсы, преобразованные в аналоговое напряжение отрицательной полярности, поступают на другой вход сумматора 19. На третий вход сумматора 19 с выхода интегрирующего усилителя 1 поступает переменная часть напряжения, которая складывается с напряжениями блоков 1 б.Заказ 1 О 1/6 Изд. М 275 Тираж 647ЦНИИПИ Комитета по делам изобретений и открьпий при СоветМосква, Ж, Раушская наб д. 45 Подписно Министров СССРТипография, пр. Сапунов интегрирования, тем самым обеспечивая плавность изменения выходного напряжения,Предмет изобретенияДискретно-аналоговый интегратор, содержащий интегрирующий усилитель, выход которого через пороговый блок и блок переключения подключен к управляющему входу ключей, включечных в цепь обратной связи интегрирующего усилителя, сумматор, реверсивные счетчики, цифро-аналоговые преобразователи, диоды и реле, отличающийся тем, что, с целью расширения области применения, повышения точности интегрирования однополярного и знакопеременного сигналов, в него введены инвертор и логический блок, содержащий вентили и блок управления вентилями, причем вход инвертора через диод подключен к выходу интегрирующего усилителя, его выход через со ответствующие диоды соединен со входамипорогового блока и блока управления вентилями, выход которого через контакты реле подключен к управляющим входам вентилей, включенных между выходами порогового бло ка и контактами реле, связанными со входамиреверсивных счетчиков, выходы которых через цифро-аналоговые преобр азователи подключены к двум входам сумматора, третий вход которого соединен с выходом интегрирующего 15 усилителя.

СмотретьЗаявка

1496752

Тбилисский научно исследовательский институт приборостроени, средств автоматизации

витель Г. М. Хаиндрава

МПК / Метки

МПК: G06G 7/186

Метки: всггсоэзнля, дискретно-аналоговый, интегратордтгт, тк

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-370614-i-vsggsoehznlya-i-diskretno-analogovyjj-integratordtgt-l-tk-g-v.html" target="_blank" rel="follow" title="База патентов СССР">I всггсоэзнля i дискретно-аналоговый интегратордтгт л: тк; г v-:</a>

Предыдущий патент: Пневматический интегратор

Следующий патент: Устройство для решения уравнения лапласа

Случайный патент: Беззондовый способ определения кислотности желудочного сока