Устройство для суммирования чисел, использующее систему остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 268751

Авторы: Луцкий, Овчинников

Текст

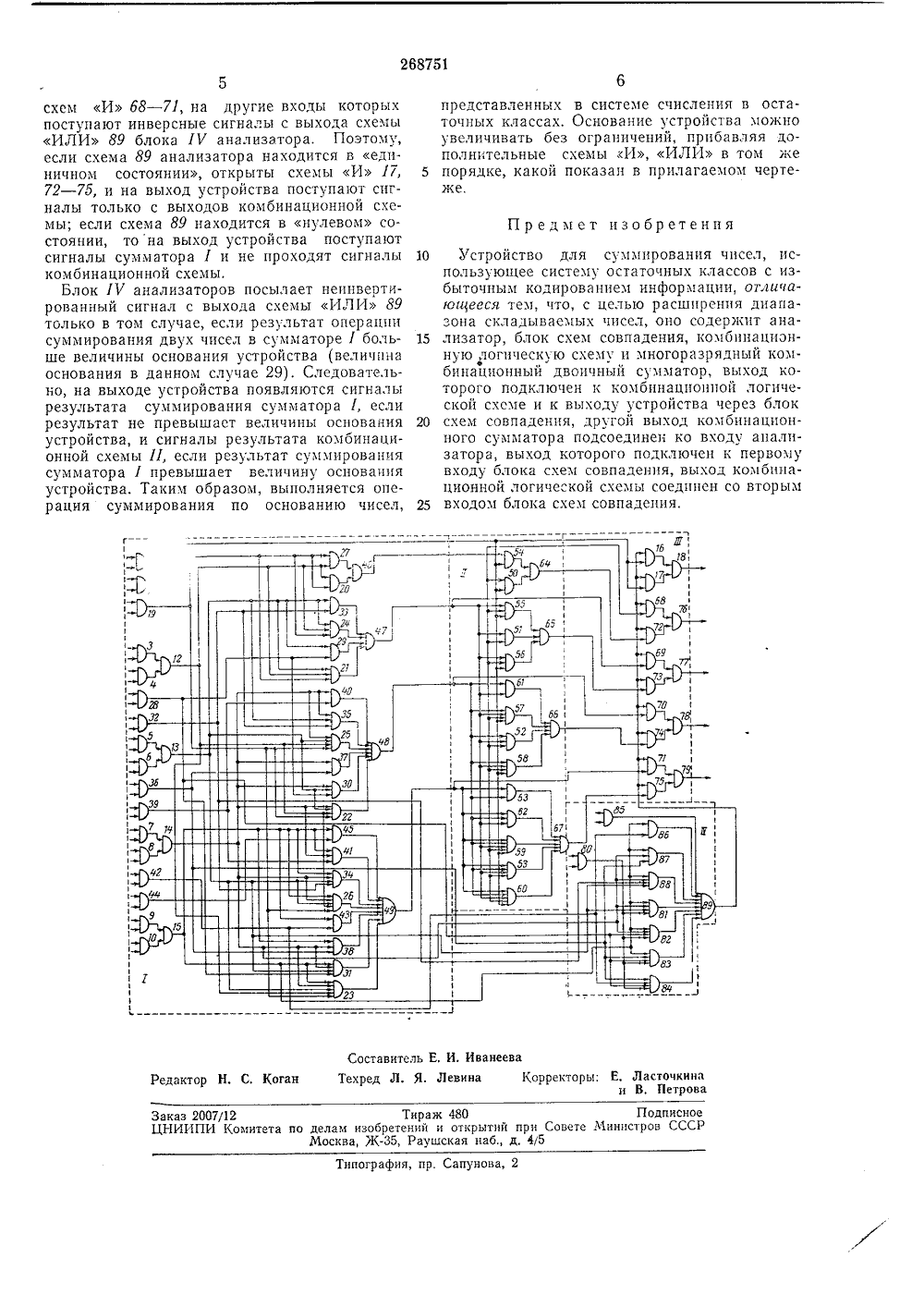

"- -. юзикте,т." еонмзв О ПИ САЙвМ.Е ИЗОБРЕТЕНИЯ 2687 И Союз Ссввтсиив Социалистичвскил РеспубливК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. свидетельства-влено 28.11.196 л. 42 птз, 7/41139662/18-24) заявк с присоединениеПриоритетОпубликовано 1 1 Ст 0 Комитет по деламизобретений и отирытиори Совете МинистровСССР УДК 681,325,55(088. Ч.1970. Бюллетеньия описания 27,ЧП.19 а опублико Авторыизобретени В. А. Луцкий и В. В, Овчинников итель ИСПОЛЬЗУЮЩЕСОВ УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ Ч СИСТЕМУ ОСТАТОЧНЫХИзобретение отно числительной техники твам, применяемым цифровых вычисл пользующих систему быточным кодированигическои схемы соединен со вторым входом блока схем совпадения.Функциональная схема предложенного устройства приведена на чертеже.5 Устройство состоит из многоразрядногокомбинационного двоичного сумматора 1 многоразрядной комбинационной двоичной схемы П, анализатора 111 и блока схем И еовпадения. Сумматор 1 осуществляет операцию сум мирования исходных многоразрядных чисел,представленных в системе остаточных классов.Выходы схем И 1 и 2,3 и 4,5 и 6, 7 и 8,9 и 10 подключены соответственно ко входам 15 схем ИЛИ 1 - 15. Прямой выход схемыИЛИ 11 подключен ко входу схемы И 1 а инверсный - ко входу схемы И 17, объ диненных схемой ИЛИ 18, являющейся выходом устройства. Прямой выход схемы И 20 19 подключен ко входам, схем И 20 - 23, аинверсный - ко входам схем И 24 - 27.Прямой выход схемы ИЛИ 12 подключен ко входам схем И 27, 24, 21, 25, 22, 23, а инверсный выход - ко входу схемы И 20.25 Прямой выход схемы 1 Л 28 подключен ковходу схем И 29 - 31, а аналогичный выход схемы И 82 подключен ко входам схем И 33 и 84.Прямой вь дкл 30 ко входам с 0,8 роиствам высти к устройования чисел машинах, исклассов с изится к уси в частидля суммиительныхостаточныхем,б, еючен 4, 2 б,Известны сумматоры с основанием более 31, выполненные на матрицах. Недостаток этих сумматоров заключается в том, что при .величинах оонования более 59 матрицы сумматоров содержат более чем 5,6 10 з элементов, и построить такие сумматоры невозможно.Цель изобретения заключается в построении устройства для суммирования чисел, расширяющего диапазон окладываемых чисел, представленных в системе остаточных классов по любому основанию, Диапазон складываемых чисел определяется величиной наибольшего основания. Эта цель достигается тем, что устройство для суммирования чисел содержит многоразрядный комбинационный двоичный сумматор, выход которого подключен к комбинационной логической схеме и к выходу устройства через блок схем совпадения. Другой выход комбинационного сумматора подсоединен ко входу анализатора, выход которого подключен к первому входу блока схем совпадения, выход комбинационной лоход схемы ИЛИ 13 по хем И 33, 24, 85, 25, 331, 23, а инверсный - ко входам схем И 29 и 21. Прямой выход схемы И 36 подключен ко входам схем И 37 и 38, а аналогичный выход схемы И 39 - ко входам схем И 40 и 41. Прямой выход схем ИЛИ 14 подключен ко входам схем И 40, 35, 25, 34, 26, 38, 21, 23, а инверсный - ко входам схем И 37, 22 и 30. Прямой выход схемы И 42 подключен ко входу схемы И 43; прямой выход схемы И 44 - ко входу схемы И 45; прямой выход схемы ИЛИ 15 - ко входам схем И 45, 34 и 26, а инверсный - ко входам схем И 43, 38, 31, 23.Схемы И 27 и 20; 21, 24, 29 и 33; 35, 25, 37, 30 и 40; 45, 41, 34, 26, 43, 38, 21 и 23 подключены ко входам схем ИЛИ 46 - 49, которые являются выходами первого двоичного сумматора 1. Выходы сумматора 1 подсоединены к комбинационной схеме П и к блоку схем совпадения 1 П в следующем порядочке: прямой выход схемы ИЛИ 46 сумматора 1 соединен,со входами схем И 50 - 53, а инверсный - со входами схем И 54 - 60, Прямой выход схемы ИЛИ 47 сумматора 1 соединен со входами, схем И 55, 57, 52, 58, 59, 53 и 60, а инверсный - со входами схем И 51, 56, 61 и 62. Прямой;выход схемы ИЛИ 48 сумматора 1 соединен со входами схем И 61, 57, 62, 59, 53 и 60, а инверсный - со входами схем И 52, 58 и 63, Прямой, выход схемы ИЛИ 49 сумматора 1 соединен со входами схемам И 62, 63, 59, а инверсный - со входами схем И 53 и 60 комбинационной схемы 11, Схемы И 54 и 50, 51, 55, 56, 52, 57, 58, 61 и 53, 59, 60, 62, 63 в комбинационной схеме 11 объединены схемами ИЛИ 64 - 67, которые являются выходами комбинационной схемы П, преобразующей сигналы сумматора 1.,Выходы сумматора 1 и комбинационной схемы П подсоединены к блоку схем совпадения в следующем порядке: выходы схем ИЛИ 46 - 49 сумматора 1 соединены со входами схем И 68 - 71 блока схем совпадения П 1, а выходы схем ИЛИ 64 6 сумматора 1 соединены со,входами схем И 72 - 75 блока схем совпадения 1 П. В блоке схем совпадения П 1 схемы 16 и 17, 63 и 72, 69 и 73, 70 и 74, 71 и 75 объединены схемами ИЛИ 18, 76 - 79, которые являются выходами устройства соответственно в первом, втором, третьем, четвертом и пятом разрядах. К свободным входам схем И 17, 72 - 75 подключен прямой выход, а ко входам схем И 16, 68 - 71 - инверсный выход блока анализато,ра, в котором выполнены следующие соединеия: схема И 80 подсоединена к схемам И 81 - 84, которые, вместе со схемами И 85 - 88 объединены схемой ИЛИ 89, являющейся выходом блока анализаторов. На вход "хемы И 80 подаются сигналы, инверсные зт переменных первых разрядов обоих слагаемых. Ко,входам схемы И 81 подсоединены выходы схем ИЛИ 13 - 15 и схемы И 80, Ко входам схемы И 83 подключены выхо 5 10 15 го 25 30 35 40 45 50 55 60 65 ды схем ИЛИ 15, 36, 28 и схемы И 80. Ко входам схемы И 84 подключены выходы схем И 42, 36, 18, 80. Ко входам схемы И 85 поданы сигналы переменных первых разрядов обоих слагаемых. Ко входам схемы И 86 подсоединены выходы схем ИЛИ 15 и И 42, Ко входам схемы И 87 подсоединены выходы схем ИЛИ 15 и 14 и И 34. Ко входам схемы И 83 )подключены выходы схем ИЛИ 13 - 15 и И 32. Схемы И 81 - 88 объединены схемой ИЛИ 89. Сигналы складываемых чисел подаются на входы схем И 1 - 10, 19, 28, 32, 36, 42, 44 в следующем порядке. На вход схемы И подаются сигналы инверсии от переменной первого разряда одного слагаемого и переменной первого разоряда другого слагаемого, на вход схемы И 2 - сигналы переменной первого разряда одного слагаемого и инверсии от переменного первого разряда другого слагаемого. На вход схемы И 19 подаются сигналы переменных первых разрядов. На вход схемы И З,подаются сигналы инверсии от переменной второго разряда одного слагаемого и переменной второго разряда другого слагаемого; на вход схемы И 4 - ,сигналы переменной второго разряда одного слагаемого и инверсии от переменной второго, разряда другого слагаемого. На входы пар схем 5 и 6, 7 и 8, 9 и 10 сигналы подаются аналогично для третьего, четвертого и пятого разрядов слагаемых, На входы схем И 28, 36 и 42 подаются соответственно сигналы переменных обоих слагаемых для второго, третьего и четвертого разрядов, а на входы схем И 32, 39 и 44 - сигналы инверсии от переменных обоих слагаемых для тех же разрядов.В результате, после прохождения сигналов через схемы ИЛИ 11 - 15 и схемы И 19, 28, 32, 36, 39, 42, 44 на выходах последних появляются сигналы промежуточного результата суммирования, которые направляются на входы схем И 27, 20, 33, 24, 29, 21, 40, 35, 25, 37, 30, 22, 45, 41, 34, 26, 43, 38, 31, 23 и после прохождения на выходах схем 46 - 49 появляются сигналы результата суммы во втором - пятом разрядах сумматора 1. Сигналы результата суммы в первом разряде появляются на выходе схемы ИЛИ 11 в прямом и инверсном коде и направляются прямосоответственно ко входам схем И 16 и 17 блока П 1.Сигналы результата суммирования сумматора 1 поступают на входы схем И 54, 50, 55, 51, 56, 61, 57, 52, 58, 63, 62, 59, 53, 60 комбинационной схемы П. При прохождении сигналов через комбинационную схему П, на выходах схем ИЛИ 64 - 67 появляются сигналы результата вычитания из суммы, образованной в сумматоре 1 постоянного числа, равного ос,нованию устройства. Эти сигналы поступают на входы схем И 72 - 75 блока 1 П схем совпадения, на другие входы которых поступают неинвертированные сигналы с выхода схемыанализатора. Сигналы результата суммирования сумматора 1 поступают на входы268751 Предмет изобретения Составитель Е. И, Иванеева Редактор Н. С. Коган Техред Л. Я. Левина Корректоры; Е. Ласточкина и В. Петровааказ 2007/12 Тираж 480ЦНИИПИ Комитета по делам изобретений и открытий приМосква, Ж, Раушская наб., д, 4/5 Подписное вете Министров СССРТипография, пр. Сапунова схем И 68 - 71, на другие входы которых поступают инверсные сигналы с выхода схемы ИЛИ 89 блока 1 Ъ анализатора, Поэтому, если схема 89 анализатора находится в единичном состоянии, открыты схемы И 17, 72 - 75, и на выход устройства поступают сигналы только с выходов комбинационной схемы; если схема 89 находится в нулевом состоянии, то на выход устройства поступают сигналы сумматора 1 и не проходят сигналы комбинационной схемы.Блок Ю анализаторов посылает неинвертированный сигнал с выхода схемы ИЛИ 89 только в том случае, если результат операции суммирования двух чисел в сумматоре 1 больше величины основания устройства (величина основания в данном случае 29). Следовательно, на выходе устройства появляются сигналы результата суммирования сумматора 1, если результат не превышает величины основания устройства, и сигналы результата комбинационной схемы 11, если результат суммирования сумматора 1 превышает величину основания устройства. Таким образом, выполняется операция суммирования по основанию чисел,представленных в системе счисления в остаточных классах. Основание устройства можно увеличивать без ограничений, прибавляя дополнительные схемы И, ИЛИ в том же 5 порядке, какой показан в прилагаемом чертеже. 10 Устройство для суммирования чцсел, использующее систему остаточных классов с избыточным кодированием информации, ог,тичаюи 1 ееся тем, что, с целью расширения диапазона складываемых чисел, оно содержит ана лизатор, блок схем совпадения, комбинационную логическую схему и многоразрядный комбинационный двоичный сумматор, выход которого подключен к комбинационной логической схеме и к выходу устройства через блок 20 схем совпадения, другой выход комбинационного сумматора подсоединен ко входу анализатора, выход которого подключен к первому входу блока схем совпадения, выход комбинационной логической схемы соединен со вторым 25 входом блока схем совпадения.

СмотретьЗаявка

1139662

В. А. Луцкий, В. В. Овчинников

МПК / Метки

МПК: G06F 7/72

Метки: использующее, классов, остаточных, систему, суммирования, чисел

Опубликовано: 01.01.1970

Код ссылки

<a href="https://patents.su/3-268751-ustrojjstvo-dlya-summirovaniya-chisel-ispolzuyushhee-sistemu-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования чисел, использующее систему остаточных классов</a>

Предыдущий патент: Магнитное логическое yctpofictbo

Следующий патент: Устройство для обраборки информации

Случайный патент: Опора рабочего валка прокатной клети