Микропрограммное устройство управления модуля вычислительной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1034037

Авторы: Благодарный, Тимонькин, Харченко

Текст

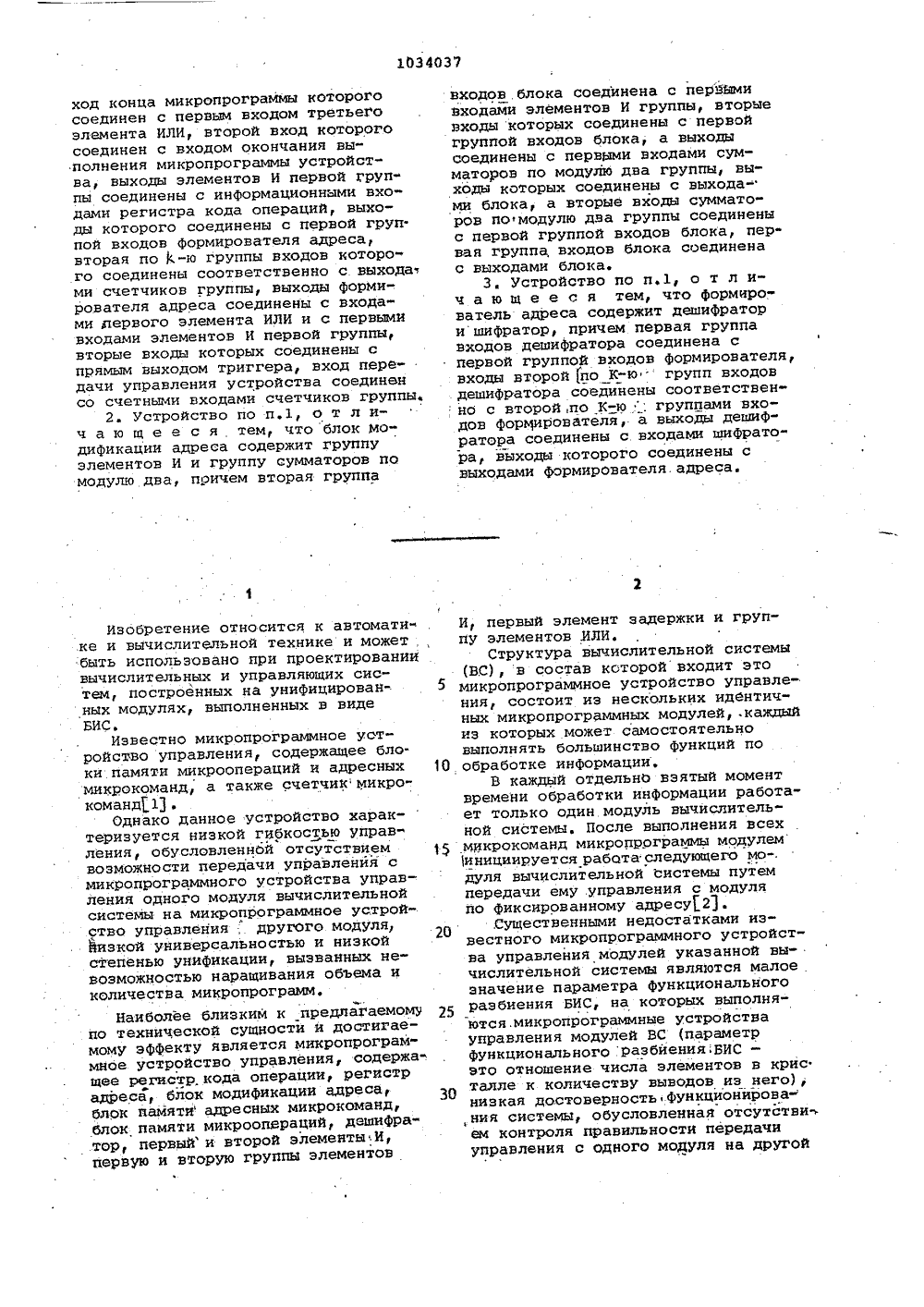

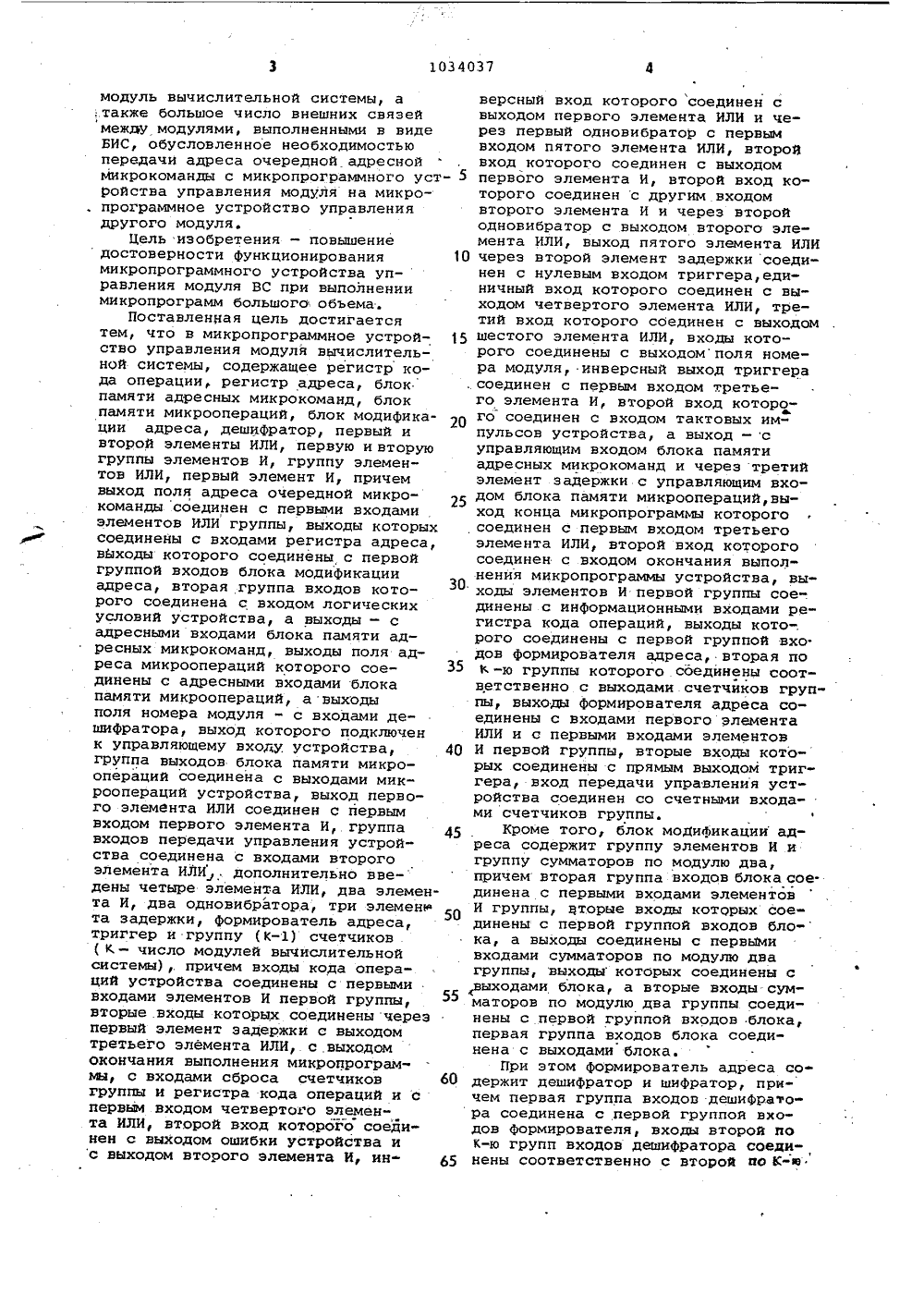

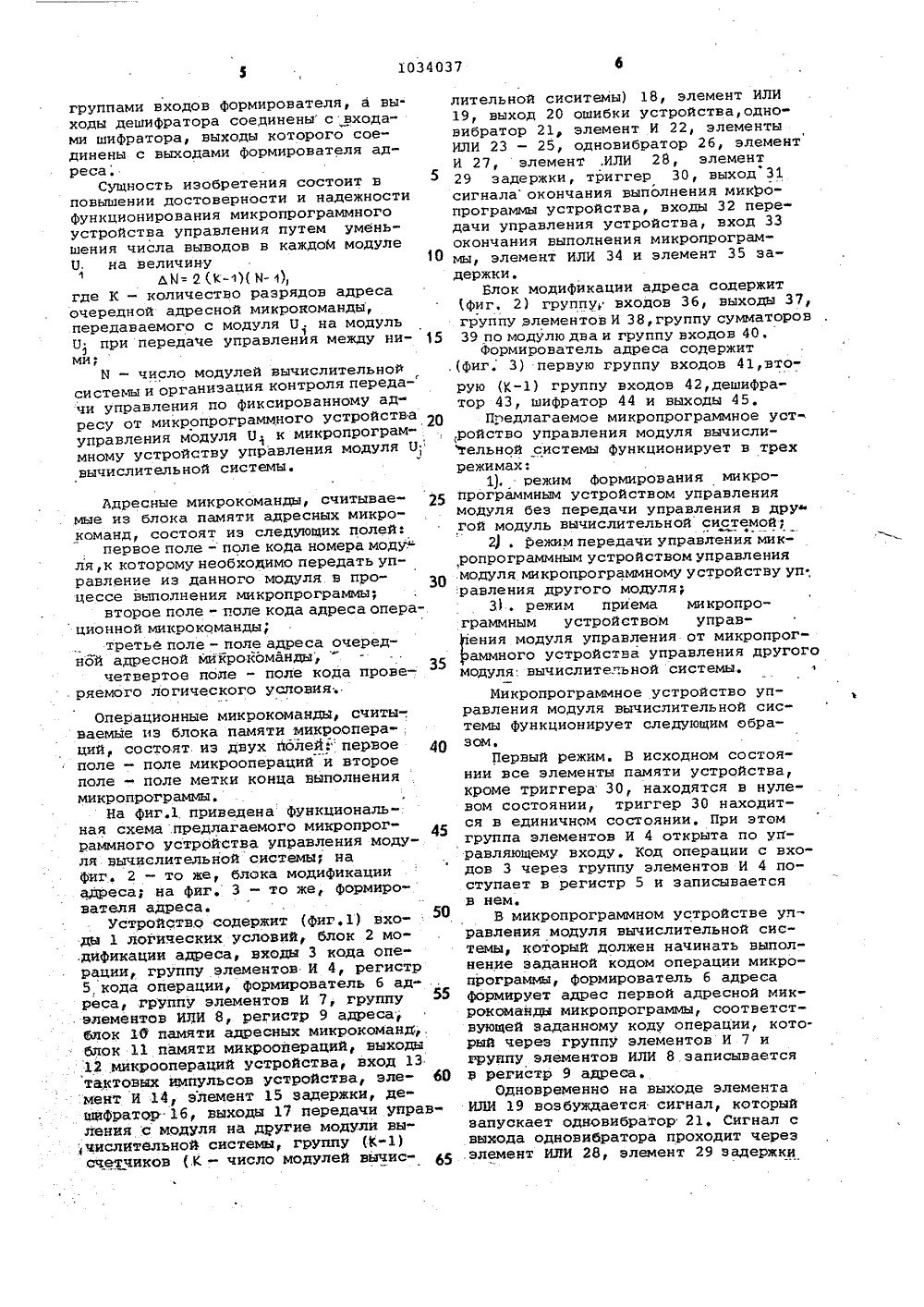

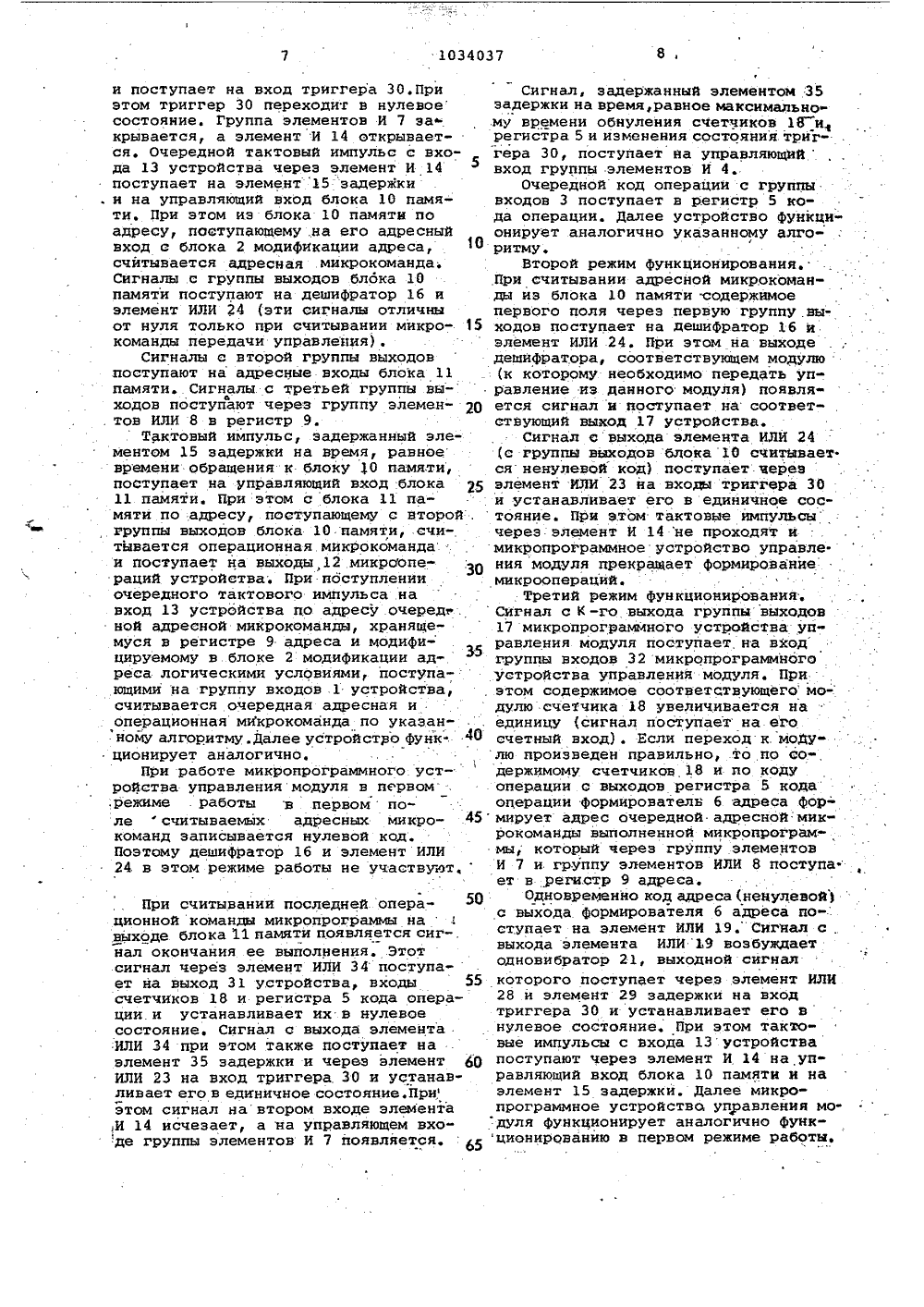

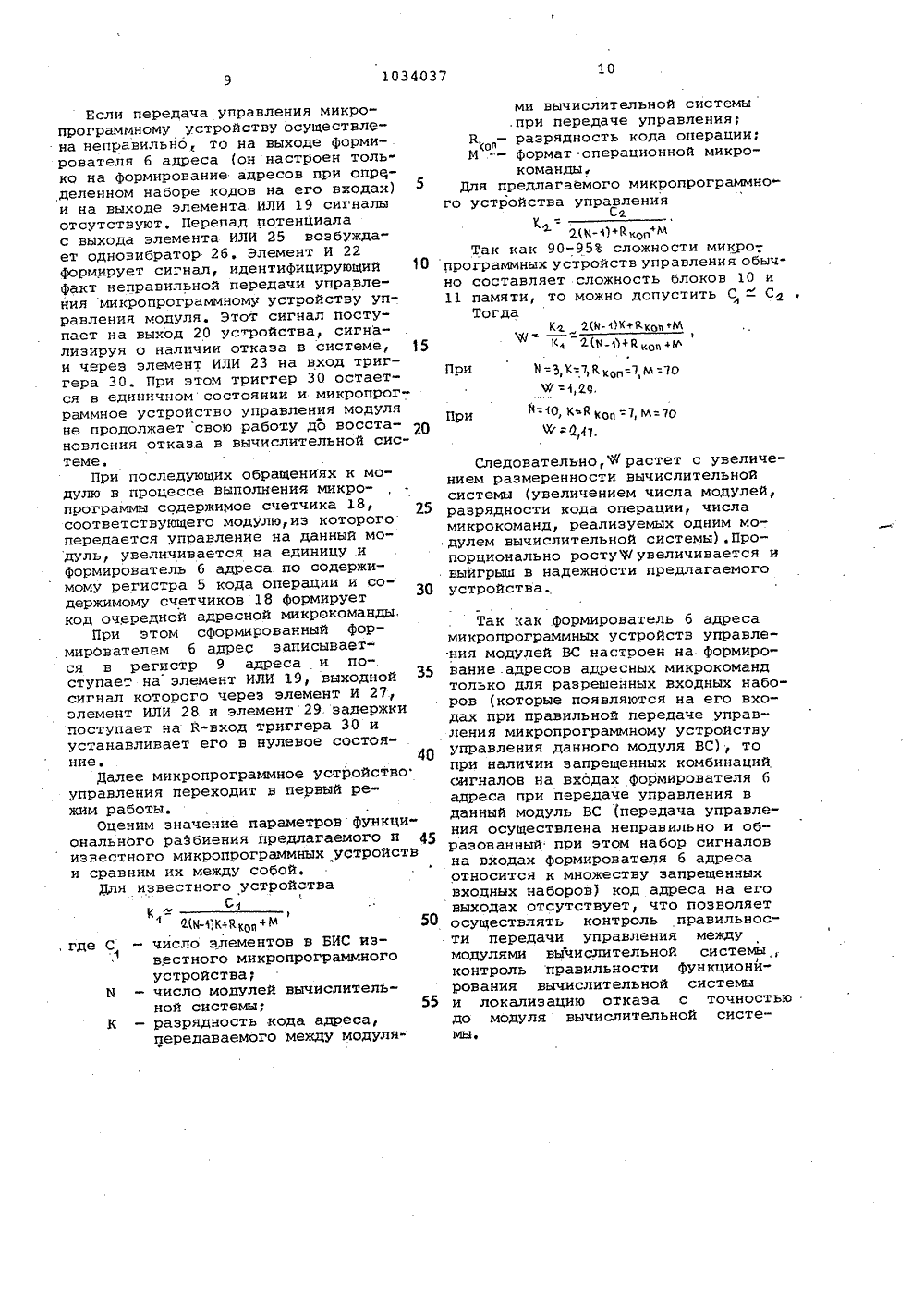

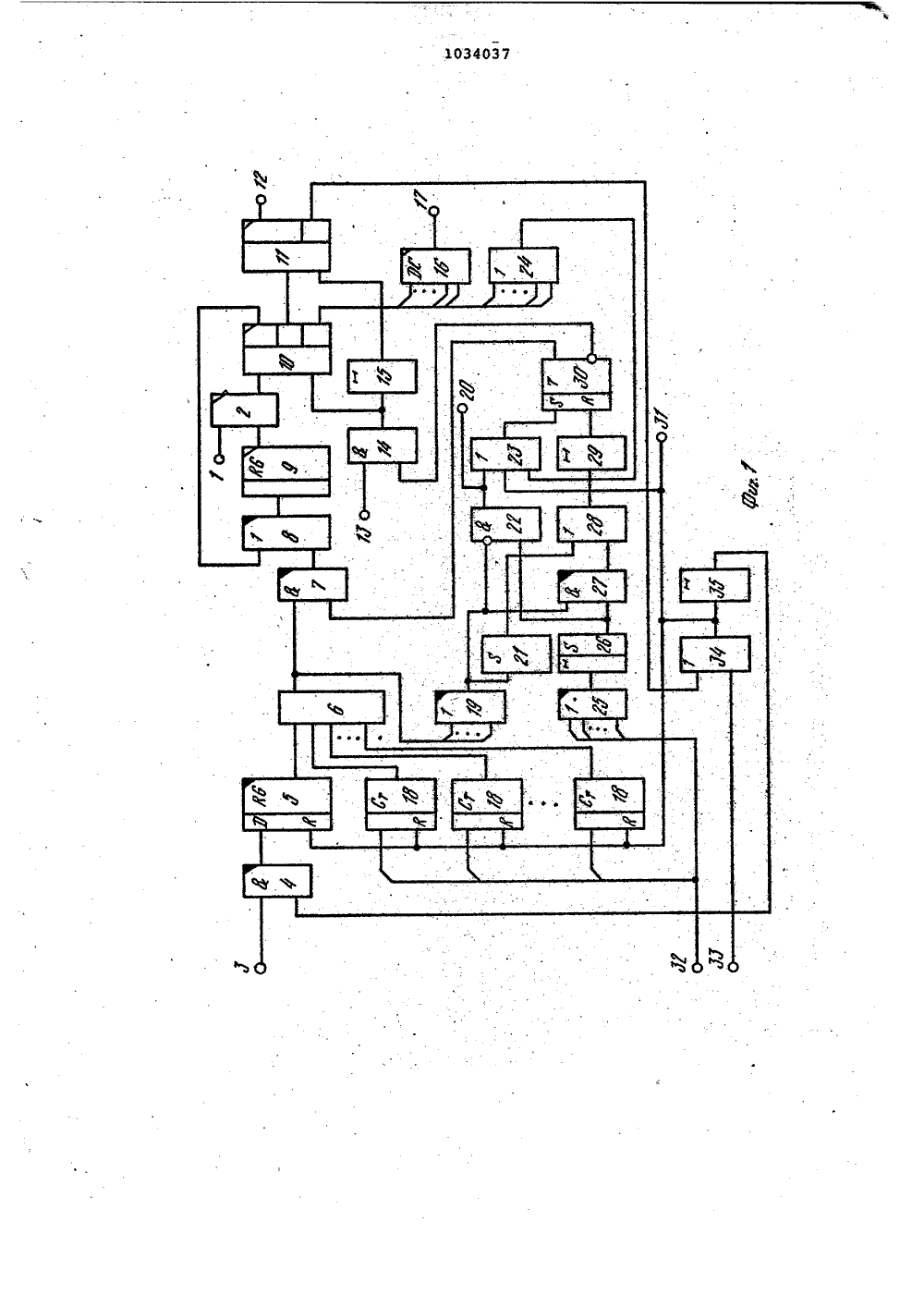

."ф 1-"-и.41м"Цг 7-.,ОПИСАНИЕ ИЗОБРЕТЕНИН АВТОРСИОМУ СВИДЕТЕЛЬСТВУ етельство ССС15/02, 1974.тельство СССР/22, 1978 ДАРСТВЕННЫЙ КОМИТЕТ СССРЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЪТИИ(54)(57) 1.МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ МОДУЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее регистр кода операции, регистр адреса, блок памяти адресных микрокоманд, блок памяти микроопераций, блок модификации адреса, дешифратор, первый элемент И, первую и вторую группу элементов И, первый и второй элементы ИЛИ, группу элементов ИЛИ, причем выход поля адреса очередной микрокоманды соединен с первыми входами элементов ИЛИ группы, выходы которых соединены с входами регистра адреса, выходы которого соединены с первой группой входов блокамодиФикации адреса, вторая группа входов которого соединена с входом логических условий устройства, а выходы - с адресными входами блока памятиадресных микрокоманд, выходы поля адреса микроопераций которого соединены с адресными входами блока ,памяти микроопераций, а выходы поля номера модуля - с входами дешифрато.ра, выход которого подключен к управляющему входу устройства, группа выходов блока памяти микроопераций соединена с выходами микроопераций устройства, выход первого элемента ИЛИ.соединен с первым входом первого элемента И, группа входов передачи управления устройства соединена с входами второго элемента ИЛИ, о т л и ч а ю щ е е с я тем,что, с целью повышения достоверности функционирования, оно дополнительно содержит четыре элемента ИЛИ,дваэлемента И, два одновибратора,триэлемента задержки, формировательадреса, триггер и группу (К) счетчиков (К - число модулей вычислительной системы), причем входы кода операций устройства соединены с первыми входами элементов И первой группы, вторые входы которых соединенычерез первый элемент задержки с выходом третьего элемента ИЛИ,с выходом окончания выполнения микро.программы,. с входами сброса счетчиков группы и регистра кода опера- .ций и с первым входом четвертого Еэлемента ИЛИ, второй вход которогосоединен с выходом ошибки устройства.и с выходом второго элемента И,инверсный вход которого соединен с вы- Сходом первого элемента ИЛИ и черезпервый одновибратор с первым вхо:дом пятого элемента ИЛИ, второй входкоторого соединен с выходом первогоэлемента И,второй вход которогосоединен с другим входом второгоэлемента И и через второй одновибратор с выходом второго элемен-та ИЛИ, выход пятого элемента ИЛИчерез второй элемент задержки соединен с нулевым входом триггера,.единичный вход которого соединен свыходом четвертого элемента ИЛИ,третий вход которого соединен свыходом шестого элемента ИЛИ,входыкоторого соединены с выходом поляноМера модуля, инверсный выход триг- каффгера соединен с первым входом третьего элемента И, второй вход которого соединен с входом тактовых импульсов устройства, а выход - суправляющим входом блока памяти адресных микрокоманд и через третийэлемент задержки с управляющим входом блока памяти микроопераций, Вы-,1034037 ход конца микропрограммы которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом окончания вы" полнения микропрограммы устройства, выходы элементов И первой Группы соединены с информационными входами регистра кода операций, выходы которого соединены с первой груп. пой входов формирователя адреса, вторая по К-ю группы входов которого соединены соответственно с выхода ми счетчиков группы, выходы формирователя адреса соединены с входами первого элемента ИЛИ и с первыми входами элементов И первой группы, вторые входы которых соединены с прямым выходом триггера, вход передачи управления устройства соединен со счетными входами счетчиков группы,2. Устройство по п,1, о т л ич а ю щ е е с я тем, что блок Модификации адреса содержит группу элементов И и группу сумматоров по модулю два, причем вторая группа Изобретение относится к автомати ке и вычислительной технике и может,быть использовано при проектированиИвычислительных и управляющих систем, построенных на унифицированных модулях, выполненных в виде БИС.Известно микропрограммное устройство управления, содержащее блоки памяти микроопераций и адресных микрокоманд, а также счетчик микро- командЦ .Однако данное устройство характеризуется низкой гибкостью управления, обусловленной отсутствием возможности передачи управленйя с микропрограммного устройства управления одного модуля вычислительнойсистемы на микропрограммное устройство управления; другого модуля, Мизкой универсальностью и низкой степенью унификации, вызванных невозможностью наращивания объема и количества микропрограмм.Наиболее близким к предлагаемому но технической сущностй и достигаемому эффекту является микропрограммное устройство управления, содержа; щее регистр. кода операции, регистр адреса, блок модификации адреса, блОК памяти адресных микрокоманд, блок памяти микроопераций, дешифратор, первый и второй элементы,И, первую и вторую группы элементов входов, блока соединена с первйми входами элементов И группы, вторые входы которых соединены с первой группой входов блока, а выходы соединены с первыми входами сумматоров по модулю два группы, выходы которых соединены с выхода- ми блока, а вторые входы сумматоров пофмодулю два группы соединены с первой группой входов блока, первая группа, входов блока соединена с выходами блока.3. Устройство по п.1, о т л ич а ю щ е е с я тем, что формирователь адреса содержит дешифратор и шифратор, причем первая группа входов дешифратора соединена с первой группой входов формирователя, входы второй по К"ю групп входов дешифратора соединены соответственно с второй,по К-ю : группами входов формирователя, а выходы дешифратора соединены с входами шифратора, выходы которого соединены с выходами формирователя. адреса. И, первый элемент задержки и группу элементов ИЛИ.Структура вычислительной системы(ВС), в состав которой входит этомикропрограммное устройство управления, состоит из нескольких идентичных микропрограммных модулей, каждыйиз которых может самостоятельновыполнять большинство функций по 10 обработке информации.В каждый отдельно взятый моментвремени обработки информации работает только один модуль вычислительной системы. После выполнения всехмикрокоманд микропрограммы модулем1 инициируется работа следующего мо-,дуля вычислительной системы путемпередачи ему управления с модуляпо фиксированному адресу 2.20.Существенными недостатками известного микропрограммного устройства управления модулей указанной вычислительной системы являются малоезначение параметра функциональногоразбиения БИС, на которых выполняются, микропрограммные устройствауправления модулей ВС (параметрФункционального Разбйения,БИС -это отношение числа элементов в кристалле к количеству выводов из него),низкая достоверность,функционирова,ния системы, обусловленная отсутстви. ем контроля правильности передачи управления с одного модуля на другоймодуль вычислительной системы, а ,также большое число внешних связей между модулями, выполненными в виде БИС, обусловленное необходимостью передачи адреса очередной адресной Микрокоманды с микропрограммного уст ройства управления модуля на микро. программное устройство управления другого модуля.Цель изобретения - повышение достоверности функционированиямикропрограммного устройства управления модуля ВС при выполнении микропрограмм большого объема.Поставленная цель достигаетсятем, что в микропрограммное устройство управления модуля вычислительной системы, содержащее регистр кода операции, регистр адреса, блокпамяти адресных микрокоманд, блокпамяти микроопераций, блок модификации адреса, дешифратор, первый ивторой элементы ИЛИ, первую и вторуюгруппы элементов И, группу элементов ИЛИ, первый элемент И, причемвыход поля адреса очередной микрокоманды соединен с первыми входамиэлементов ИЛИ группы, выходы которыхсоединены с входами регистра адреса,выходы которого соединены с первойгруппой входов блока модификацииадреса, вторая группа входов которого соединена с входом логическихусловий устройства, а выходы - садресными входами блока памяти адресных микрокоманд, выходы поля адреса микроопераций которого соединены с адресными входами блокапамяти микроопераций, а выходыполя номера модуля - с входами дешифратора, выход которого подключенк управляющему входу устройства,группа выходов блока памяти микроопераций соединена с выходами микроопераций устройства, выход первого элемЕнта ИЛИ соединен с первымвходом первого элемента И,.группавходов передачи управления устройства соединена с входами второгоэлемента ИЛИ . дополнительно введены четыре элемента ИЛИ, два элемента И, два одновибратора, три элемента задержки, формирователь адреса,триггер и группу (К) счетчиков( К- число модулей вычислительнойсистемы),. причем входы кода операций устройства соединены с первымивходами элементов И первой группы,вторые .входы которых соединены черезпервый элемент задержки с выходомтретьего элемента ИЛИ, с выходомокончания выполнения микропрограммы, с входами сброса счетчиков группы и регистра кода операций и спервым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом ошибки устройства и с выходом второго элемента И, инверсный вход которого соединен свыходом первого элемента ИЛИ и через первый одновибратор с первымвходом пятого элемента ИЛИ, второйвход которого соединен с выходом - 5 первого элемента И, второй вход которого соединен с другим .входомвторого элемента И и через второйодновибратор с выходом второго элемента ИЛИ, выход пятого элемента ИЛИ О через второй элемент задержки соединен с нулевым входом триггера,единичный вход которого соединен с выходом четвертого элемента ИЛИ, третий вход которого соединен с выходом 5 шестого элемента ИЛИ, входы которого соединены с выходомполя номера модуля, инверсный выход триггера.соединен с первым входом третье"го элемента И, второй вход которо кго соединен с входом тактовых импульсов устройства, а выход - суправляющим входом блока памятиадресных микрокоманд и через третийэлемент задержки с управляющим вхо дом блока памяти микроопераций,выход конца микропрограммы которогосоединен с первым входом третьегоэлемента ИЛИ, второй вход которогосоединен с входом окончания выполненйя микропрограммы устройства, выходы элементов И первой группы сое-.динены с информационными входами регистра кода операций, выходы кото-.рого соединены с первой группой вхо.дов формирователя адреса, вторая по З 5 к -ю группы которого соединены соответственно с выходами счетчиков группы, выходы формирователя адреса соединены с входами первого элементаИЛИ и с первыми входами элементов 40 И первой группы, вторые входы которых соединены с прямым выходом триггера, вход передачи управления устройства соединен со счетными входами счетчиков группы.Кроме того, блок модификации адреса содержит группу элементов И игруппу сумматоров по модулю два,причем вторая группа входов блока соединена с первыми входами элементовИ группы, вторые входы которых соединены с первой группой входов бло-ка, а выходы соединены с первымивходами сумматоров по модулю двагруппы, выходы которых соединены с,выходами блока, а вторые входы сумматоров по модулю два группы соединены с первой группой входов блока,первая группа входов блока соединена с выходами блока.При этом формирователь адреса со бО держит дешифратор и шифратор, причем первая группа входов дешифратора соединена с первой группой входов формирователя, входы второй пок-ю групп входов дешифратора соеди иены соответственно с второй по К-югруппами входов формирователя, а выходы дешифратора соединены с входами шифратора, выходы которого соединены с выходами формирователя адреса .Сущность изобретения состоит в 5повышении достоверности и надежностифункционирования микропрограммногоустройства управления путем уменьшения числа выводов в каждоМ модулеО. на величину 10дй= 2 (.К-Ы Н- ),где К - количество разрядов адресаочередной адресной микрокоманды,передаваемого с модуля О, на модульО при передаче управленйя между ними;Н - число модулей вычислительнойсистемы и организация контроля переда-"чи управления по фиксированному адресу от микропрограммного устройства 20управления модуля О,) к микрапрограммному устройству управления модуля Овычислительной системы. Адресные микрокоманды, считывае мые из блока памяти адресных микро- команд, состоят из следующих полей:первое поле - поле кода номера моду.- ля,к которому необходимо передать управление из данного модуля в процессе выполнения микропрограммы;второе поле - поле кода адреса опера ционной микрокоманды;третье поле - поле адреса очередной адресной мнкрокоманды, "четвертое поле - поле кода проверяемого логического условия.Операционные микрокаманды, считы-, ваемые из блока памяти микроопера-, ций, состоят. из двух полей:первое 40 поле - поле микроопераций и второе пале - поле метки конца выполнения микропрограммы.На фиг.1 приведена функциональная схема предлагаемого микропраг раммного устройства управления модуля вычислительной системы," нафиг. 2 - то же, блока модификации адреса; на фиг. 3 - та же, формирователя адреса.Устройство содержит (фиг.1) входы 1 логических условий, блок 2 мо,дификации адреса, входы 3 када операции, группу элементов И 4, регистр 5, кода операции формирователь 6 ад . реса, группу элементов И 7, группу элементов ИЛИ 8, регистр 9 адреса, блок 16 памяти адресных микрокоманде,. блок 11 памяти микроапераций, выходы 12 микроапераций устройства, вход 13 тактовых импульсов устройства, эле- б 0 мент И 14, элемент 15 задержки, дешифратар, выходы 17 передачи управлений с модуля на другие модули вы:,числйтельной системы, группу (К) счетчиков ( к - число модулей вычис лительной сиситемы) 18, элемент ИЛИ 19, выход 20 ошибки устройства, одно- вибратор 21, элемент И 22, элементы ИЛИ 23 - 25, одновибратор 26, элемент И 27, элемент ,ИЛИ 28, элемент 29 задержки, триггер 30, выход 31 сигналаокончания выполнения микро" программы устройства, входы 32 передачи управления устройства, вход 33 окончания выполнения микропрограммы, элемент ИЛИ 34 и элемент 35 задержки.Блок модификации адреса содержитфиг, 2) группу, входов 36, выходы 37,группу элементов И 38,группу сумматоров39 по модулю два и группу входов 40.Формирователь адреса содержит (фиг. 3) первую группу входов 41,вторую (К) группу входов 42,дешифратор 43, шифратор 44 и выходы 45.Предлагаемое микропрограммное уст ,.ройство управления модуля вычислительной системы функционирует в трех режимах1). Режим Формирования микропрограммным устройством управлениямодуля без передачи управления в дру гой модуль вычислительной системой;4режим передачи управлениямик:ропрограммным устройством управлениямодуля микропрограммному устройству уп;равления другого модуля;3), режим приема микропрограммным устройством управения модуля управления от микропрогаммного устройства управления другого модуля; вычислительной системы.Микропрограммное устройство управления модуля вычислительной системы функционирует следующим образом.Первый режим. В исходном состоянии все элементы памяти устройства,кроме триггера 30, находятся в нулевом состоянии, триггер 30 находится в единичном состоянии, При этомгруппа элементов И 4 открыта по уп- равляющему входу, Код операции с входов 3 через группу элементов И 4 поступает в регистр 5 и записываетсяв нем.В микропрограммном устройстве управления модуля вычислительной системы, который должен начинать выполнение заданной кодом операции микропрограммы, формирователь 6 адресаформирует адрес первой адресной микракаманды микропрограммы, соответствующей заданному коду операции, который через группу элементов И 7 изрунпу элементов ИЛИ 8 записываетсяв регистр 9 адреса.Одновременна на выходе элементаИЛИ 19 возбуждается сигнал, которыйзапускает адновибратор 21, Сигнал свыхода одновибратора проходит черезэлемент ИЛИ 28, элемент 29 задержки1034037 8, и поступает на вход триггера ЗО.Приэтом триггер 30 переходит в нулевоесостояние. Группа элементов И 7 закрывается, а элемент И 14 открывается. Очередной тактовый импульс с входа 13 устройства через элемент И 14поступает на элемент 15 задержки. и на управляющий вход блока 10 памяти. При этом из блока 10 памяти поадресу, поступающему .на его адресныйвход а блока 2 модификации адреса,считывается адресная .микрокоманда.Сигналы .с группы выходов блока 10памяти поступают на дешифратор 16 иэлемент ИЛИ 24 (эти сигналы отличныот нуля только при считывании микрокоманды передачи управления).Сигналы с второй группы выходовпоступают на адресные входы блока 11памяти. Сигналы с третьей группы выЬходов поступают через группу элемен О. тов ИЛИ 8 в регистр 9,Тактовый импульс, задержанный элементом 15 задержки на время, равноевремени обращения к блоку 0 памяти,поступает на управляющий вход блока11 памяти. При этом с блока 11 памяти по адресу, поступающему с второй .группы выходов блока 10 памяти, считывается операционная микрокомандаи поступает на выходы 12 микроопераций устройства. При ноступленииочередного тактового импульса навход 13 устройства по адресу очеред .ной адресной микрокоманды, хранящемуся в регистре 9 адреса и модифицируемому в блоке 2 модификации адреса логическими условиями, поступа-:ющими на группу входов 1 устройства,считывается очередная адресная иоперационная микрокоманда по указанному алгоритму. Далее устройство функ 40ционирует аналогично.При работе микропрограммного устройства управления модуля в первом,режиме . работы в нервом поле считываемых адресных микрокоманд записывается нулевой код.Поэтому дешифратор 16 и элемент ИЛИ24. в этом режиме работы не участвуют,При считывании последней операционной команды микропрограммы навыходе блока 11 памяти появляется сиг-. нал окончания ее выполнения. Этот сигнал через элемент ИЛИ 34 поступает на выход 31 устройства, входы 55 счетчиков 18 и регистра 5 кода операции.и устанавливает их и нулевое состояние. Сигнал с выхода элемента ИЛИ 34 при этом также поступает на элемент 35 задержки и червз элемент 6 О ИЛИ 23 на вход триггера 30 и устанавливает его в единичное состояние,При этом сигнал навтором входе элемента ,И 14 исчезает, а на управляющем входе группы элементов И 7 появляется. Сигнал, задержанный элементом:35 задержки иа время, равное максимальному времени обнуления счетчиков 18 и регистра 5 и изменения состояния триггера 30, поступает на управляющий вход группы элементов И 4.Очередной код операции с группы входов 3 поступает в регистр 5 кода операции. Далее устройство функционирует аналогично указанному алгоритму.Второй режим функционирования. При считывании адресной микрокомаиды из блока 10 памяти содержимое первого поля через первую группу выходов поступает на дешифратор 16 и элемент ИЛИ 24. При этом на выходе дешифратора, соответствующем модулю (к которому необходимо передать уп-. равление из данного модуля) появляется сигнал и поступает на соответ- . ствующий выход 17 устройства.Сигнал а выхода элемента ИЛИ 24 (с группы выходов блока 10 считывает. ся ненулевой код) поступает. через элемент ИЛИ 23 на входы триггера 30 и устанавливает его в единичное состояние. При этом тактовые импульсы через:элемент И 14 не проходят и микропрограммное устройство управле. ния модуля прекращает Формирование микрооперацийТретий режим Функционирования, Сигнал с К -го выхода группы выходов 17 микропрограькного устройства управления модуля поступает на вход группы входов 32 микропрограммного Устройства управления модуля. При этом содержимое соответствующегомодулю счетчика 18 увеличивается на единицу (сигнал поступает на его счетный вход). Если переход к моДулю произведен правильно, то по со.-, держимому счетчиков 18 и по коду операции а выходов регистра 5 кода операции Формирователь б адреса фор- мирует адрес очередной адресной микрокоманды выполненной микронрограм+ мы, который через группу элементов И 7 и группу элементов ИЛИ 8 поступа ет в регистр 9 адреса.Одновременно код адреса(ненулевой) с выхода формирователя б адреса по-. ступает на элемент ИЛИ 19. Сигнал с, выхода элемента ИЛИ 19 возбуждает одновибратор 21, выходной сигнал которого поступает через .элемент ИЛИ 28 и элемент 29 задержки на вход триггера 30 и устанавливает его внулевое состояние, При этом тактовые импульсы с входа 13 устройства поступают через элемент И 14 на управляющий вход блока 10 памяти и на элемент 15 задержкй. Далее микропрограммное устройство управления модуля Функционирует аналогично функционированию в первом режиме работы.Если передача управления микропрограммному устройству осуществлена неправильно, то на выходе формирователя б адреса (он настроен толь"ко на формирование адресов при определенном наборе кодов на его входах)и на выходе элемента. ИЛИ 19 сигналыотсутствуют, Перепад потенциалас выхода элемента ИЛИ 25 возбуждает одновибратор 26. Элемент И 22формирует сигнал, идентифицирующий 10факт неправильной передачи управления микропрограммному устройству управления модуля. Этот сигнал поступает на выход 20 устройства, сигнализируя о наличии отказа в системе, 15и через элемент ИЛИ 23 на вход триггера 30 При этом триггер 30 остается в единичномсостоянии и микропрограммное устройство управления модуляне продолжает свою работу до восстановления отказа в вычислительной системе.При последующих обращениях к мо"дулю в процессе выполнения микропрограммы содержимое счетчика 18,соответствующего модулю,из которогопередается управление на данный модуль, увеличивается на единицу иформирователь б адреса по содержимому регистра 5 кода операции и содержимому счетчиков 18 формируеткод очередной адресной микрокоманды,При этом сформированный формирователем б адрес записывается в регистр 9 адреса и по-.ступает на элемент ИЛИ 19, выходнойсигнал которого через элемент И 27,элемент ИЛИ 28 и элемент 29. задержкипоступает на й-вход триггера 30 иустанавливает его в нулевое состояние. 40Далее микропрограммное устройствоуправления переходит в первый режим работы,Оценим значение параметров функционального разбиения предлагаемого и 45известного микропрограммных устройстви сравним их между собой.Для известного устройстваСлйн-е.я, + м 50, где С - число элементов в БИС известного микропрограммногоустройства;Б - число модулей вычислительной системы; 55К - разрядность кода адреса,передаваемого между модуля ми вычислительной системы.при передаче управления;к - разрядность кода операции;КопМформат операционной микрокоманды,Для предлагаемого микропрограммного устройства управленияСкк,=г(й- Ч+ копТак как 90-95 сложности микро-. программных устройств управления обычно составляет сложность блоков 10 и 11 памяти, то можно допустить С - СллТогдак 2 э)к+кк+мКл Ь-Юфй(од ФМ Н:3,К:,К,:,м=оФI = (,20.В-.0, Кй КО=7, М=70Фг =Я,47. При При Следовательно,Ю растет с увеличением размеренности вычислительной системы (увеличением числа модулей, разрядности кода операции, числа микрокоманд, реализуемых одним модулем вычислительной системы),Пропорционально росту% увеличивается и выйгрыш в надежности предлагаемого устРойстваТак как формирователь б адреса микропрограммных устройств управления модулей ВС настроен на формирование .адресов адресных микрокоманд только для разрешенных входных наборов (которые появляются на его входах при правильной передаче управления микропрограммному устройству управления данного модуля ВС), то при наличии запрещенных комбинаций сигналов на входах формирователя 6 адреса при передаче управления в данный модуль ВС (передача управления осуществлена неправильно и образованный при этом набор сигналов на входах формирователя б адреса относится к множеству запрещенных входных наборов) код адреса на его выходах отсутствует, что позволяет осуществлять контроль правильности передачи управления между модулями вычислительной системы,. контроль правильности функционирования вычислительной системы и локализацию отказа с точностью до модуля вычислительной систе- мые1034037 Составитель Л.ЛогачеваРачкулинец ТехредМ.Гергель Коррект Редант Огар Подпис4/5 филиал ППП фПатент, г. ужгород, ул. Проектная,4 Заказ 5627/52 Ти ВНИИПИ Государственно по делам изобретен 113035, Москва, Ж

СмотретьЗаявка

3401818, 21.01.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: вычислительной, микропрограммное, модуля, системы

Опубликовано: 07.08.1983

Код ссылки

<a href="https://patents.su/8-1034037-mikroprogrammnoe-ustrojjstvo-upravleniya-modulya-vychislitelnojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления модуля вычислительной системы</a>

Предыдущий патент: Устройство для возведения чисел в квадрат по модулю

Следующий патент: Приоритетное устройство с шифракцией адреса

Случайный патент: Устройство для обжига порошко-образных материалов