Сумматор последовательного действия

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 268008

Автор: Бобров

Текст

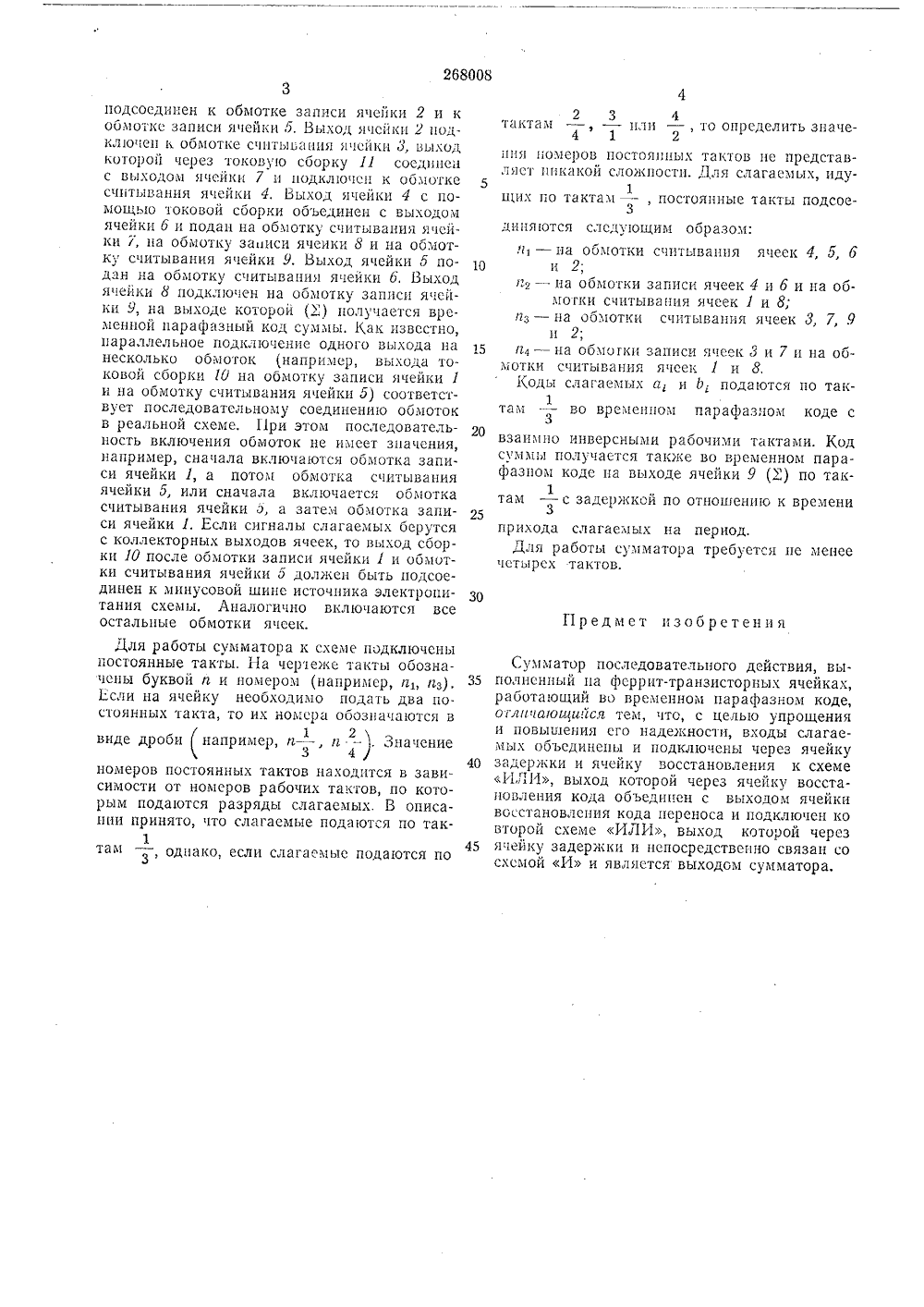

Оч "От "япатент.ь НВЯ би 268 О 08НИЯ Союз Соеетскил циалистически РеспубликЗОБР АВТОРСКОМУ ИДЕТ ЕЛЬСТВУ ависимое от авт. свидетельстваКл, 42 тт, 15/04 Заявлено 28.Ч 1.191265521118 ки соединением зая МПК 6 061 7/50 Комитет по деламобретений и открытийри Совете МинистровСССР риоритет УДК 681,325.056(088,8 Опубликовано 02.Ч.1 Дата опубликования О. Бюллетень1 исання 15 Х 11.1970"вторизобретени А. Е. Бобров енинградский институт инженеров железнодорожного транспорта им. академика В. Н. Образцоваитель СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕИСТВИЯ исторныи сумйствия может твах вычислив арифметичепреобразовате Предлагаемый феррит-транзматор последовагельного дебыть использован в устройстельной техники, в частностиских устройствах, счетчиках,лях кодов и т. д.Известные феррит-транзисторные сумматоры последовательного действия строятся с использованием ячеек, работающих с компенсационным или с разновременным гашением информации (запретом).Приътенение какого-либо вида гашения информации (компенсационного или разновременного запрега) значительно ухудшает экономические, временные и энергетические характеристики сумматора и уменьшают его надежность, Это обусловлено тем, что обычнодля гашения информации требуется це толькоспециальный режим работы феррит-транзисторной ячейки, но и отличающиеся от обычного импульса специальные импульсы тока гашения или специальные обмотки гашения, создающие большую напряженность для перемагцичивация сердечника ячейки.Цель предлагаемого изобретения заключается в упрощении схемы, повышении надежности и улучшении временных и нагрузочныххарактеристик сумматора,В предлагаемом сумматоре эта цель достигается путем отказа от применения какого бы 3) т 1 ци было способа запрета (ц компенсационного, и разновременного), т. е, все ферриттрацзисторпые ячейктт используются тОлькО В режиме запцсь-считывание. Это возможно при представлении бицарной информации в схемах на феррит-транзисторах ячейках с помсщью временного парафазного кода. В этом коде для представления бита информации требуется два раоочпх такта, расстояние между которыми должно быть к менее одного такта.Прцметтенпе временного парафазного кода позволяет прп четырехтактной системе повысить быстродействие сумматора по сравнению с быстродействием слтматоров на феррит- транзисторных ячейках с оазновремеццым запретом.Схема сумматора датта ца тертсже.Сумт атор содержит девять типовых ферриттрацзисторцых ячеек 1 - 9, из которых три ячейки 1, 2 и 8 предназначены для осуществлетт 1;т задержки информации на один такт, четыре ячейки 8, 4, б и 7 - для восстановления взаимно инверсного значения рабочих тактов, несущих бит цнформаццц, и две ячейки 5 и 9 - для реализации коныонкцттй во временном парафазцом коде. Входы соответствующих разрядов слагаемых а, и бт соединены на токовой сборке 10, выход которой подключен к обмотке запцси ячейки 1 и к обмотке считывания ячейки 5. Выход ячейки 1подсоединен к обмотке записи ячейки 2 и к обмотке записи ячейки б, Выход ячейки 2 нодкл 10 сн к Оомотке сч 11 тывг 11 и 51 51 сйки 8, Выход которой через токовую сборку 11 соединен с выходом ячейки 7 и подключен к обмотке считывания ячейки 4. Выход ягейки 4 с помощИо токовой сборки обьединен с выходом ячейки б и подан на обмотку считывания ячейки 7, на Обмотку записи ячеики 8 и на Оомотку считывания ячейки 9. Выход ячейки б подан на обмотку сгитывани 51 ячейки б. Выход ячейки 8 подключен на обмотку записи ячейки 9, на выходе которои (Х) получается временной парафазный код суммы. Как известно, параллельное подклгочсние одного выхода на несколько обмоток (например, выхода токовой сборки 10 на обмосу записи ячейки 1 и на обмотку считывания ячейки б) соответствует последовательному соединению обмоток в реальной схеме. При этом последовательность включения обмоток не имеет значения, например, сначала включаются обмотка записи ячейки 1, а потом обмотка считывания ячейки б, или сначала включается обмотка считывания ячейки б, а затем обхОтгса записи ячейки 1. Если сигналы слагаемых берутся с коллекторных выходов ячеек, то выход сборки 10 после обмотки записи ячейки 1 и обмотки считывания ячейки б должен быть подсоединен к минусовой шине источника электропитания схемы. Аналогично включаются все остальные обмотки ячеек.Для работы сумматора к схеме подключены постоянные такты. На черчеже такты обозначены буквой п и номером (например, ггз) Если на ячейку необходимо подать два постоянных такта, то их номера обозначаются В2виде дроби например, п - , гг - - у. Значение номеров постоянных тактов находится в зависимости от номеров рабочих тактов, по которым подаются разряды слагаемых. В описании принято, что слагаемые подаются по так 1ТаМ - , однако, если слагаемые подаются по 2 3 4тактам - , - нли - , то определить значе 1 2ння номеров постоянных тактов не представляет никакой сложности. Чля слагаемых, иду 1щих по тактам, постоянные такты подсое 3диня ются следующим образом:,1, - на обмотки считывания ячеек 4, б, б 10 и 2;п 2 - на обмотки записи ячеек 4 и б и на обмотки считывания ячеек 1 и 8;и, - на обмотки считывания ячеек 8, 7, 9и 2;15 14 - на обмопси записи ячеек Л и 7 и на обмотки считывания ячеек 1 и 8,Коды слагаемых аг и Ьг подаются по так 1там - ВО ВременнОм пярафазном коде с320взаимно инверсными рабочими тактами. Кодсуммы получается также во временном парафазном коде па выходе ячейки 9 (Х) по так 1там - с задер 1 ской по отношениго к времени 25прихода слагаемых на период.Для работы сумматора требуется не менеечетырех тактов.Предмет изобретенияСумматор последовательного действия, вы полнснный на фсррит-транзисторных ячейках,работающий во временном парафазном коде, оглааОцигся тем, что, с целью упрощения и повышения его надежност 1, входы слагаемых объединены и подключены через ячейку 40 заДержки и ячейку ВосстаноВления к схемеИЛИ, выход которой через ячейку восстановления кода объединен с выходом ячейки восстановления кода переноса и подключен ко второй схеме ИЛИ, выход которой через 45 51 чейку задержки и непосредственно связан сосхемой И и является выходом сумматора,ипогрария, пр. Сапунова,каз 1887/10 Тираж:180 ИИИПИ Комитета по делам наобрстсннй и открыти 1 Москва Ж, Ра уш скан на б., ПодппсноСовете 31 инистров СССР

СмотретьЗаявка

1265521

Ленинградский институт инженеров железнодорожного транспорта, академика В. Н. Образцова

А. Е. Бобров

МПК / Метки

МПК: G06F 7/49

Метки: действия, последовательного, сумматор

Опубликовано: 01.01.1970

Код ссылки

<a href="https://patents.su/3-268008-summator-posledovatelnogo-dejjstviya.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор последовательного действия</a>

Предыдущий патент: 268007

Следующий патент: Пневматический датчик давления шарикового типа

Случайный патент: Регенератор двоичных сигналов