Сумматор параллельного действия на несколько чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 231897

Автор: Кузнецов

Текст

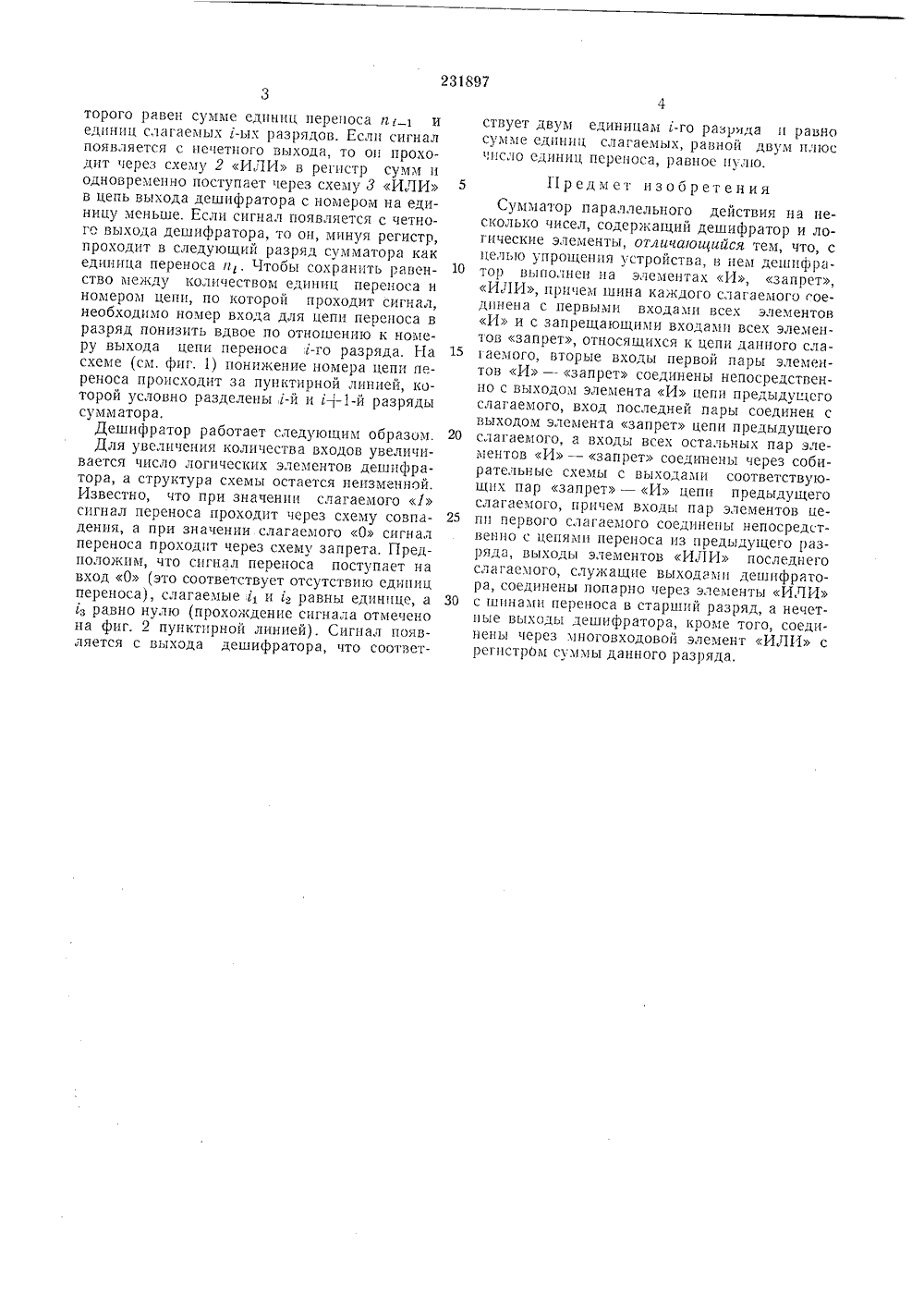

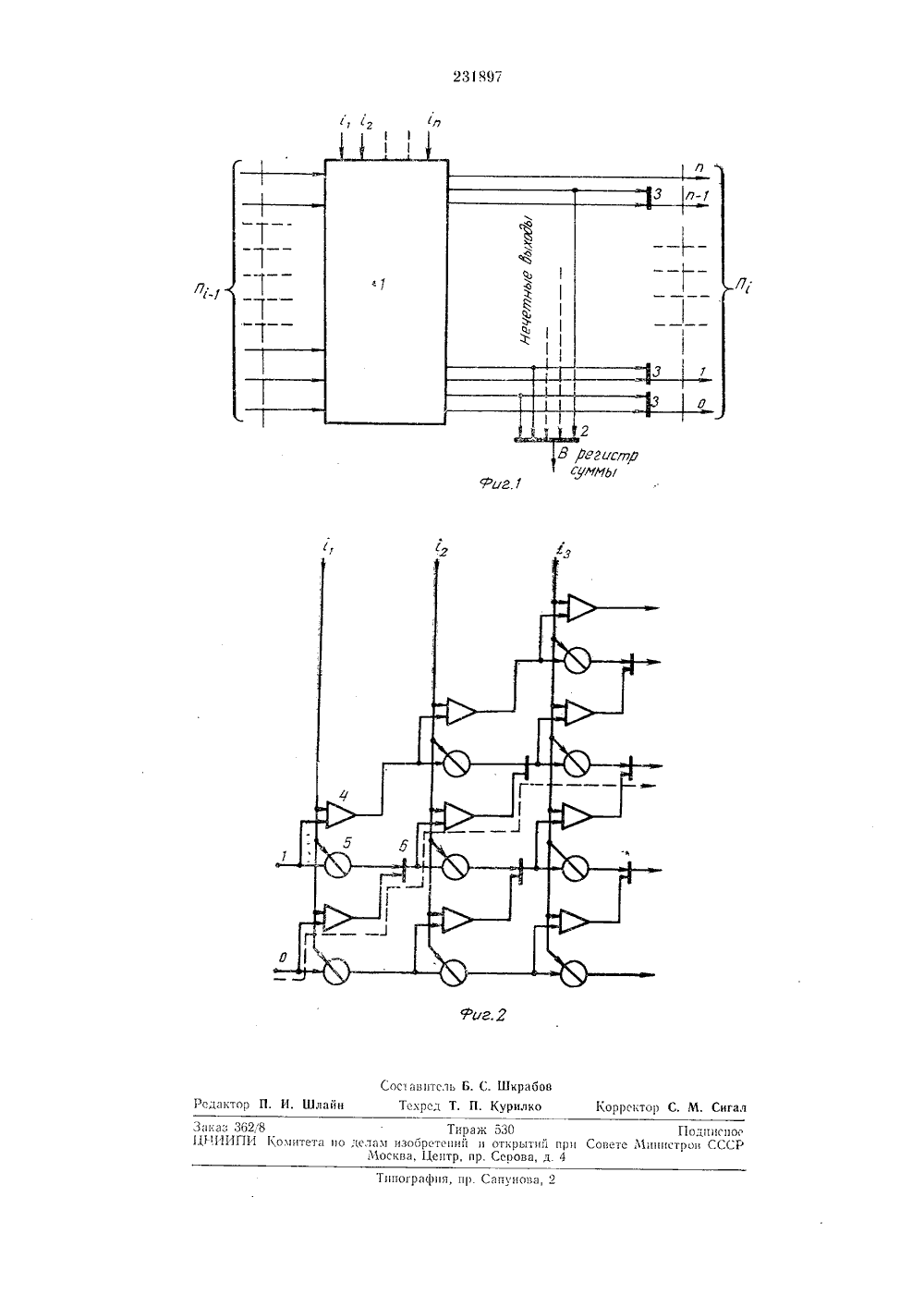

%ФйфюеЬоеооюэйай О П ИСЭН И Е 23)897ИЗОБРЕТЕНИЯ СОюз Советских Социалистических РеспубликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. свидетельства М 1 л. 42 шз) 7/50 аявлено 03,7.11164403/26-2 аявки М с присоединени МПК 6 061ДК 681 325 54(088 8) Приоритет Комитет ел ий и открытий зобрете ри Сов ллетень,с 36 публиковано 28.Х 1,19 МинистровР бликования описания 15 Л.196 Да втор В. И. Кузнецов анский радиотехнический инст:-.1 аявител СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ НА НЕСКОЛЬКО ЧИСЕЛоры па логиче р 1, многонт 3 ИЛИ .ит: элеменэлементы 6 слагаемь чя сумк Известны многочисленные сумм ат раллельного действия, построенные на ских элементах и деиифраторе.Предложенный сумматор параллельного действия на несколько чисел отличается от известных тем, что в нем дешифратор выполнен на элементах И, запрет, ИЛИ. Шина каждого слагаемого соединена с первыми входами всех элементов И и с запрецгаютцими входами всех элементов запрет, относящихся к цепи данного слагаемого. Вторые входы первой пары элементов И - запрет соединены непосредственно с выходом элемента И цепи предыдущего слагаемого. Вход последней пары соединен с выходом элемента запрет пепи предыдущего слагаемого. Входы всех остальных пар элементов И - запрет соединены через собирательные схемы с выходами соответствующих пар запрет - И цепи предыдущего слагаемого. Входы пар элементов цепи первого слагаемого соединены непосредственно с цепями переноса из предыдущего разряда, Выходы элементов ИЛИ последнего слагаемого, служащие выходами дешифратора, соединены попарно через элементы ИЛИ с шинами переноса в старший разряд, а нечетные выходы дешифратора, кроме того, соединены через многовходовой элемент ИЛИ с регистром суммы данного разряда. Предложенный сумматор позволяет сократить время выполнения операций при суммировании большого количества многоразрядныхчисел, ои имеет более простую схему и надежней в эксплуатации по сравненгио с известными устройствами,На фиг. 1 представлена схема -го разрядасумматора; на фиг. 2 - схема дешифратора натри слагаемых и два входа для перенос с10 младшего разряда.Сумматор содержит дешифратовходовой элемент 2 ИЛИ, элемена два входа. Дешифратор содернты 4 И, элементы 5 запрет,15 ИЛ 1:1.Дешифратор 1 имеет входы1 4 , входы от О до и д, тыединиц переноса и т т с младшего разряда ивыходы от О до 2 п суммы единиц слагае 20 мых -ых разрядов и единиц переноса и т т,Для переноса в следующий разряд в сумматоре имеются выходы и от О до п.Предлагаемый сумматор работает следующим образом25 Сигналы иа дешифратор 1 поступают навходы слагаемых 1, 4 1 одновременно,Сигнал переноса подается на дешифратортолько по одному входу, номер которого равенчислу единиц переноса. Сигнал с дешифратора30 появляется только с одного выхода, номер которого равен сумме единиц переноса пги единиц слагаемых -ых разрядов. Если сигнал появляется с нечетного выхода, то оп проходит через схему 2 ИЛИ в регистр сумм и одновременно поступает через схему 3 ИЛИ в цепь выхода дешифратора с номером на единицу меньше. Если сигнал появляется с четного выхода дешифратора, то он, минуя регистр, проходит в следующий разряд сумматора как единица переноса и,. Чтобы сохранить равенство между количеством единиц переноса и номером цепи, по которой проходит сигнал, необходимо номер входа для цепи переноса в разряд понизить вдвое по отношению к номеру выхода цепи переноса,-го разряда. На схеме (см, фиг. 1) понижение номера цепи переноса происходит за пунктирной линией, которой условно разделены -й и +1-й разряды сумматора.Дешифратор работает следующим образом.Для увеличения количества входов увеличивается число логических элементов дешифратора, а структура схемы остается неизменной. Известно, что при значении слагаемого 1 сигнал переноса проходит через схему совпадения, а при значении слагаемого О сигнал переноса проходит через схему запрета. Предположим, что сигнал переноса поступает на вход О (это соответствует отсутствию единиц переноса), слагаемые 1, иравны единице, а , равно нулю (прохождение сигнала отмечено на фиг. 2 пунктирной линией). Сигнал появляется с выхода дешифратора, что соответствует двум единицам -го разряда и равно сумме единиц слагаемых, равной двум плюс число единиц переноса, равное нулю.5 Предмет изобретенияСумматор параллельного действия на несколько чисел, содержащий дешифратор и логические элементы, отличаощийся тем, что, сцелшо упрощения устройства, в нем дешифра 10 тор выполнен на элементах И, запрет,ИЛИ, причем шина каждого слагаемого соединена с первыми входами всех элементовИ и с запрещающими входами всех элементов запрет, относящихся к цепи данного сла 15 чаемого, вторые входы первой пары элементов И - запрет соединены непосредственно с выходом элемента И цепи предыдущегослагаемого, вход последней пары соединен свыходом элемента запрет цепи предыдущего20 слагаемого, а входы всех остальных пар элементов И - запрет соединены через собирательные схемы с выходами соответствующих пар запрет - И цепи предыдущегослагаемого, причем входы пар элементов це 25 пп первого слагаемого соединены непосредственно с цепями переноса из предыдущего разряда, выходы элементов ИЛИ последнегослагаемого, служащие выходамп дешифратора, соединены попарно через элементы ИЛИ30 с шинами переноса в старший разряд, а нечетные выходы дешифратора, кроме того, соединены через многовходовой элемент ИЛИ срегистрОм суммы данного разряда,-1 Сосгавитсль Ь. С. Шкрабов Текрсд Т. П. Курилко Корректор С. М. Сига Редактор П Типография, пр. лпунова,Закан 362,8 ТиражЦИИИПИ Комитета ио делам изобретенийМосква, Центр, пр 530 Поди испо ткрытий при Совете Министров СССР Ссрова, д. 4

СмотретьЗаявка

1164403

В. И. Кузнецов занский радиотехнический институт

МПК / Метки

МПК: G06F 7/50

Метки: действия, параллельного, сумматор, чисел

Опубликовано: 01.01.1968

Код ссылки

<a href="https://patents.su/3-231897-summator-parallelnogo-dejjstviya-na-neskolko-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор параллельного действия на несколько чисел</a>

Предыдущий патент: 231896

Следующий патент: Устройство для контроля параметров объекта

Случайный патент: Логарифмическое вычислительное устройство