Двоично-десятичное суммирующее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

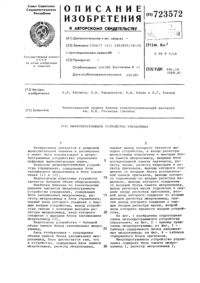

О П И С А Н И Е 22 О 63ИЗОБРЕТЕНИЯ Воюз Советских Социалистических РеспубликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. свидетельстваЗаявлено 03.1 Ч.1967 ( 1146271/26-24с присоединением заявкил. 42 птд, 7/4 МПК 6 061УДК 681.325,55 (088.8 орит Комитет по делам зобрвтвиий и открытий при Совете Министров СССРано 28.Ч 1,1968. Бюллетеньолик Дата опубликования описания 9,1 Х.19 Авторыизобретения оротаев, Е, В, Коновалов Белорусский Государственный университет Заявитель. Ленина ИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТ Двоично-десятичное суммирующее устройство может быть использовано в специализированной и универсальной ЭЦВМ, когда для вычисления используется таблица результатов, записанная в постоянной памяти.Известны двоично-десятичные суммирующие устройства с использованием таблиц результатов.Г 1 редложенное двоично-десятичное суммируютцсе устройство содержит схему управления с формирователями последовательности управляющих сигналов, регистр первого операнда, выполненный по схеме двоично-десятичного реверсивного счетчика, регистр второго операнда, схему коррекции первого операнда с триггером переноса и со схемой модификации по +1 регистра первого операнда и запоминающее устройство, содержащее таблицы сложения - вычитания, и отличается тем, что выход первого формирователя последовательности управляющих сигналов соединен со входом клапана, второй вход которого соединен с единичным выходом триггера переноса, а выход - со входом элемента ИЛИ, второй вход которого соединен через клапан с выходом второго формирователя последовательности и единичным выходом триггера первого двоичного разряда регистра второго операнда. Выход элемента ИЛИ соединен с первыми входами клапанов модификации, вторые входы которых соединены соответственно с выходами источников сигнала Сложение и Вычитание схемы управления, а выходы клапановсоединень 1 соответственно со входами счета по5 +1 и- 1 регистра первого операнда, Выход третьего формирователя последовательности управляющих сигналов соединен с пусковым входом схемы возбуждения адресов запоминающего устройства, входы первого - седь 10 мого разрядов этой схемы соединены соответственно с источником сигнала Вычитание,единичными выходами второго - четвертогоразрядов регистра второго операнда и второго - четвертого разрядов регистра пер 15 вого операнда, Единичные выходы усилителей считывания первого - четвертого разрядов запоминающего устройства соединены через клапаны с единичнымивходами триггеров второго - пятого разрядов20 регистра первого операнда. Каждая четная четырехразрядная ячейка таблицы запоминающего устройства содержит двоично-десятичныйкод результата сложения определенной парыодноразрядных четных десятичных чисел без25 младшего двоичного разряда, а каждая нечетная ячейка - результат вычитания без младшего разряда.Изобретение позволяет сократить объемтаблицы результатов, хранящихся в памяти, и30 тем самым упростить устройство,20 25 30 35 40 50 55 60 65 На чертеже представлена блок-схема описываемого устройства.Устройство содержит схему управления 1, регистр П первого операнда, регистр 1 П второго операнда, схему К коррекции первого операнда и запоминающее устройство Р (регистр П выполнен как пятиразрядный реверсивный десятичный счетчик).Цепи приема операндов в регистры П и П 1 и соединения выходов схемы переноса реверсивного счетчика 1 со входами триггеров 2 - б на чертеже не показаны.Схема работает следующим образом.Перед операцией первое слагаемое (уменьшаемое) принимается в первый - четвертый разряды регистра П, второе слагаемое (вычитаемое) - в регистр 1 П. Сигнал запуска с источника 7 запускает цепочку последовательно включенных элементов задержки 8 - 11, формирующих временную диаграмму устройства, и поступает на клапан 12. Если от предыдущей операции в триггере 13 переноса осталась единица переноса (занять), то сигнал с клапана 12 поступает на гашение триггера 13 и через элемент 14 ИЛИ - на входы клапанов 15 и 1 б.При сложении по сигналу Сложение с источника 17 выполняется добавление +1 в регистр П, при вычитании по сигналу Вычитание с источника 18 выполняется вычитание- .1 из регистра П.Затем происходит коррекция первого опе. ранда по значению первого двоичного разряда второго операнда. Сигнал с выхода элемента задержки 8 через клапан 19 опрашивает триггер 20 первого разряда регистра П 1 и через элемент 14 ИЛИ и один из клапанов 15 или 1 б поступает на вход счета по +1 или- 1 регистра П. Сигнал с выхода элемента задержки 9 поступает на вход схемы 21 возбуждения адресов, формирующей адрес ячейки результата.Перед появлением кода на выходе усилителей считывания 22 - 25 сигнал с выхода элемента задержки 10 гасит содержимое второго - четвертого разрядов регистра 11. Прочитанный код принимается в триггеры 2 - б регистра П через клапаны 2 б - 29 по сигналу с источника 30 сигнала приема результата. В триггер б принимается разряд переноса результата, в триггер 5 - 2 - разряды 8, 4, 2 результата в коде 8421. Первый разряд в коде результата отсутствует, так как при сложении (вычитании) четных чисел этот разряд всегда равен нулю. После приема кода по сигналу с элемента задержки 11 содержимое триггера б (разряд переноса) через клапан 31 заносится в триггер 13 переноса. В разрядах 1 - 4 (триггеры 2 - 5) регистра П оказывается результат в коде 8421, в триггере 13 переноса остается единица переноса (занять), которая учитывается при сложении (вычитании) следующих по весу десятичных разрядов операндов,Принцип работы устройства дополнительно поясняется на примерах. П р и м е р 1, 9+7. От предыдущего сложения осталась единица переноса.До обращения к таблице в регистре первого операнда выполняются следующие действия;а) 9+1==10 (10000), т. е. добавляется единица переноса;б) 10+1 = 11 (10001), т. е. добавляется единица младшего двоичного разряда второго слагаемого (7).При обращении к таблице формируется адрес;000 011 0 признак сложения четвертый, третий, второйразряды второго слагаемого четвертый, третий, второй разрядыпервого слагаемого,В ячейке по этому адресу находится код 0011, т. е. код результата от сложения 0+6=6 (00110) без младшего двоичного разряда. Код из таблицы принимается в предварительно погашенные пятый - второй разряды регистра первого слагаемого, причем пятый разряд регистра перед приемом кода не гасится. Таким образом, после занесения кода 0011 в регистр первого слагаемого, содержащий код 10001, последний будет содержать код 10111, т. е. код результата от сложения 9+7+ единица переноса.П р и м е р 2. 7 - 9. От предыдущего вычитания осталась единица занять.До обращения к таблице в регистре первого операнда выполняются следующие действия:а)- 1=6 (00110), т. е. вычитается единица занять;б) 6 - 1=5 (00101), т. е. вычитается младший двоичный разряд вычитаемого (9),Обращение к таблице происходит по адресу010 100 1 п ризнак вычитаниячетвертый, третий, второйразряды вычитае мого четвертый, третий, второй разрядыум еньшаемого. В этой ячейке находится результат вычитания 4 - 8=16 (10110) без младшего двоичного разряда, т, е. код 1011. Этот код принимается в пятый - второй разряды регистра первого операнда, в результате в этсм регистре устанавливается код 10111, т. е. результат от вычитания 7 - 9 - единица занять.Единица в пятом разряде кода 10111 учитывается при вычитании следующей пары разрядов чисел в качестве единицы занять. Предмет изобретенияДвоично-десятичное суммирующее устройство, содержащее схему управления с форми 220631рователями последовательности управляющих сигналов, регистр первого операнда, выполненный по схеме двоично-десятичного реверсивного счетчика, регистр второго операнда, схему коррекции первого операнда с триггером переноса и со схемой модификации по +1 регистра первого операнда и запоминающее устройство, содержащее таблицы сложения - вычитания, отличающееся тем, что, с целью упрощения устройства, выход первого формирователя последовательности управляющих сигналов соединен со входом клапана, второй вход которого соединен с единичным выходом триггера переноса, а выход соединен со вхо дом элемента ИЛИ, второй вход которого соединен через клапан с выходом второго формирователя последовательности и единичным выходом триггера первого двоичного разряда регистра второго операнда; выход элемента КИЛИ соединен с первыми входами клапанов модификации, вторые входы которых соединены соответственно с выходами источников сигнала Сложение и Вычитание схемы управления, а выходы клапанов соединены соответственно со входами счета по +1 и- 1 регистра первого операнда; выход третьего формирователя последовательности управляющих сигналов соединен с пусковым входом схемы 5 возбуждения адресов запоминающего устройства, входы псрвого - седьмого разрядов этой схемы соединены соответственно с источником сигнала Вычитание, единичными выходами второго в четверто разрядов регистра второ го операнда и второго в четверто разрядоврегистра первого операнда; единичные выходы усилителей считывания первого в четвертого разрядов запоминающего устройства соединены через клапаны с единичными входами 15 триггеров второго - пятого разрядов регистрапервого операнда; каждая четная четырехразрядная ячейка таблицы запоминающего устройства содержит двоично-десятичный код результата сложения определенной пары одно разрядных четных десятичных чисел без младшего двоичного разряда, а каждая нечетная ячейка содержит результат вычитания безмладшего разряда.

СмотретьЗаявка

1146271

Н. А. Коротаев, Е. В. Коновалов, Г.И. Лев Белорусский Государственный университет В.И. Ленина

МПК / Метки

МПК: G06F 7/50

Метки: двоично-десятичное, суммирующее

Опубликовано: 01.01.1968

Код ссылки

<a href="https://patents.su/3-220631-dvoichno-desyatichnoe-summiruyushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Двоично-десятичное суммирующее устройство</a>

Предыдущий патент: Устройство для преобразования г-3, начного двоичного кода в р-значный двоичный код

Следующий патент: Устройство умнож1ения

Случайный патент: Устройство для измерения длительности монохроматических ультракоротких световых импульсов